HOME > TECHNOLOGIES > POWER ELECTRONICS SYSTEMS > FPGA POWER SUPPLY CONSIDERATIONS

# **FPGA Power Supply Considerations**

An examination of the power requirements for FPGAs, offers guidance on how and where to place them on the PCB, and takes the reader step-by-step through a design example involving an FPGA that needs to operate in a system supplied by a 12 V bus, which is the main output from a mains-supplied SMPS.

Owain Bryant, Product Applications Engineer, Vishay Siliconix | Power Electronics Aug. 1, 2013

SHARE Tweet

Recommend 14

COMMENTS 0

An examination of the power requirements for FPGAs, offers guidance on how and where to place them on the PCB, and takes the reader step-by-step through a design example involving an FPGA that needs to operate in a system supplied by a 12 V bus, which is the main output from a mains-supplied SMPS. What is in this article?:

FPGA Power Supply Considerations

Choosing the Right Regulator

**Example of Initial Design Procedure**

The key part of the FPGA design is to determine the voltage requirements needed and the current requirements of each voltage rail. The major FPGA vendors offer comprehensive

#### Advertisement

calculators that take into account the frequency that the part operates at, the number of gates used, as well as the toggle rate of the gates to determine these requirements. For instance, Altera offers the PowerPlay Early Power Estimator and Xilinx offers the XPower Analyzer.

## TABLE 1.80 PLUS CERTIFICATION REQUIREMENTS

|                  | Part<br>number | Logic<br>(Ks) | Core<br>voltage<br>(V) | Core<br>tol.<br>(mV) |                        | Auxiliary<br>Voltages<br>(V)                                                      | IO<br>voltages<br>(V) | IO<br>tol<br>(%) |

|------------------|----------------|---------------|------------------------|----------------------|------------------------|-----------------------------------------------------------------------------------|-----------------------|------------------|

| Altera           |                |               |                        |                      |                        |                                                                                   |                       |                  |

| Stratix V        | 5SEBA          | 1087          | 0.85                   | 30                   | 2.5<br>1.5             | (VCCA_PLL)<br>(VCCD_PLL)                                                          | 1.2 - 3               | 5<br>5           |

| Cyclone IV<br>GX | EP4CGX150      | 150           | 1.2                    | 40                   | 2.5<br>1.2             | (VCCA, VCCA_GXB, VCCH_<br>GXB)<br>(VCCD_PLL,<br>VCC_CLKIN)                        | 1.2 - 3               | 5<br>5           |

| Arria V          | 5AGXB7         | 503           | 1.1                    | 30                   | 2.5                    | (VCC_AUX,<br>VCCA_FPLL, VCCPD)                                                    | 1.2 - 3.3             | 5                |

| Xilinx           |                |               |                        |                      |                        |                                                                                   |                       |                  |

| Virtex 6         | XC6VLX760      | 760           | 1                      | 50                   | 2.5                    | (VCC_AUX)                                                                         | 1.2 - 2.5             | 5                |

| Virtex 6         | XC7V2000T      | 2000          | 1                      | 30                   | 1<br>1.2<br>1.8<br>4.5 | (MGTAVCC, VCCBRAM)<br>(MGTAVTT)<br>(MGTVCCAUX, VCCAUX,<br>VCCAUX_IO)<br>(VCCBRAM) | 1.2 - 1.8             | 5                |

| Spartan 6        | XC6SLS150T     | 147           | 1.2                    | 60                   | 1.2<br>2.5<br>3.3      | (MGTAVCC,<br>MGTAVCCPLL,MGTAVTTRX,<br>MGTAVTTTX)<br>(VCCAUX)                      | 1.2 - 3.3             | 5                |

| Artix 7          | XC7A350T       | 360           | 1                      | 30                   | 1<br>1.2<br>1.8        | (MGTAVCC, VCCBRAM,<br>VCCINT)<br>(MGTAVTT)<br>(MGTVCCAUX, VCCAUX,<br>VCCAUX_IO)   | 1.2 - 3.3             | 5                |

### in The Power Plant

# **Most Read**

- 1. Back-to-Basics On Power Factor And Why We Correct It

- 2. Image Gallery: Top Power Management Semiconductors Q1Q2 2013

- 3. Image Gallery: Top Regulator ICs Q1Q2 2013

- 4. Blog: Graphene Provides Efficient Electronics Cooling

- 5. Reader Q&A of the Month: Steve Sandler Answers Your Questions

Advertisement

## **Related Articles**

- Optimum Dead Time Selection in ZVS Topologies

- Redundant Power Supplies Prevent System Downtime

- Power Management Basics: Power Supply Characteristics

- Turn Your Power Supply's Power Limit into Current Limit

**Table 1** lists some of the typical voltage rails required by Altera and Xilinx devices, broken down into the core voltage, the I/O voltages, the transceiver, and the auxiliary voltages.

FPGAs with lower core voltage needs require high currents, high accuracy, and minimum ripple. In order to achieve this, decoupling capacitors should be placed as close as possible to the FPGA, with minimal ESR and ESL in the decoupling path.

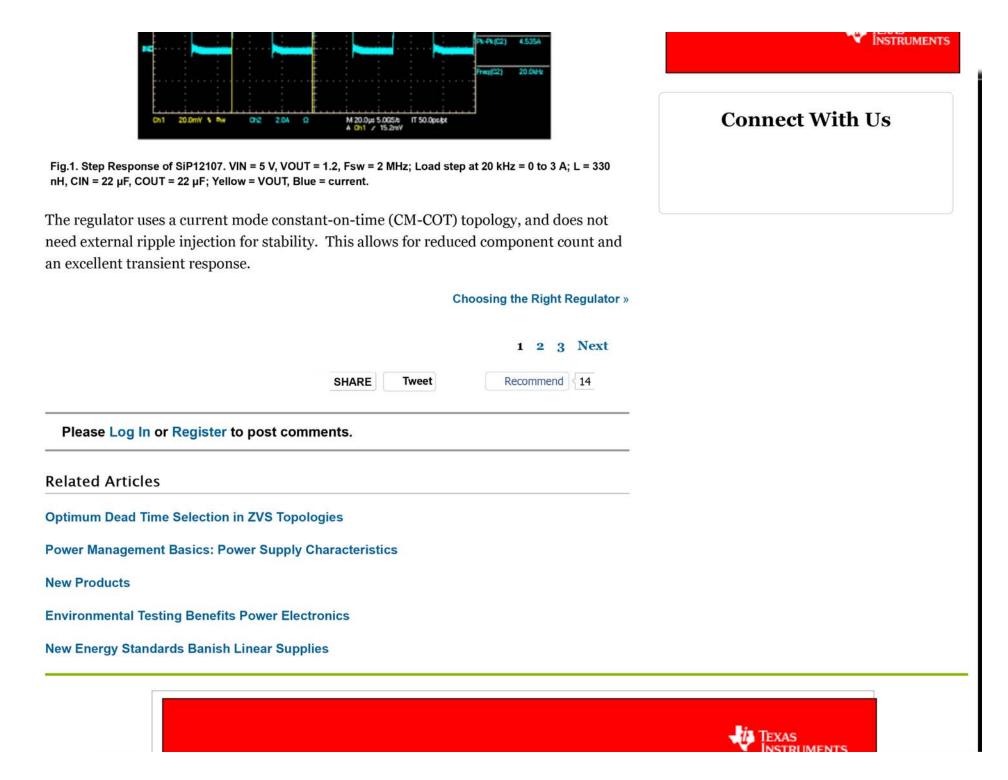

Another desirable practice is to place the POL regulators as near to the part as possible without affecting routing in and out of the FPGA. Higher operating frequencies and the integration of control, drivers and MOSFETs, enable a compact layout. The small solution footprint allows for close placement of the regulators to the FPGA, thus improving regulator transient response. *Fig. 1* provides an example of a 3 A regulator in Vishay's microBUCK® product offering.

The step response, with minimal input and output capacitance of 22  $\mu$ F (0805), can be observed in *Fig. 1* as 37 mV Pk-Pk (the load has some capacitance also).

| New                 | wsletter Signup              |

|---------------------|------------------------------|

| Sign-up t           | o receive our free newslette |

|                     |                              |

| E-MAIL:             |                              |

| E-MAIL:<br>COUNTRY: | UNITED STATES                |

### Advertisement