### **Power MOSFETs**

**Application Note AN845**

# Matching System Dead Time to MOSFET Parameters in ZVS Circuits

#### by Sanjay Havanur

Medium- and high-voltage power MOSFETs are used in a variety of isolated converter topologies, such as half- or full-bridges and single-ended boost and synchronous buck regulators. The bridges may be hard- or soft-switched; however, most of today's converters employ zero voltage switching (ZVS) to eliminate turn-on switching losses. The powertrain remains the same, except the sequence in which devices are turned on and off needs to be modified. Synchronous buck converters, typically used for front end pre-regulation in wide-input DC/DC brick converters, also switch the low-side MOSFET in ZVS mode. While the hard switched bridges and boost converters do not have critical dead time requirements, all soft-switched ZVS bridges and synchronous buck converters must operate within such limits. In low-voltage synchronous buck converters, the dead time during the transitions between the low- and high-side MOSFETs is optimized by the controller or the driver. Shoot-through protection is also implemented, either by sensing the falling edge of the gate drive or the switch node voltage. There are also more sophisticated techniques that attempt to optimally adjust the delay on a continuous basis.

However, such fine tuning is not practical with higher-voltage drivers, so designers must fall back on fixed dead times during transitions. Since long dead times lead to longer body diode conduction and a consequent loss of efficiency, it is always desirable to provide an optimally minimized dead time without running into shoot-through conditions. This requires a detailed understanding of the transition process and calculation of different intervals based on MOSFET and circuit parameters. While optimum delays can be, and quite often are, determined empirically, analysis is necessary to account for variations and to choose the right device for the highest efficiency. For an illustration of this analysis, in this article we will use a soft-switched full bridge, which operates with a full duty ratio of 50 % per arm. Such a topology is also known as a DC transformer, and is popular for generating an unregulated intermediate bus converter (IBC) output from a 48 V<sub>DC</sub> input. The concepts and parametric tradeoffs discussed here can be extended to many other ZVS topologies as well.

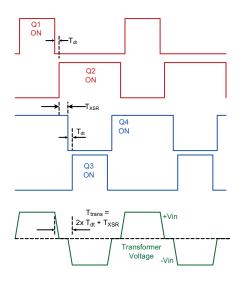

Fig. 1 - Gate drive and transformer voltages in a full-duty ratio bridge

APPLICATION NOT

Д

Vishay Siliconix

### Matching System Dead Time to MOSFET Parameters in ZVS Circuits

#### THE TRANSITION PROCESS

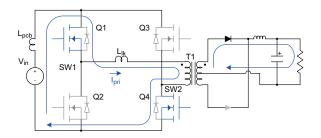

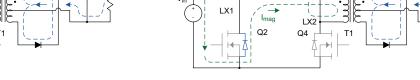

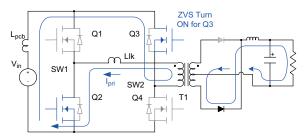

To start with, there are different ways to sequence a soft-switched full bridge, and each has its own benefits and pitfalls. One particular sequence, where each transition is initiated by turning off the high-side MOSFET, is shown in Fig. 1. The flow of current through different devices during the transition is shown in Fig. 2a through Fig. 2e. Initially Q1 and Q4 are conducting and power is delivered to load (Fig. 2a). The transition is initiated by turning off Q1, and its current is diverted to the body diode of Q2 (Fig. 2b). This interval lasts for T<sub>dt</sub>.

Fig. 2a - Q1 and Q4 are conducting

Fig. 2b - Q1 is turned off and current is diverted to Q2

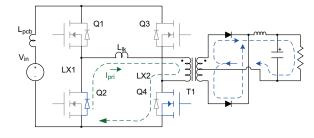

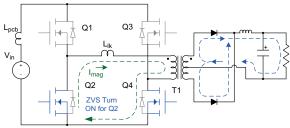

When Q1 is completely off, Q2 is turned on with ZVS. This is followed by a short duration ( $T_{XSR}$ ), during which the transformer primary is shorted out and a magnetizing current circulates between the low-side MOSFETs (Fig. 2c). In phase-shifted bridge converters, output regulation is achieved by varying the  $T_{XSR}$ , but in DC transformers it is kept to a minimum. After the  $T_{XSR}$  delay, Q4 is turned off and the magnetizing current is diverted to Q3 (Fig. 2d). The transition is complete when Q3 is turned on with ZVS after another interval of  $T_{dt}$  (Fig. 2e).

Fig. 2c - Q2 is turned on with ZVS

Fig. 2d - Q4 is turned off and magnetizing current is diverted to Q3

Fig. 2e - Q3 is turned on with ZVS

The total transition time is given by the equation  $T_{trans} = 2 x T_{dt} + T_{XSR}$ .

Document Number: 67527

Vishay Siliconix

### Matching System Dead Time to MOSFET Parameters in ZVS Circuits

The interval  $T_{XSR}$  is not critical to the primary transition; it can be zero in theory. However, a minimum value is demanded by the secondary synchronous rectifier. If output rectifiers are replaced by synchronous MOSFETs, their drive signals must toggle during the  $T_{XSR}$  dead band. This is true whether SSRs are self driven or control driven; the secondary drive pulses are matched to the primary in both cases. The only difference is that in a self-driven scheme,  $T_{XSR}$  needs to be higher since the transformer secondary rise and fall times are much slower. Another factor to consider is that High  $\rightarrow$  Low and Low  $\rightarrow$  High transitions are not symmetric with IC-based gate drivers, which may add a delay during the level shifting of the input signals. This is different from, and in addition to, the normal propagation delay through the drive stages. The level shift delay reduces available dead time even further during  $H \rightarrow L$  transitions, but is actually beneficial during  $L \rightarrow H$  transitions and increases available dead time. Most drivers try to match the total delays within a few nanoseconds, but the difference, denoted as  $T_{LSH}$ , needs to be taken into account.

It is clear that ZVS turn-on is achieved only if, within the available dead time T<sub>dt</sub>,

- a) The gate capacitance of the outgoing MOSFET is discharged to below V<sub>th</sub>, and

- b) The output capacitor of the incoming MOSFET is fully discharged close to zero.

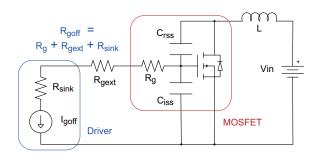

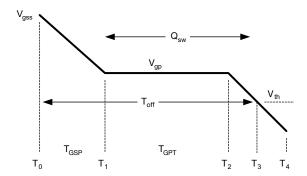

Fig. 3 shows the simplified gate turn-off circuit used in the analysis. Since all capacitances are functions of V<sub>DS</sub>, the equivalent charge specifications will be used in the calculations. There are three distinct stages for the gate discharge, as shown in Fig. 4.

Fig. 3 - Simplified gate drive circuit

Fig. 4 - Gate turn-off voltage and time intervals

- T0 T1: C<sub>iss</sub> is discharged from the gate supply voltage V<sub>GSS</sub> to plateau V<sub>gp</sub>, assuming constant turn-off current. During this interval the I<sub>goff</sub> current is limited by the drive capability rather than gate resistors

- T1 T2: Conventional plateau time where  $V_{DS}$  rises to  $V_{IN}$  and beyond due to ringing. The gate current is now limited by the total resistance in the gate loop

- T2 T3: Current fall time in the outgoing MOSFET

The three intervals can be calculated using the equations:

$$T_{GSP} = C_{iss0} \times \left(\frac{V_{gss} - V_{gp}}{I_{goff}}\right) \\ T_{GPT} = R_{igoff} \times \frac{Q_{sw}}{V_{gp}} \\ R_{goff} = R_g + R_{ext} + R_{sink} + R_{s$$

Vishay Siliconix

## Matching System Dead Time to MOSFET Parameters in ZVS Circuits

The value  $C_{iss0}$  used for  $T_{GSP}$  is not from the datasheet tables, but at  $V_{DS} = 0$  V, when the MOSFET is fully on. For ultra-low  $R_{DS(on)}$  MOSFETs with extremely high cell densities, trench gates, and charge balancing structures,  $C_{iss0}$  can be 4 times to 5 times higher than the  $C_{iss}$  specified at mid voltage. There is no power loss, but this interval can eat up a major part of the available dead time. The formula for  $T_{GPT}$  defines the sum of voltage rise time and current fall time during turn-off based on the drive conditions. But this is an inadequate approximation, since the current fall time depends on a number of external parameters such as PCB trace inductance, the source inductance of the package, and the input voltage. These factors dominate the di/dt of the primary loop current over gate drive. However, the focus here is on achieving zero voltage status for the incoming MOSFET, which may be determined using another approach. As the current in the high-side MOSFET goes to zero, the same is taken up by its complement on the low side. This enables a simple estimate of the time required to discharge the output capacitance as one quarter of one resonant cycle of  $L_{PCB}$  and  $C_{oss}$ ,

$$T_{DSD} = \frac{\pi}{2} \times \sqrt{\frac{L_{PCB} \times Q_{oss}}{V_{IN}}}$$

It is assumed that the PCB trace inductance is much smaller than the leakage inductance  $L_{lk}$ , and during  $T_{DSD}$  the transformer loop current does not change. With this we are in a position to state the complete timing requirement for the dead time  $T_{dt}$ ,

$$T_{dt} \ge T_{LSH} + T_{GSP} + T_{GPT} + T_{DSD}$$

This final result is somewhat conservative for devices with high  $V_{th}$  values. The higher rise time needed before gate voltage can reach  $V_{th}$  adds to the dead time.

#### **TEST RESULTS ON IBC CONVERTER**

0 Z

Z

РР

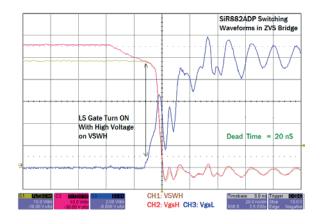

The above analysis was verified with the SiR882ADP high-performance MOSFET targeted for high-frequency DC/DC converters. The relevant specifications of the device are shown in Table 1. The test platform was a 48 V to 9.6 V IBC converter operating at 200 kHz. The original design set the dead time at 20 ns. From the Table 1 values, it is clear that this dead time is quite insufficient.

| TABLE1: DEADTIME CALCULATIONS FOR SIR882ADP |       |              |                    |      |    |  |  |  |

|---------------------------------------------|-------|--------------|--------------------|------|----|--|--|--|

| SiR882ADP                                   |       |              | CIRCUIT PARAMETERS |      |    |  |  |  |

| R <sub>DS(on)</sub>                         | 7.4   | mΩ           | V <sub>IN</sub>    | 48   | V  |  |  |  |

| C <sub>iss</sub>                            | 1975  | pF           | $V_{ges}$          | 10   | V  |  |  |  |

| C <sub>iss0</sub>                           | 4500  |              | I <sub>goff</sub>  | 2    | Α  |  |  |  |

| $Q_{sw}$                                    | 9.8   | nC<br>V<br>Ω | L <sub>PCB</sub>   | 20   | nH |  |  |  |

| Q <sub>oss</sub>                            | 64    |              | R <sub>sink</sub>  | 2    | Ω  |  |  |  |

| $V_{gp}$                                    | 3     |              | R <sub>gext</sub>  | 2    |    |  |  |  |

| $R_g$                                       | 1     |              | R <sub>goff</sub>  | 5    |    |  |  |  |

| T <sub>GSP</sub>                            | 15.75 | - ns         | T <sub>LSH</sub>   | 10   | ns |  |  |  |

| T <sub>GPT</sub>                            | 16.2  |              | T <sub>DSD</sub>   | 8.11 |    |  |  |  |

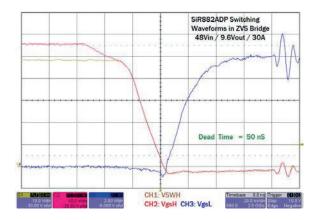

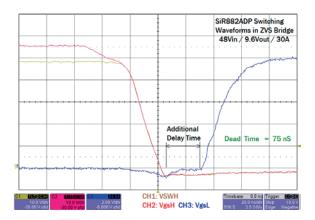

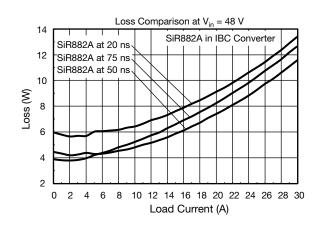

Fig. 5a to Fig. 5c show the switching node waveforms for three different dead times: 50 ns, 75 ns, and 20 ns. Fig. 6 shows the power loss of the entire converter as a function of different dead times. Optimal switching with minimum loss occurs at a dead time of 50 ns, as calculated. At 20 ns, the low-side MOSFET is turned on with the switch node voltage at V<sub>IN</sub>, resulting in shoot-through losses. While the waveforms at 75 ns look clean and offer an extra safety margin, the duration of diode conduction also increases. Fig. 6 shows its impact: diode losses steadily adding up with increasing current.

Revision: 06-Oct-14 Document Number: 67527

Д

# Matching System Dead Time to MOSFET Parameters in ZVS Circuits

Fig. 5a - Switching waveforms at a dead time of 50 ns

Fig. 5b - Switching waveforms at a dead time of 75 ns

Fig. 5c - Switching waveforms at a dead time of 20 ns

Fig. 6 - Total loss as a function of dead time

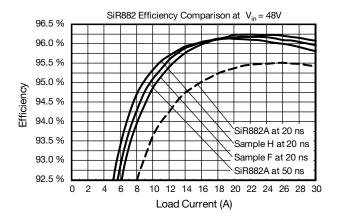

Fig. 7 - System efficiency comparison

Vishay Siliconix

## Matching System Dead Time to MOSFET Parameters in ZVS Circuits

#### **DILIGENCE BEFORE DROP IN**

It is quite common for designers to try out a promising new part in an existing design. It is also equally common to do this by just dropping in the new part in place of the existing one and run an automated efficiency test program. Unfortunately, the results are almost never reliable. As seen above, the power losses are quite dependent on how well the dead time is matched to the device characteristics. Modern trench devices with dense cell structures offer the benefit of very low  $R_{DS(on)}$ , but also come with larger  $C_{iss0}$ ,  $Q_{gd}$ , and  $Q_{oss}$  values. While they offer better figure of merit (FOM) and improved efficiencies, designers need to fine tune their circuits to realize their full potential. Evaluating them by dropping devices into existing circuits, without regard to individual switching characteristics, can lead to misleading results and prevent designers from choosing a better solution to improve overall performance.

This can be further illustrated by comparing three different devices in the same circuit. Table 2 shows the calculated optimum dead times for the SiR882ADP MOSFET against two other samples. Fig. 7 shows the measured efficiency of all devices at different dead times. Sample H was the original device used in the IBC converter with a dead time of 20 ns. It has the highest gate threshold voltage  $V_{th}$  and is more immune to shoot-through even with reduced dead times. Both the lower  $R_{DS(on)}$  devices show worse efficiency simply because they were dropped into a circuit that was not designed for them. With nearly half the  $R_{DS(on)}$ , sample F shows only marginally better efficiency performance; until about 50 % of the load, it is actually worse than the highest  $R_{DS(on)}$  competitor. The SiR882ADP also comes off much worse at 20 ns, but at the optimum value of 50 ns demonstrates its benefits.

| TABLE 2: COMPARISON OF COMPETITIVE DEVICES |          |          |           |      |  |  |  |

|--------------------------------------------|----------|----------|-----------|------|--|--|--|

| MOSFET PART NUMBER                         | SAMPLE H | SAMPLE F | SiR882ADP | UNIT |  |  |  |

| Typical R <sub>DS(on)</sub>                | 12       | 6.3      | 7.2       | mΩ   |  |  |  |

| Calculated Optimum Dead Time               | 38.3     | 38.9     | 50.1      | ns   |  |  |  |

#### **CONCLUSIONS**

Unlike hard-switched converters, ZVS designs like IBC or phase-shifted bridges must work under strict dead time limits during switching transitions. Insufficient dead time during turn off can result in the loss of ZVS, poor efficiency, and in the worst case, failure of the device due to shoot-through. The minimum dead time required varies from one device technology to another, even when they all come from the same manufacturer, but can be easily calculated from the published device parameters. Dead time optimization based on the analysis presented here can help to exploit the advances in device technology and achieve better performance even from legacy designs.

Revision: 06-Oct-14 Document Number: 67527