### Feed-Forward Controller with Primary MOSFET Drivers for Intermediate Bus Converters

### DESCRIPTION

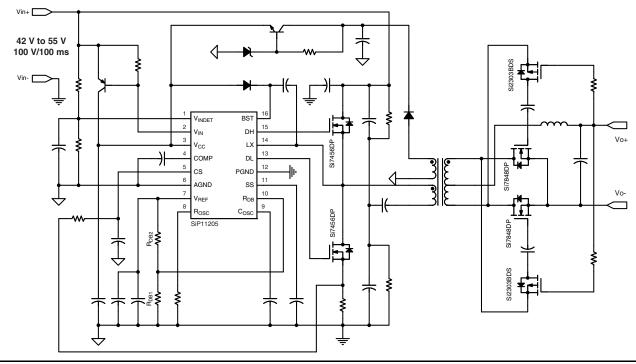

SiP11205 is a feed-forward controller for the primary side of a half-bridge intermediate bus converter (IBC). It is ideally suited for isolated applications such as telecom, data communications and other products requiring an IBC architecture and conversion of standard bus voltages such as 48 V to a lower intermediate voltage, where high efficiency is required at low output voltages (24 V, 12 V, 9 V or 5 V).

Designed to operate within the telecom voltage range of 36 V to 75 V and withstand 100 V transients for a period of 100 ms, the IC is designed for controlling and driving both the low- and high-side switching devices of a half-bridge converter.

The feed-forward feature is designed to make the converter output semi-regulated and is beneficial for point-of-load applications that require narrow input range. SiP11205 has advanced current monitoring and control circuitry, which allows the user to set the maximum current in the primary circuit. This feature acts as protection against overcurrent and output short circuit. Current sensing is by means of a sense resistor connected in series with the primary low-side MOSFET.

### FEATURES

- 36 V to 75 V input voltage range

- Withstand 100 V, 100 ms transient capability

- Integrated ± 1.6 A typical high- and low-side MOSFET drivers

- Oscillator frequency is programmable from 200 kHz to 1 MHz (100 kHz to 500 kHz switching frequency) and can be externally synchronized

- Voltage feed-forward compensation

- High voltage pre-regulator operates during start-up

- Current sensing on primary low-side switch

- Hiccup mode

- System low input voltage detection

- Chip UVLO function

- Programmable soft-start function

- Over temperature protection (160 °C)

- Greater than 95.5 % efficiency for 42 V to 55 V input range

- Better than 2 % line regulation at 9 A

#### APPLICATIONS

- Intermediate bus architectures

- Telecom and Datacom

- Routers and servers

- Storage area network

- Base station

- 1/8 and 1/4 bricks

### **TYPICAL APPLICATION CIRCUIT**

### Vishay Siliconix

### **TECHNICAL DESCRIPTION**

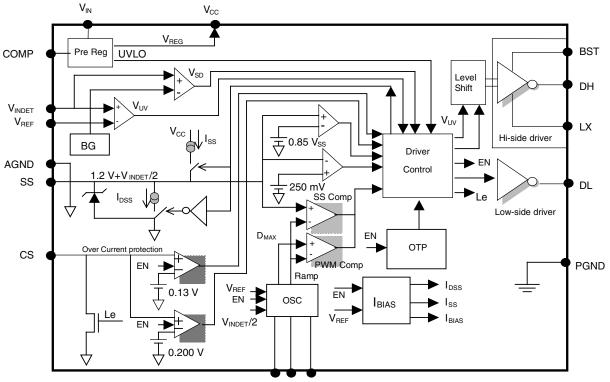

SiP11205 is a feed-forward controller on the primary side of a half-bridge intermediate bus converter. With 100 V depletion mode MOSFET in the chip, the SiP11205 is capable of being powered directly from the high voltage bus to V<sub>CC</sub> through an external PNP pass transistor, or may be powered by an external supply directly to the V<sub>CC</sub> pin.

Without the use of an external pass transistor, failure of the converter output to power  $V_{CC}$  above the  $V_{REG}$  level will result in over temperature protection activating hiccup

### SIP11205 BLOCK DIAGRAM

operation whenever the pre-regulator power dissipation becomes excessive.

The external high- and low-side N-Channel power MOSFETs are driven by a built-in driver with  $\pm$  1.6 A peak current capability. SiP11205 is available in the MLP44-16 PowerPAK<sup>®</sup> package and TSSOP-16 PowerPAK<sup>®</sup> package and is specified over the ambient temperature range of -40 °C to 85 °C.

ROSC RDB COSC

| ABSOLUTE MAXIMUM P                  | RATINGS all voltages referenced to G | ND = 0 V                       |       |

|-------------------------------------|--------------------------------------|--------------------------------|-------|

| Parameter                           |                                      | Limit                          | Unit  |

| March March                         | Continuous                           | 80                             |       |

| V <sub>IN</sub> , V <sub>LX</sub>   | 100 ms                               | 100                            |       |

| V <sub>CC</sub>                     |                                      | 14.5                           |       |

| V <sub>BST</sub>                    | Continuous                           | 95                             | v     |

|                                     | 100 ms                               | 112                            | v     |

| V <sub>BST -</sub> V <sub>LX</sub>  |                                      | 15                             |       |

| Logic Inputs                        |                                      | - 0.3 to V <sub>CC</sub> + 0.3 |       |

| Linear Inputs                       |                                      | - 0.3 to V <sub>CC</sub> + 0.3 |       |

| HV Pre-Regulator Input Current (cor | ntinuous)                            | 10                             | mA    |

| Storage Temperature                 |                                      | - 65 to 150                    | °C    |

| Maximum Junction Temperature        |                                      | 150                            |       |

| Power Dissipation                   | PowerPAK MLP44-16 <sup>a, b</sup>    | 2564                           | mW    |

| Fower Dissipation                   | PowerPAK TSSOP-16 <sup>a, c</sup>    | 2630                           | 11100 |

| Thermal Impedance ( $\Theta_{IA}$ ) | PowerPAK MLP44-16 <sup>a, b</sup>    | 39                             | °C/W  |

|                                     | PowerPAK TSSOP-16 <sup>a, c</sup>    | 38                             | -0/00 |

Notes:

a. Device Mounted with all leads soldered or welded to PC board.

b. Derate 25.6 mW/°C above 25 °C.

c. Derate 26.3 mW/°C above 25 °C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| <b>RECOMMENDED OPERATING RANGE</b> all voltages referenced to GND = 0 V |            |                                                  |            |  |  |

|-------------------------------------------------------------------------|------------|--------------------------------------------------|------------|--|--|

| Parameter                                                               |            | Limit                                            | Unit       |  |  |

| V <sub>IN</sub>                                                         | Continuous | 36 to 75                                         |            |  |  |

| V IN                                                                    | 100 ms     | 100                                              |            |  |  |

| V <sub>BST</sub>                                                        | ·          | V <sub>IN</sub> + 10.5 to V <sub>IN</sub> + 13.2 |            |  |  |

| V <sub>BST</sub> - V <sub>LX</sub>                                      |            | 10.5 to 13.2                                     | V          |  |  |

| V <sub>CC</sub>                                                         |            | 10.5 to 13.2                                     |            |  |  |

| Logic Inputs                                                            |            | - 0.3 to V <sub>CC</sub> + 0.3                   |            |  |  |

| Linear Inputs                                                           |            | - 0.3 to V <sub>CC</sub> + 0.3                   |            |  |  |

| F <sub>OSC</sub>                                                        |            | 200 to 1000                                      | kHz        |  |  |

| R <sub>OSC</sub>                                                        |            | 40 to 200                                        | kΩ         |  |  |

| C <sub>OSC</sub>                                                        |            | 100 to 220                                       | pF         |  |  |

| C <sub>SS</sub>                                                         |            | 10 to 100                                        | ~ <b>Г</b> |  |  |

| C <sub>COMP</sub>                                                       |            | 2.2                                              | – nF       |  |  |

| V <sub>REF</sub> Capacitor to GND                                       |            | 1                                                |            |  |  |

| C <sub>BOOST</sub>                                                      |            | 0.1                                              | μF         |  |  |

| V <sub>CC</sub> Capacitor to GND                                        |            | 4.7                                              | 7          |  |  |

# Vishay Siliconix

| SPECIFICATIONS                               |                                     |                                                                                                                      |      |        |      |            |

|----------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|--------|------|------------|

|                                              |                                     | Test Conditions                                                                                                      |      | Limits |      |            |

|                                              |                                     | Unless Otherwise Specified<br>$T_A = -40 ^\circ\text{C} \text{ to } + 85 ^\circ\text{C}, F_{OSC} = 800 \text{ kHz},$ |      |        |      |            |

|                                              |                                     | $10.5 \text{ V} \le \text{V}_{CC} \le 13.2 \text{ V}, \text{V}_{INDET} = 4.8 \text{ V},$                             |      |        |      |            |

|                                              |                                     | $V_{IN} = 48 \text{ V}, \text{ R}_{DB1} = 47.5 \text{ k}\Omega, \text{ R}_{DB2} = 28.7 \text{ k}\Omega,$             |      |        |      |            |

| Parameter                                    | Symbol                              | $R_{OSC}$ = 47.5 kΩ, $C_{OSC}$ = 100 pF                                                                              | Min. | Тур.   | Max. | Unit       |

| Pre-Regulator                                |                                     |                                                                                                                      | -    | -      |      |            |

| V <sub>IN</sub> Range                        | V <sub>IN</sub>                     |                                                                                                                      | 36   | 48     | 75   | V          |

| Pre-Reg Current (cut-off)                    | I <sub>VINLKG</sub>                 | $V_{IN} = 75 \text{ V}, \text{ V}_{CC} > 10.5 \text{ V}$                                                             |      |        | 10   | μA         |

| Pre-Reg Current (standby)                    | I <sub>VINSD</sub>                  | $V_{IN} = 75 \text{ V}, V_{INDET} = 0 \text{ V}$                                                                     |      | 90     | 200  | μ          |

| Pre-Reg Current (switching)                  | I <sub>VIN</sub>                    | V <sub>IN</sub> = 75 V, V <sub>INDET</sub> = 7.5 V                                                                   | 3.6  | 6.2    | 9    | mA         |

| Pre-Reg Output Voltage                       | V <sub>REG</sub>                    | $V_{CC}$ Voltage with $V_{IN} = 48$ V                                                                                | 7.8  | 9.3    | 10.4 | V          |

| Pre-Reg Drive Current                        | ISTART                              | V <sub>CC</sub> < V <sub>REG</sub>                                                                                   | 20   |        |      | mA         |

| Pre-Reg Load Regulation                      | LDR                                 | I <sub>LOAD</sub> : 0 to 20 mA                                                                                       |      | 100    |      | mV         |

| Pre-Reg Line Regulation                      | LNR                                 |                                                                                                                      |      | 0.05   |      | %/V        |

| Pagulator Componentian                       | I <sub>SRC</sub>                    | V <sub>CC</sub> = 12 V                                                                                               | - 35 | - 20   | - 10 |            |

| Regulator Compensation                       | I <sub>SNK</sub>                    | $v_{CC} = 12 v$                                                                                                      | 40   | 87     | 130  | μA         |

| V <sub>CC</sub> Supply Voltage               |                                     |                                                                                                                      |      |        |      |            |

| V <sub>CC</sub> Range                        | V <sub>CC</sub>                     |                                                                                                                      | 10.5 | 12     | 13.2 | V          |

| Shut Down Current                            | I <sub>SD</sub>                     | V <sub>INDET</sub> = 0 V                                                                                             | 50   | 150    | 350  | μA         |

| Quiescent Current                            | Ι <sub>Q</sub>                      | V <sub>INDET</sub> < V <sub>REF</sub>                                                                                | 3.0  | 4      | 5.2  |            |

| Supply Current                               | I <sub>CC</sub>                     | V <sub>INDET</sub> > V <sub>REF</sub>                                                                                | 5.0  | 6.6    | 8.5  | mA         |

| UVLO OFF-Threshold                           | UVLO <sub>H</sub>                   | V <sub>CC</sub> rising                                                                                               | 7.6  | 9.0    | 10   |            |

| Hysteresis                                   | H <sub>UVLO</sub>                   |                                                                                                                      |      | 1.2    |      | v          |

| V <sub>CC</sub> Clamp Voltage                | V <sub>CLAMP</sub>                  | Force 20 mA into V <sub>CC</sub>                                                                                     | 14   | 15.3   | 16.2 |            |

| Current Sense                                | 02/1111                             |                                                                                                                      |      |        |      | ·          |

| Current Limit Threshold 1 (MOC) <sup>a</sup> | V <sub>MOC</sub>                    | I <sub>SS</sub> = 20 μA                                                                                              | 105  | 130    | 160  |            |

| Current Limit Threshold 2 (SOC) <sup>b</sup> | V <sub>SOC</sub>                    | I <sub>SS</sub> = 400 nA                                                                                             | 165  | 200    | 235  | mV         |

| CS to DL Delay                               | T <sub>D</sub>                      |                                                                                                                      |      | 150    |      |            |

| Leading Edge Blanking Period                 | T <sub>BL</sub>                     | DL <sub>(ON)</sub> blanking time                                                                                     |      | 20     |      | ns         |

| Pulse Width Modulator                        | DL                                  |                                                                                                                      |      |        |      | L          |

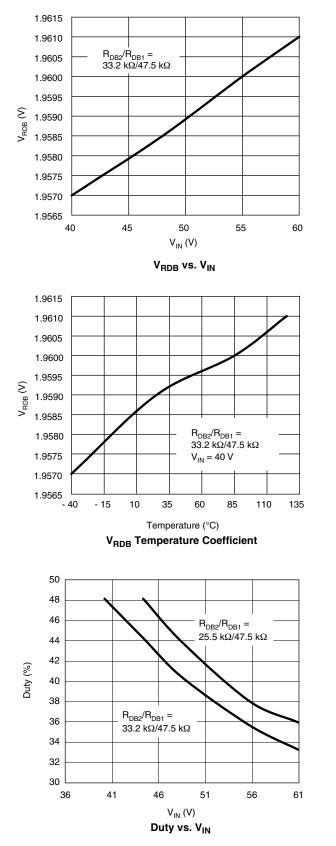

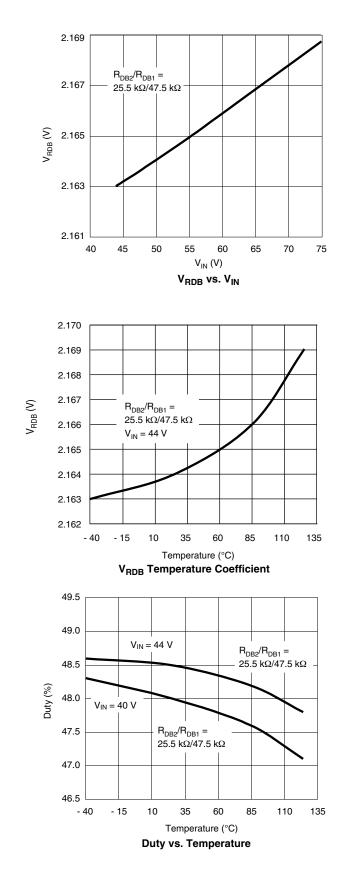

| Maximum Duty Cycle <sup>c</sup>              | D <sub>MAX</sub>                    | V <sub>IN</sub> = 42 V, V <sub>INDET</sub> = 4.2 V                                                                   | 1    | 47     | 50   |            |

| Maximum Duty Cycle Asymmetry                 | WIEW                                |                                                                                                                      |      | 1      |      | %          |

| R <sub>DB</sub> Voltage                      | V <sub>RDB</sub>                    | V <sub>IN</sub> = 42 V, V <sub>INDET</sub> = 4.2 V                                                                   |      | 2.06   |      | V          |

| Oscillator                                   | nee                                 |                                                                                                                      |      |        |      | ι <u> </u> |

| Oscillator Frequency <sup>d</sup>            | F <sub>OSC</sub>                    |                                                                                                                      | 680  | 800    | 920  | kHz        |

| Oscillator Bias Voltage                      | V <sub>ROSC</sub>                   |                                                                                                                      |      | 2.36   |      | V          |

| Soft Start                                   |                                     |                                                                                                                      |      |        |      | ι <u> </u> |

| Soft Start Charging Current                  | I <sub>SS</sub>                     | V <sub>SS</sub> = 0                                                                                                  | - 26 | - 20   | - 14 | μA         |

| SS Ramp Completion Voltage                   | V <sub>SS</sub>                     |                                                                                                                      |      | 4.5    |      | V          |

| MOC Discharge Current                        | I <sub>DSS1</sub>                   | CS = V <sub>MOC</sub>                                                                                                | 14   | 20     | 26   | μA         |

| SOC Discharge Current                        | I <sub>DSS2</sub>                   | $CS = V_{SOC}$                                                                                                       |      | 400    |      | nA         |

| Reset Voltage                                | V <sub>SSL</sub>                    | CS < V <sub>MOC</sub>                                                                                                |      | 0.25   |      | V          |

| Reference                                    | • 55L                               |                                                                                                                      |      | 0.20   |      | v          |

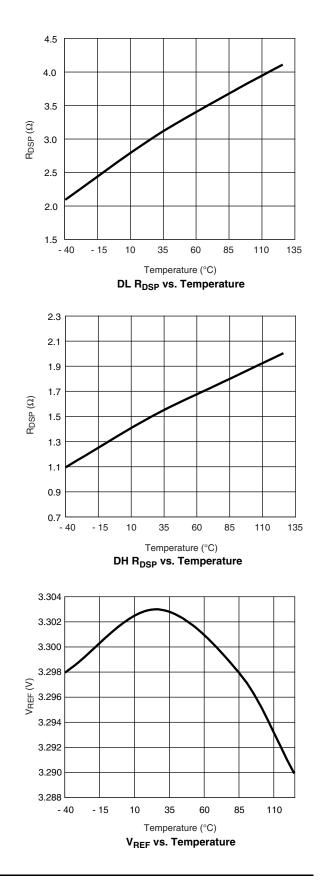

| Output Voltage                               | V <sub>REF</sub>                    | V <sub>CC</sub> = 12 V                                                                                               | 3.2  | 3.3    | 3.4  | v          |

| Short Circuit Current                        | I <sub>REFSC</sub>                  | $V_{\text{BEF}} = 0 \text{ V}$                                                                                       | - 50 | - 42   | 0.7  | mA         |

| Load Regulation                              | $\Delta V_{\rm R}/\Delta I_{\rm R}$ | $0 \text{ mA} \le I_{\text{LOAD}} \le 2.5 \text{ mA}$                                                                | - 33 | - 42   |      | mV         |

|                                              | <u>∽v</u> K⁄ ∽iR                    |                                                                                                                      | - 33 | - 10   |      | 1117       |

## Vishay Siliconix

| SPECIFICATIONS                     |                     |                                                                                                                   | 1     |        |       |     |

|------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------|-------|--------|-------|-----|

|                                    |                     | Test Conditions<br>Unless Otherwise Specified<br>T <sub>A</sub> = - 40 °C to + 85 °C, F <sub>OSC</sub> = 800 kHz, |       | Limits |       |     |

| Parameter                          | Symbol              |                                                                                                                   | Min.  | Тур.   | Max.  | Uni |

| V <sub>INDET</sub> Function        |                     |                                                                                                                   | •     |        | •     |     |

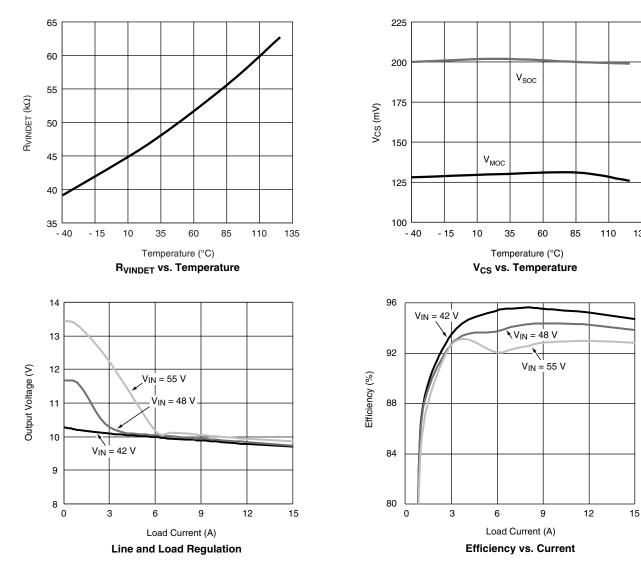

| VINDET Pin Input Impedance         | R <sub>VINDET</sub> |                                                                                                                   | 30    | 46     | 70    | kΩ  |

| Shutdown Threshold High Voltage    | V <sub>SDH</sub>    | V <sub>INDET</sub> rising, V <sub>REF</sub> on                                                                    | 0.33  | 0.58   | 0.76  |     |

| Shutdown Hysteresis Voltage        | H <sub>SD</sub>     | H <sub>SD</sub>                                                                                                   |       | 0.15   |       | v   |

| Under Voltage OFF Voltage          | V <sub>UVH</sub>    | V <sub>INDET</sub> rising at I <sub>CC</sub>                                                                      | 3.14  | 3.3    | 3.46  | v   |

| Under Voltage Hysteresis Voltage   | H <sub>UV</sub>     |                                                                                                                   |       | 0.26   |       |     |

| Over Temperature Protection (01    | [P)                 |                                                                                                                   |       | •      |       | •   |

| Activating Temperature             | OTP <sub>ON</sub>   | T <sub>J</sub> rising                                                                                             |       | 160    |       | °C  |

| De-Activating Temperature          | OTP <sub>OFF</sub>  | T <sub>J</sub> falling                                                                                            |       | 145    |       |     |

| High-Side MOSFET Driver (DH O      | utput)              |                                                                                                                   |       | •      | •     |     |

| Output High Voltage (differential) | V <sub>DHH</sub>    | V <sub>DHH</sub> Sourcing 10 mA, V <sub>DH</sub> - V <sub>BST</sub>                                               |       |        |       | v   |

| Output Low Voltage (differential)  | V <sub>DHL</sub>    | Sinking 10 mA, V <sub>DH</sub> -V <sub>LX</sub>                                                                   |       |        | 0.3   | v   |

| Peak Output Sourcing Current       | I <sub>DHH</sub>    | V <sub>CC</sub> = 10.5 V, C <sub>LOAD</sub> = 3 nF                                                                |       | - 2.2  |       | A   |

| Peak Output Sinking Current        | I <sub>DHL</sub>    | $V_{CC} = 10.3$ V, $O_{LOAD} = 3$ M                                                                               |       | 1.6    |       |     |

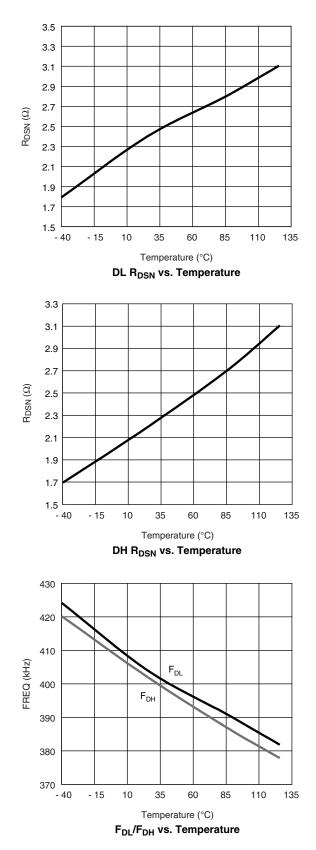

| Driver Frequency                   | F <sub>DH</sub>     |                                                                                                                   | 340   | 400    | 460   | kH  |

| Rise Time                          | t <sub>HR</sub>     | C <sub>LOAD</sub> = 3 nF                                                                                          |       | 20     |       |     |

| Fall Time                          | t <sub>HF</sub>     | C <sub>LOAD</sub> = 3 nF                                                                                          |       | 20     |       | ns  |

| Boost Pin Current (switching)      | I <sub>BST</sub>    | V _ 75 V V _ V _ V                                                                                                | 1.3   | 2.6    | 3.9   |     |

| LX Pin Current (switching)         | I <sub>LX</sub>     | $V_{LX} = 75 V$ , $V_{BST} = V_{LX} + V_{CC}$                                                                     | - 2.1 | - 1.4  | - 0.7 | m/  |

| LX Pin Leakage Current             | I <sub>LX-LKG</sub> | $V_{INDET} = 0 V, V_{LX} = 40 V$                                                                                  |       |        | 10    | μA  |

| Low-Side MOSFET Driver (DL Ou      | itput)              |                                                                                                                   | •     |        |       |     |

| Output High Voltage (differential) | V <sub>DLH</sub>    | Sourcing 10 mA, V <sub>DL</sub> - V <sub>CC</sub>                                                                 | - 0.3 |        |       | v   |

| Output Low Voltage (differential)  | V <sub>DLL</sub>    | Sinking 10 mA, V <sub>DL</sub> - V <sub>AGND</sub>                                                                |       |        | 0.3   | ľ   |

| Peak Output Sourcing Current       | I <sub>DLH</sub>    | V <sub>CC</sub> = 10.5 V, C <sub>LOAD</sub> = 3 nF                                                                |       | - 1.6  |       | •   |

| Peak Output Sinking Current        | I <sub>DLL</sub>    | $v_{CC} = 10.5 v$ , $O_{LOAD} = 5 HF$                                                                             |       | 1.6    |       | A   |

| Driver Frequency                   | F <sub>DL</sub>     |                                                                                                                   | 340   | 400    | 460   | kH  |

| Rise Time                          | t <sub>LR</sub>     | C <sub>LOAD</sub> = 3 nF                                                                                          |       | 20     |       |     |

| Fall Time                          | t <sub>LF</sub>     | C <sub>LOAD</sub> = 3 nF                                                                                          |       | 20     |       | ns  |

Notes:

a. MOC stands for moderate overcurrent voltage at CS pin. b. SOC stands for severe overcurrent voltage at CS pin.

c. The maximum duty cycle is set by the resistor ratio ( $R_{DB1}/R_{DB2}$ ) from pin  $R_{DB}$  to  $V_{REF}$  at minimum  $V_{IN}$  = 42 V. d. Not tested. Guaranteed by driver frequency test. The driver frequency is half of the oscillator frequency.

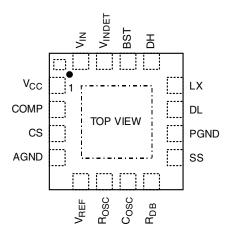

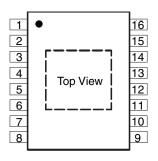

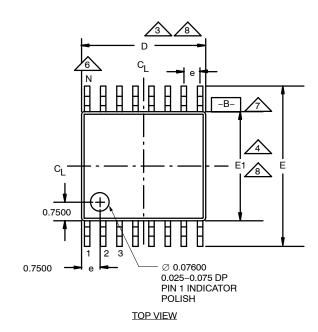

### PACKAGE AND PIN CONFIGURATION

#### MLP44-16 PowerPAK Package

#### **TSSOP-16 PowerPAK Package**

#### Notes:

For MLP44-16 package the bottom pin 1 indicator is connected to EPAD or AGND.

| TSSOP-16 | MLP44-16 | Symbol           | Description                                                             |

|----------|----------|------------------|-------------------------------------------------------------------------|

| 3        | 1        | V <sub>CC</sub>  | Pre-regulator output and supply voltage for internal circuitry          |

| 4        | 2        | COMP             | Pre-regulator compensation pin                                          |

| 5        | 3        | CS               | Current sense comparator input                                          |

| 6        | 4        | AGND             | Analog ground (connected to package's exposed pad)                      |

| 7        | 5        | V <sub>REF</sub> | 3.3 V reference output and bypass capacitor connection pin              |

| 8        | 6        | R <sub>OSC</sub> | Oscillator resistor connection                                          |

| 9        | 7        | C <sub>OSC</sub> | Oscillator capacitor connection and external frequency sync. connection |

| 10       | 8        | R <sub>DB</sub>  | Dead time setting resistor connection                                   |

| 11       | 9        | SS               | Soft start capacitor connection                                         |

| 12       | 10       | PGND             | Power ground                                                            |

| 13       | 11       | DL               | Primary low-side MOSFET drive signal                                    |

| 14       | 12       | LX               | High-side MOSFET source and transformer connection node                 |

| 15       | 13       | DH               | Primary high-side MOSFET drive signal                                   |

| 16       | 14       | BST              | Bootstrap voltage pin for the high-side driver                          |

| 1        | 15       | VINDET           | Shut down/under voltage/enable control pin                              |

| 2        | 16       | V <sub>IN</sub>  | High voltage pre-regulator input                                        |

| ORDERING INFORMATION |          |         |                    |  |  |

|----------------------|----------|---------|--------------------|--|--|

| Part Number          | Package  | Marking | Temperature        |  |  |

| SiP11205DQP-T1-E3    | TSSOP-16 | 11205   | - 40 °C to + 85 °C |  |  |

| SiP11205DLP-T1-E3    | MLP44-16 | 11203   | - 40 C 10 + 85 C   |  |  |

SiP11205 Vishay Siliconix

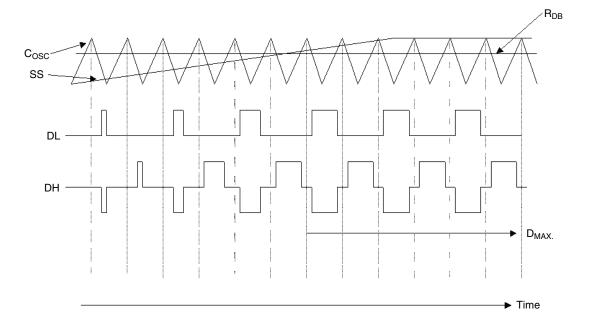

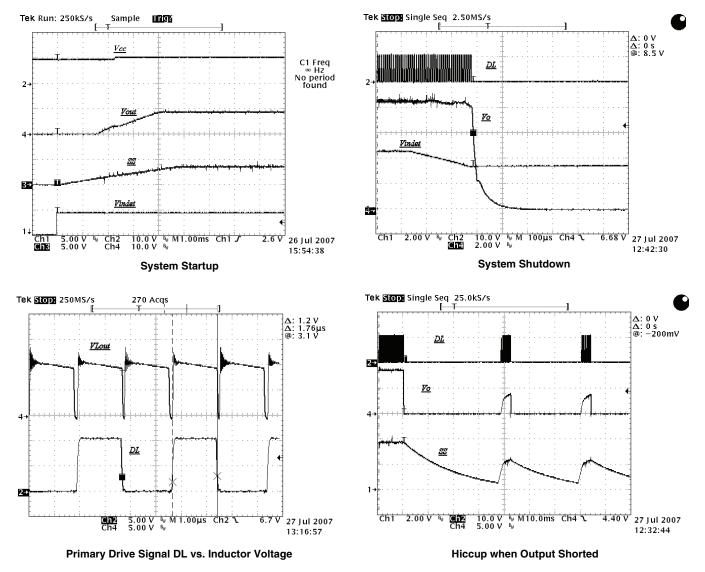

### TIMING DIAGRAM AND SOFT START DUTY CYCLE CONTROL

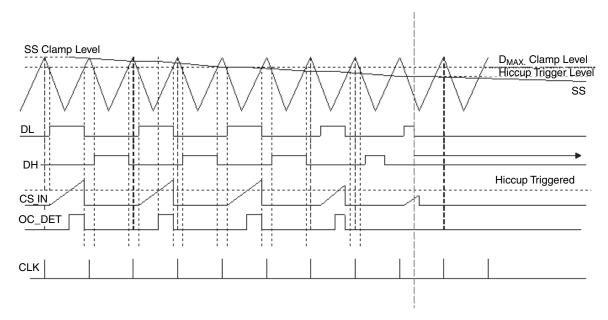

### HICCUP RESPONSE TO MODERATE OVERCURRENT FAULTS

Over current protection operation showing reduction in duty cycle down to the hiccup trigger point. SS continues to discharge down to 250 mV (400 nA  $I_{DISCHARGE}$ ), and then will recharge at 20  $\mu$ A.

Vishay Siliconix

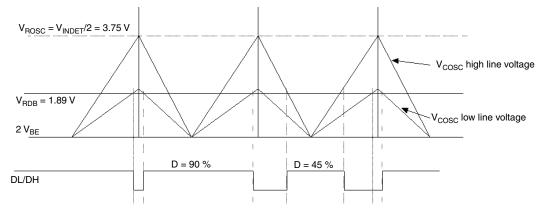

### FEED-FORWARD FUNCTION DIAGRAM

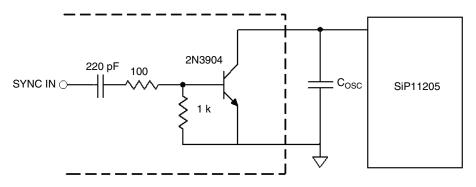

### **CIRCUIT FOR FREQUENCY SYNCHRONIZATION**

### **DETAILED OPERATIONAL DESCRIPTION**

#### Start Up

The controller supply (V<sub>CC</sub>) is linearly regulated up to its target voltage V<sub>REG</sub> by the on chip pre-regulator circuit. During power up with VINDET ramping up from GND, the VCC capacitor minimum charge current is 20 mA and the pre-regulator voltage is typically 9.3 V. As VINDET exceeds V<sub>REF</sub>, the DL/DH outputs are capable of driving 3 nF MOSFET gate capacitances and hence the pre-regulator load regulation can easily handle 120 µA to 20 mA load step with a typical load regulation of 1 %. Startup current into the external V<sub>CC</sub> capacitor is limited to typically 20 mA by the internal N-Channel DMOS in the pre-regulator unless an external power source is connected to V<sub>CC</sub> pin. This source may be a DC supply or from external  $V_{IN}$  by connecting a PNP pass transistor between  $V_{\text{IN}}$  and  $V_{\text{CC}}.$  The  $V_{\text{CC}}$  pin is protected by a 20 mA clamp when this pin exceeds 14.5 V. The clamp turns on when  $V_{CC}$  is between 14.5 and 16 V. When V<sub>CC</sub> exceeds the UVLO voltage (UVLO<sub>H</sub>) a soft start cycle of the switch mode supply is initiated. The V<sub>CC</sub> supply continues to be charged by the pre-regulator until  $V_{CC}$  equals V<sub>REG</sub>. During this period, between UVLO<sub>H</sub> and V<sub>REG</sub>, excessive load may result in V<sub>CC</sub> falling below UVLO<sub>H</sub> and

stopping switch mode operation. This situation is avoided by the hysteresis between  $\rm V_{REG}$  and UVLO Off-Threshold level UVLO\_L.

### **PWM Operation**

During startup, DL always turns on before DH and both switch on and off at half the oscillator frequency. The SS comparator compares the SS ramp with the oscillator ramp hence the duty cycle increases as  $V_{SS}$  increases. When SS ramp reaches a voltage that equals to  $R_{DB}$  voltage, the PWM comparator, which compares  $R_{DB}$  voltage to the oscillator ramp, takes over and the maximum duty cycle is now set by the oscillator ramp and  $R_{DB}$  voltage. Refer to "Timing diagram and soft start duty cycle control" graph for better understanding. After soft start completion the duty cycle is modulated by the feed-forward voltage  $V_{FF} = V_{ROSC} = V_{INDET}/2$ . Since the oscillator frequency is fixed, the ramp amplitude must increase to reduce the duty cycle set by  $R_{DB}$ . Mathematically, the total duty cycle is determined by the following formula:

$\begin{array}{l} \mathsf{D}_{\mathsf{TOTAL}} = \\ \mathsf{V}_{\mathsf{RDB}}/(\mathsf{V}_{\mathsf{INDET}}/2) = 2 \ x \ \mathsf{V}_{\mathsf{REF}} \ x \ \mathsf{R}_{\mathsf{DB1}}/(\mathsf{R}_{\mathsf{DB1}} + \mathsf{R}_{\mathsf{DB2}})/\mathsf{V}_{\mathsf{INDET}} \end{array}$

And the duty cycle on DL or DH will then be approximately half of  $D_{TOTAL}$ . Please note that due to oscillator comparator overshoot the exact duty cycle calculated using above formula may be slightly different. To better understand the PWM operation during start up refer to "Timing Diagram and Soft Start Duty Cycle Control" graph, for PWM operation after start up see "Feed-Forward Function Diagram".

For each specific application the  $R_{DB1}/R_{DB2}$  ratio must be chosen to provide maximum duty cycle with appropriate dead time at minimum supply voltage. The voltage at  $R_{DB}$  pin that corresponds to maximum duty cycle at minimum input voltage can be determined by applying a precise voltage source on this pin for the dead time required. The SiP11205 has a stable 3.3 V reference with 3 % temperature accuracy, so a typical 3 % duty variation and 1 % DL/DH matching can be achieved. There will be 0.75 % duty reduction for each 1 V increase in the V<sub>IN</sub> supply range. For better system efficiency it is recommended that the input voltage range be limited to 42 V to 55 V.

#### Soft Start

The soft start circuit plays an important role in protecting the controller. At startup it prevents high in-rush current. During a normal start-up sequence ( $V_{CS} < V_{MOC}$ .  $V_{CS}$  is the voltage at CS pin), or following any event that would cause a hiccup-and-soft-start sequence,  $C_{SS}$  will be charged from about 0 V to a final voltage of 2  $V_{BE}$  +  $V_{INDET}/2$  at a 20  $\mu$ A rate. As the voltage on the  $C_{SS}$  rises towards the final voltage, the maximum permitted DL and DH duty cycles will increase from 0 % to a maximum defined by the R<sub>DB</sub> resistor divider.

When a mild fault condition is detected (V<sub>CS</sub> = V<sub>MOC</sub>), C<sub>SS</sub> goes into a hiccup mode until fault condition is removed. The hiccup is activated when C<sub>SS</sub> discharges to 0.85 V<sub>SS</sub> at 20  $\mu$ A and subsequently at 0.4  $\mu$ A until the fault condition is removed. Refer to "Fault Conditions and Responses" for details.

#### **Fault Conditions and Responses**

The faults that can cause a hiccup-and-retry cycle are moderate over-current (MOC), severe over-current (SOC), chip level UVLO, system level UVLO, and over temperature protection (OTP).

Prior to detailing the various fault conditions and responses, some definitions are given:

- 1. A complete switching period, T, consists of two oscillator cycles T<sub>DL</sub> and T<sub>DH</sub>.

- 2.  $T_{DL}$  ( $T_{DH}$ ) is the oscillator cycle during which the DL (DH) output is in the high state.

- 3. T is defined as starting at the beginning of  $T_{DL}$ , and terminating at the end of  $T_{DH}$ .

#### Response to MOC Faults ( $V_{MOC} < V_{CS} < V_{SOC}$ ):

Once SiP11205 has completed a normal soft-start cycle,  $\rm V_{SS}$  will be clamped at the final voltage, allowing the maximum possible duty cycle on DL and DH.

If an MOC fault occurs following the start-up (due to a condition such as an excessive load on the converter's output), SiP11205 will respond by gradually reducing the available maximum duty cycle of its DL and DH outputs each to be equal to approximately 42 % of their possible 47 % maximum values. This is before any effects of deadtime introduced by  $R_{DB}$  are added in. This reduction in available maximum duty cycle is achieved by reducing the voltage on the SS pin to 4 V, as follows:

- 1. If  $V_{MOC} < V_{CS} < V_{SOC}$  at any time during  $T_{DL}$ , a current of 20  $\mu$ A will be drawn out of the SS pin until the beginning of the next  $T_{DL}$ .

- 2. If the voltage on the SS pin remains above the value that would allow an available maximum DL and DH duty cycle of 42 %, SiP11205 will continue operating.

- 3. If the voltage on the SS pin goes below the value that would allow an available maximum DL and DH duty cycle of 42 %, a hiccup interval is started, during which both DL and DH are held in their low states.

- 4. The SS pin is discharged towards 0 V by a 400 nA sink current.

- 5. The hiccup interval is terminated when the SS pin is discharged to 0.25 V.

After the above actions have been taken switching on the DL and DH outputs will then resume with a normal soft-start cycle.

Response to MOC faults is enabled after the successful completion of any normal soft-start cycle.

Response to SOC Faults ( $V_{CS} > V_{SOC}$ ):

This is an immediate, single-cycle response over current shutdown, followed by a hiccup delay and a normal soft-start cycle. Since this is a gross fault protection mechanism, its triggering mechanism is asynchronous to the timing of  $\rm T_{DL}$  and  $\rm T_{DH}.$

- 1. If  $V_{CS} > V_{SOC}$ , a hiccup interval is started, during which both DL and DH are held in their low states.

- 2. The SS pin is discharged towards 0 V by a 400 nA sink current.

- 3. The hiccup interval is terminated when the SS pin is discharged to 0.25 V.

- 4. Switching on the DL and DH outputs will then resume with a normal soft-start cycle.

Severe over current response is enabled at all times, including the initial ramp-up period of the soft-start pin. This allows SiP11205 to provide rapid fault protection for the converter's power train.

### Vishay Siliconix

#### Immediate Response to UVLO Faults:

The under voltage protection conditions at converter-level (V<sub>INDET</sub> pin UVLO) and chip-level (V<sub>CC</sub> UVLO) will immediately trigger a shutdown-and-retry SS response, with the restart requirements being that:

- 1. The SS pin has been discharged at a 20  $\mu\text{A}$  rate to the 0.25 V level.

- 2. The affected supply has recovered to its turn-on threshold.

Once these conditions are met, switching will resume with a normal soft-start cycle. Response to UVLO faults is enabled at all times, including the initial ramp-up period of the softstart pin.

Immediate Response to an OTP Condition:

Failure of the application circuit to provide an external voltage to the V<sub>CC</sub> pin above the V<sub>REG</sub> level may result in an OTP condition (T<sub>J</sub> > OTP<sub>ON</sub>). Other conditions, such as excessive ambient temperature or, where applicable, failure of airflow over the DC-DC converter circuit, can also trigger an OTP condition. An OTP condition will immediately trigger a shutdown-and-retry soft start response, with the restart requirements being that:

- 1. The SS pin has been discharged at a 20  $\mu\text{A}$  rate to the 0.25 V level.

- 2. The chip junction temperature has fallen below the lower OTP threshold.

Once these conditions are met, switching will resume with a normal soft-start cycle. Response to the OTP condition is enabled at all times, including the initial ramp-up period of the soft-start pin.

### Reference

The reference voltage of SiP11205 is set at 3.3 V at V<sub>REF</sub> pin. This pin should be decoupled externally with a 0.1 µF to 1 µF capacitor to GND. Up to 5 mA may be drawn internally from this reference to power external circuits. Note that if the V<sub>INDET</sub> pin is pulled below 0.55 V (typical), the reference will be turned off, and SiP11205 will enter a low-power "standby" mode. During startup or when V<sub>REF</sub> is accidentally shorted to ground, this pin has internal short circuit protection limiting the source current to 50 mA. V<sub>REF</sub> load regulation for 5 mA step is typically 0.45 %.

### Oscillator

The oscillator is designed to operate from 200 kHz to 1 MHz with temperature stability within 15 %. This operating frequency range allows the converter to minimize the inductor and capacitor size, improving the power density of the converter. The oscillator frequency, and therefore the switching frequency, is programmable by the value of resistor and capacitor connected to the  $R_{OSC}$  and  $C_{OSC}$  pins respectively. Note that the switching frequency at pins DL and DH is half of the oscillator frequency, i.e., the DL output

will be active during one oscillator cycle, and the DH during the next oscillator cycle.

The feed-forward voltage appears at pin  $R_{OSC}$  and equals to  $V_{INDET}/2$ . This voltage sets the peak voltage of the oscillator waveform. Therefore the higher input voltage the higher  $V_{INDET}/2$  and the higher oscillator peak voltage. The pulse width of the drive signals DL and DH is then generated by comparing the voltage at  $R_{DB}$  pin with the oscillator output saw tooth. The voltage at  $R_{DB}$  pin is fixed so the higher input voltage the narrower DL/DH pulse width and the lower the duty cycle. (See Feed-forward Function Diagram.)

### VINDET

The V<sub>INDET</sub> pin controls several modes of operation and the modes of operation are controlled by shutdown (V<sub>SD</sub>) and under voltage (V<sub>UV</sub>) comparators (see block diagram). When the IC is powered solely by V<sub>IN</sub> and V<sub>INDET</sub> is less than V<sub>SDH</sub> due to some external reset condition the pre-regulator is in low power standby mode and the internal bias network is powered down. When V<sub>INDET</sub> is greater than V<sub>SDH</sub> but less than V<sub>REF</sub> and V<sub>CC</sub> is forced to 12 V the pre-regulator shuts off drawing only leakage current from V<sub>IN</sub> and quiescent current from V<sub>CC</sub>. In this mode the controller output drivers remains static (non-switching). When V<sub>INDET</sub> is above V<sub>REF</sub> the controller is enabled and both drivers are switching at half the oscillator frequency. If SiP11205 is shut down via this pin, its restart will be by means of a soft-start cycle, as described under "Soft Start" and "Hiccup-Mode Operation" above.

The input impedance to ground of this pin is typically 46K  $\pm$  30 % and must be taken into account when designing the feed-forward compensation. An external 10:1 resistor divider ratio of supply voltage to V<sub>INDET</sub> pin is required in a typical application.

### **Primary Side MOSFET Drivers**

The low-side MOSFET driver is powered directly from V<sub>CC</sub> of the chip. The high-side MOSFET however requires the gate voltage to be higher than V<sub>IN</sub>. This is achieved with a charge pump capacitor C<sub>BST</sub> between BST and LX, and an external diode to charge and bootstrap the initial charge up voltage across C<sub>BST</sub> to V<sub>CC</sub> level. On the alternate oscillator cycle the boost diode isolates BST from V<sub>IN</sub> and hence BST and LX steps up to V<sub>IN</sub> + V<sub>CC</sub> and V<sub>IN</sub>, respectively. This sequencing insures that DL will always turn on before DH during start-up. The boost capacitor value must be chosen to meet the application droop rate requirement.

### **External Frequency Synchronization**

The oscillator frequency of this IC can be synchronized to an external source with a simple circuit shown in "Circuit for Frequency Synchronization" diagram. The synchronized frequency should not exceed 1.4 times the set frequency, and the synchronized frequency range should not exceed the IC frequency range.

SiP11205 Vishay Siliconix

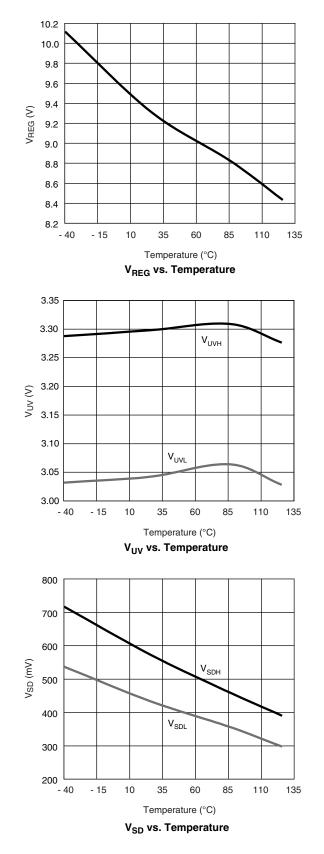

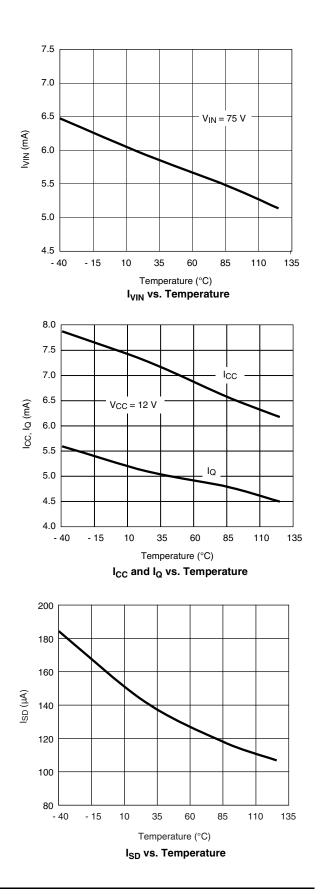

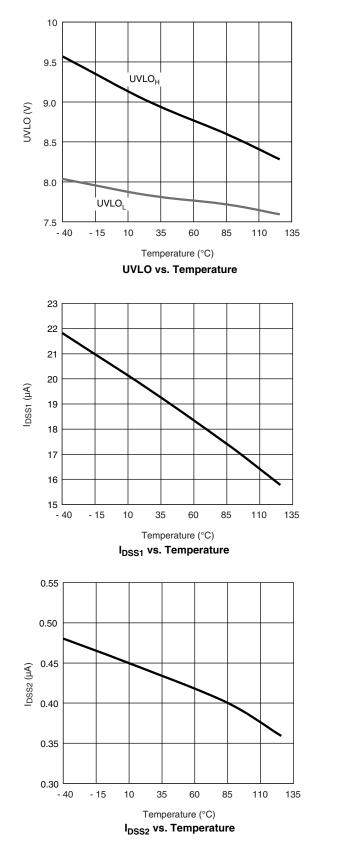

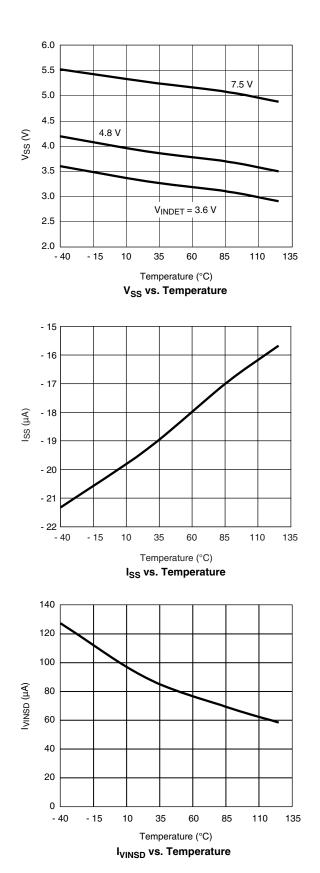

### **TYPICAL CHARACTERISTICS**

Document Number: 69233 S-81795-Rev. C, 04-Aug-08

Vishay Siliconix

### **TYPICAL CHARACTERISTICS**

VISHAY

SiP11205 Vishay Siliconix

### **TYPICAL CHARACTERISTICS**

Document Number: 69233 S-81795-Rev. C, 04-Aug-08

Vishay Siliconix

### **TYPICAL CHARACTERISTICS**

135

Vishay Siliconix

### **TYPICAL CHARACTERISTICS**

Vishay Siliconix

### **TYPICAL WAVEFORMS**

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see http://www.vishay.com/ppg?69233.

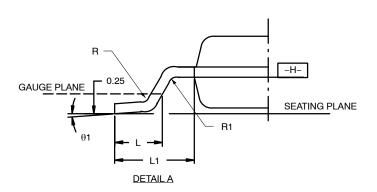

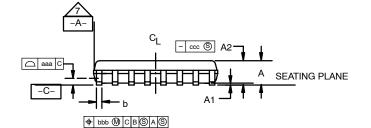

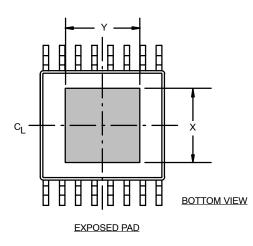

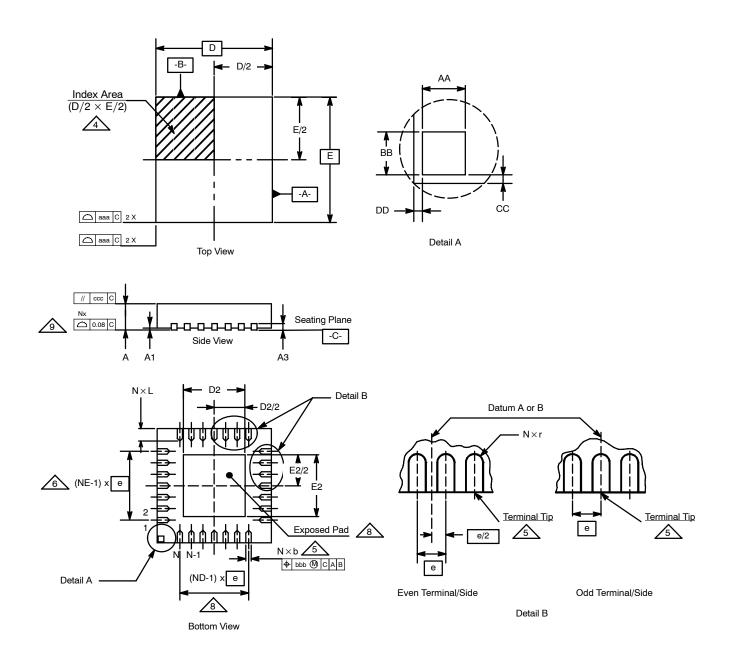

### POWER IC THERMALLY ENHANCED PowerPAK® TSSOP: 14/16-LEAD

|                       | M     | LLIMETE  | RS    |            | NCHES'     | ŧ      |  |

|-----------------------|-------|----------|-------|------------|------------|--------|--|

| Dim                   | Min   | Nom      | Max   | Min        | Nom        | Max    |  |

| Α                     | -     | -        | 1.20  | -          | -          | 0.0472 |  |

| <b>A</b> <sub>1</sub> | 0.025 | -        | 0.100 | 0.001      | -          | 0.0039 |  |

| A <sub>2</sub>        | 0.80  | 0.90     | 1.05  | 0.0315     | 0.0354     | 0.0413 |  |

| b                     | 0.19  | -        | 0.30  | 0.0075     | -          | 0.0118 |  |

| b1                    | 0.19  | 0.22     | 0.25  | 0.0075     | 0.0087     | 0.0098 |  |

| С                     | 0.09  | -        | 0.20  | 0.0035     | -          | 0.0079 |  |

| c1                    | 0.09  | -        | 0.16  | 0.0035     | -          | 0.0063 |  |

| D                     | 4.9   | 5.0      | 5.1   | 0.1929     | 0.1968     | 0.2008 |  |

| е                     |       | 0.65 BSC | r.    |            | 0.0256 BSC |        |  |

| Е                     | 6.2   | 6.4      | 6.6   | 0.2441     | 0.2520     | 0.2598 |  |

| E <sub>1</sub>        | 4.3   | 4.4      | 4.5   | 0.1693     | 0.1732     | 0.1772 |  |

| L                     | 0.45  | 0.60     | 0.75  | 0.0177     | 0.0236     | 0.0295 |  |

| L1                    |       | 1.0 REF  | r.    | 0.0394 REF |            |        |  |

| R                     | 0.09  | -        | -     | 0.0035     | -          | -      |  |

| R1                    | 0.09  | -        | -     | 0.0035     | -          | -      |  |

| θ1                    | 0     | -        | 0     | 0          | -          | 0      |  |

| N (14)                |       | 14       | 1     |            | 14         | 1      |  |

| N (16)                |       | 16       |       | 16         |            |        |  |

| Х                     | 2.95  | 3.0      | 3.05  | 0.116      | 0.118      | 0.120  |  |

| Y (14)                | 3.15  | 3.2      | 3.25  | 0.124      | 0.126      | 0.128  |  |

| Y (16)                | 2.95  | 3.0      | 3.05  | 0.116      | 0.118      | 0.120  |  |

| aaa                   |       | 0.10     |       |            | 0.0039     |        |  |

| bbb                   |       | 0.10     |       |            | 0.0039     |        |  |

| CCC                   |       | 0.05     |       |            | 0.0020     |        |  |

| ddd                   |       | 0.20     |       | 0.0079     |            |        |  |

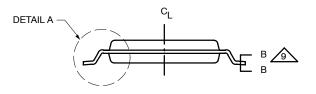

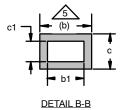

### POWER IC THERMALLY ENHANCED PowerPAK® TSSOP: 14/16-LEAD

\*Dimensions are in mm converted to inches.

NOTES:

- 1. All dimensions are in millimeters (angles in degrees).

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- $\cancel{3}$  Dimension "D" does not include mold flash, protrusions or gate burrs.

- A Dimension "E1" does not include internal flash or protrusion.

- 5. Dimension "b" does not include Dambar protrusion.

- 6. "N" is the maximum number of lead terminal positions for the specified package length.

- $2^{\uparrow}$  Datums  $A_{-}$  and  $B_{-}$  to be determined at datum plane  $H_{-}$  .

- 2 Dimensions "D" and "E1" are to be determined at datum plane -H-.

- Cross section B-B to be determined at 0.10 to 0.25 mm from the lead tip.

- 10. Refer to JEDEC MO-153, Issue C., Variation ABT.

- 11. Exposed pad will depend on the pad size of the L/F.

### Package Information Vishay Siliconix

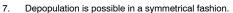

### PowerPAK<sup>®</sup> MLP44-16 (POWER IC ONLY)

JEDEC Part Number: MO-220

#### PowerPAK® MLP44-16 (Power IC Only)

JEDEC Part Number: MO-220

|     | MI       | LLIMETER | RS*  | INCHES     |            |        |       |

|-----|----------|----------|------|------------|------------|--------|-------|

| Dim | Min      | Nom      | Max  | Min        | Nom        | Max    | Notes |

| А   | 0.80     | 0.90     | 1.00 | 0.0315     | 0.0354     | 0.0394 |       |

| A1  | 0        | 0.02     | 0.05 | 0          | 0.0008     | 0.0020 |       |

| A3  | -        | 0.20 Ref | -    | -          | 0.0079     | -      |       |

| AA  | -        | 0.345    | -    | -          | 0.0136     | -      |       |

| aaa | -        | 0.15     | -    | -          | 0.0059     | -      |       |

| BB  | -        | 0.345    | -    | -          | 0.0136     | -      |       |

| b   | 0.25     | 0.30     | 0.35 | 0.0098     | 0.0118     | 0.138  | 5     |

| bbb | -        | 0.10     | -    | -          | 0.0039     | -      |       |

| CC  | -        | 0.18     | -    | -          | 0.0071     | -      |       |

| CCC | -        | 0.10     | -    | -          | 0.0039     | -      |       |

| D   |          | 4.00 BSC |      | 0.1575 BSC |            |        |       |

| D2  | 2.55     | 2.7      | 2.8  | 0.1004     | 0.1063     | 0.1102 |       |

| DD  | -        | 0.18     | -    | -          | 0.0071     | -      |       |

| E   |          | 4.00 BSC |      |            | 0.1575 BSC |        |       |

| E2  | 2.55     | 2.7      | 2.8  | 0.1004     | 0.1063     | 0.1102 |       |

| е   |          | 0.65 BSC |      |            | 0.0256 BSC |        |       |

| L   | 0.3      | 0.4      | 0.5  | 0.0118     | 0.0157     | 0.0197 |       |

| Ν   | 16       |          |      | 16         |            | 3, 7   |       |

| ND  | -        | 4        | -    | -          | 4          | -      | 6     |

| NE  | -        | 4        | -    | -          | 4          | -      | 6     |

| r   | b(min)/2 | -        | -    | b(min)/2   | -          | -      |       |

\* Use millimeters as the primary measurement.

ECN: S-50794—Rev. B, 16-May-05 DWG: 5905

NOTES:

1. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

2. All dimensions are in millimeters. All angels are in degrees.

3. N is the total number of terminals.

4. The terminal #1 identifier and terminal numbering convention shall conform to JESD 95-1 SPP-012. Details of terminal #1 identifier are optional, but must be located within the zone indicated. The terminal #1 identifier may be either a molded or marked feature. The X and Y dimension will vary according to lead counts.

$\sqrt{5.}$  Dimension b applies to metallized terminal and is measured between 0.25 mm and 0.30 mm from the terminal tip.

$\underline{/6.}$  ND and NE refer to the number of terminals on the D and E side respectively.

$\sqrt{9.}$  Coplanarity applies to the exposed heat sink slug as well as the terminals.

Vishay

### Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

© 2024 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

Revision: 01-Jan-2024