# **Configurable H-Bridge Driver**

#### **FEATURES**

- H-Bridge or Dual Half-Bridge Operation

- 20- to 40-V Supply

- Static (dc) Operation

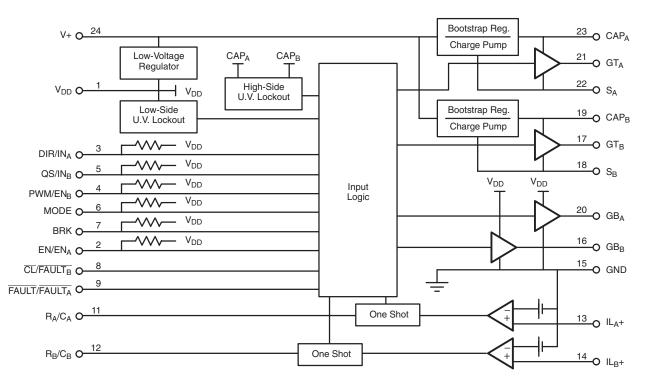

FUNCTIONAL BLOCK DIAGRAM

- Cross-Conduction Protected

- Current Limit

- ESD Protected

- Fault Output

- Undervoltage Lockout

#### DESCRIPTION

The Si9978 is an integrated driver for an n-channel MOSFET H-bridge. The mode control allows operation as either a full H-bridge driver or as two independent half-bridges. The DIR/PWM input configuration allows easy implementation of either sign/magnitude or anti-phase PWM drive schemes for full H-bridges. Schmitt triggers on the inputs provide logic signal compatibility and hysteresis for increased noise immunity. An internal low-voltage regulator allows the device to be powered directly from a system supply of 20 to 40 volts. All n-channel gates are driven directly from low-impedance outputs. The addition of one external capacitor per half-bridge allows internal circuitry to level shift both the power supply and logic signal for the high-side n-channel gate drives. Internal charge pumps replace leakage current lost in the high-side driver circuits to provide "static" (dc) operation in any output condition. Protection features include an undervoltage lockout, cross-conduction prevention logic, and overcurrent monitors.

The Si9978 is available in both standard and lead (Pb)-free, 24-pin wide-body SOIC (surface mount) packages, specified to operate over the industrial (-40 to +85°C) temperature range.

#### Document Number: 70011 S-40804-Rev. E, 26-Apr-04

# Si9978 Vishay Siliconix

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on pins 2–7 with respect to ground | -0.3 to V <sub>DD</sub> + 0.3 V |

|--------------------------------------------|---------------------------------|

| Voltage on pin 24                          | –0.3 to 50 V                    |

| Voltage on pins 17, 19, 21, 23             | –0.3 to +60 V                   |

| Voltage on pins 18, 22                     | –2 to 50 V                      |

| Operating Temperature (T <sub>A</sub> )40 to +85   | °С  |

|----------------------------------------------------|-----|

| Storage Temperature                                | °С  |

| Maximum Junction Temperature (T <sub>J</sub> ) 150 | )°C |

| Power Dissipation                                  | nW  |

### **RECOMMENDED OPERATING CONDITIONS**

| V+                              | +20 to 40 $V_{DC}$ |

|---------------------------------|--------------------|

| R <sub>A</sub> , R <sub>B</sub> | 100 kΩ             |

| SPECIFICATIONS                   |                  |                                                         |                  |                        |                  |      |  |  |

|----------------------------------|------------------|---------------------------------------------------------|------------------|------------------------|------------------|------|--|--|

|                                  |                  | Test Conditions<br>Unless Otherwise Specified           |                  | Limits<br>-40 to 85°C  |                  |      |  |  |

| Parameter                        | Symbol           | V+ = 20 to 40 V                                         | Min <sup>a</sup> | Тур <sup>ь</sup>       | Max <sup>a</sup> | Unit |  |  |

| Power                            |                  |                                                         | •                | •                      | •                | •    |  |  |

| Supply Voltage Range             | V+               |                                                         | 20               |                        | 40               | v    |  |  |

| Logic Voltage                    | V <sub>DD</sub>  |                                                         | 14.5             | 16                     | 17.5             | l V  |  |  |

| Supply Current                   | I+               | I <sub>DD</sub> = 0 mA                                  |                  | 3                      | 5                | mA   |  |  |

| Inputs (DIR, PWM, EN, QS, M      | IODE, BRK)       |                                                         |                  | 1                      |                  | •    |  |  |

| High-State                       | VIH              |                                                         | 4.0              | 1                      | 1                |      |  |  |

| Low-State                        | V <sub>IL</sub>  |                                                         |                  |                        | 1.0              | V    |  |  |

| High-State Input Current         | I <sub>IH</sub>  | $V_{IH} = V_{DD}$                                       |                  |                        | 10               |      |  |  |

| Low-State Input Current          | IIL              | $V_{IL} = 0 V$                                          | -100             | -50                    | -25              | μΑ   |  |  |

| Outputs                          |                  |                                                         |                  |                        |                  |      |  |  |

| Low-Side Gate Drive, High State  | V <sub>GBH</sub> |                                                         | 14               | 16                     | 17.5             | 1    |  |  |

| Low-Side Gate Drive, Low State   | V <sub>GBL</sub> |                                                         |                  |                        | 1                |      |  |  |

| High-Side Gate Drive, High State | V <sub>GTH</sub> |                                                         | 16               | 18                     | V                |      |  |  |

| High-Side Gate Drive, Low State  | V <sub>GTL</sub> | S <sub>A, B</sub> = 0 V                                 |                  |                        | 1                |      |  |  |

| Low-Side Switching, Rise Time    | t <sub>rL</sub>  |                                                         |                  | 110                    |                  |      |  |  |

| Low-Side Switching, Fall Time    | t <sub>fL</sub>  | Rise Time = 1 to 10 V                                   |                  | 50                     |                  | ns   |  |  |

| High-Side Switching, Rise Time   | t <sub>rH</sub>  | Fall Time = 10 to 1 V<br>$C_L = 600 \text{ pF}$         |                  | 110                    |                  |      |  |  |

| High-Side Switching, Fall Time   | t <sub>fH</sub>  |                                                         |                  | 50                     |                  |      |  |  |

| Break-Before-Make Time           |                  |                                                         |                  | 250                    |                  |      |  |  |

| FAULT, CL                        | V <sub>OL</sub>  | I <sub>OL</sub> = 1 mA                                  |                  |                        | 0.4              | V    |  |  |

| FAULT, CL Leakage Current        | I <sub>ОН</sub>  | $\overline{FAULT}, \overline{CL} = V_{DD}$              |                  | 0.2                    | 10               | μΑ   |  |  |

| Protection                       |                  |                                                         |                  |                        |                  |      |  |  |

| Low-Side Undervoltage Lockout    | UVLL             |                                                         |                  | 0.8 V <sub>DD</sub>    |                  | 1    |  |  |

| Low-Side Hysteresis              | V <sub>H</sub>   |                                                         |                  | 0.8                    |                  | V    |  |  |

| High-Side Undervoltage Lockout   | UVLH             | S <sub>A, B</sub> = 0 V                                 |                  | V <sub>DD</sub> -3.3 V |                  | 1    |  |  |

| Current Limit                    |                  |                                                         |                  |                        |                  |      |  |  |

| Comparator Input Bias Current    | I <sub>IB</sub>  |                                                         | -5               | -0.2                   | 5                | μA   |  |  |

|                                  |                  | $T_A = 25^{\circ}C$                                     | 90               | 100                    | 110              |      |  |  |

| Comparator Threshold Voltage     | V <sub>TH</sub>  |                                                         | 85               |                        | 115              | mV   |  |  |

|                                  |                  | $R_A$ , $R_B$ = 100 k $\Omega$ , $C_A$ , $C_B$ = 100 pF | 8                | 10                     | 12               | 1    |  |  |

| One Shot Pulse Width             | t <sub>p</sub>   | $R_A,R_B$ = 100 kΩ, $C_A,C_B$ = 0.001 $\mu F$           | 80               | 100                    | 120              | μs   |  |  |

| Propagation Delay                | t <sub>pd</sub>  | C <sub>L</sub> = 600 pF                                 |                  | 600                    |                  | ns   |  |  |

Notes:

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

| TRUTH TABLE—H-BRIDGE MODE |                         |                        |                        |                         |     |                   |                   |     |     |                 |     |                           |                              |                                    |

|---------------------------|-------------------------|------------------------|------------------------|-------------------------|-----|-------------------|-------------------|-----|-----|-----------------|-----|---------------------------|------------------------------|------------------------------------|

| MODE                      | DIR/<br>IN <sub>A</sub> | EN/<br>EN <sub>A</sub> | QS/<br>IN <sub>B</sub> | PWM/<br>EN <sub>B</sub> | BRK | IL <sub>A</sub> + | IL <sub>B</sub> + | GTA | GBA | GT <sub>B</sub> | GBB | CL/<br>FAULT <sub>B</sub> | FAULT/<br>FAULT <sub>A</sub> | Condition                          |

| 1                         | 1                       | 1                      | 1                      | Л                       | 0   | L                 | Х                 | Н   | L   | L               | Г   | 1                         | 1                            | Normal<br>Operation                |

| 1                         | 1                       | 1                      | 0                      | Л                       | 0   | L                 | х                 | Л   | L   | L               | Л   | 1                         | 1                            |                                    |

| 1                         | 0                       | 1                      | 1                      | Л                       | 0   | L                 | х                 | L   | Л   | н               | L   | 1                         | 1                            |                                    |

| 1                         | 0                       | 1                      | 0                      | Л                       | 0   | L                 | х                 | L   | Л   | Л               | L   | 1                         | 1                            |                                    |

| 1                         | Х                       | 1                      | х                      | х                       | 1   | L                 | Х                 | L   | Н   | L               | Н   | 1                         | 1                            | Brake                              |

| 1                         | Х                       | 0                      | х                      | х                       | Х   | L                 | Х                 | L   | L   | L               | L   | 1                         | 1                            | Disable                            |

| 1                         | х                       | 1                      | х                      | Х                       | 0   | Л                 | х                 | L   | L   | L               | L   |                           |                              | Overcurrent                        |

| 1                         | х                       | х                      | х                      | х                       | х   | х                 | х                 | L   | L   | L               | L   | 1                         | 0                            | Undervoltage<br>on V <sub>DD</sub> |

| TRUT | TRUTH TABLE—HALF-BRIDGE MODE |                        |                        |                         |     |                   |                   |     |                 |                 |                 |                           |                              |                                    |

|------|------------------------------|------------------------|------------------------|-------------------------|-----|-------------------|-------------------|-----|-----------------|-----------------|-----------------|---------------------------|------------------------------|------------------------------------|

| MODE | DIR/<br>IN <sub>A</sub>      | EN/<br>EN <sub>A</sub> | QS/<br>IN <sub>B</sub> | PWM/<br>EN <sub>B</sub> | BRK | IL <sub>A</sub> + | IL <sub>B</sub> + | GTA | GB <sub>A</sub> | GT <sub>B</sub> | GB <sub>B</sub> | CL/<br>FAULT <sub>B</sub> | FAULT/<br>FAULT <sub>A</sub> | Condition                          |

| 0    | 1                            | 1                      | Х                      | 0                       | Х   | L                 | L                 | Н   | L               | L               | L               | 1                         | 1                            |                                    |

| 0    | 0                            | 1                      | Х                      | 0                       | Х   | L                 | L                 | L   | н               | L               | L               | 1                         | 1                            | Normal                             |

| 0    | Х                            | 0                      | 1                      | 1                       | Х   | L                 | L                 | L   | L               | н               | L               | 1                         | 1                            | Operation                          |

| 0    | Х                            | 0                      | 0                      | 1                       | Х   | L                 | L                 | L   | L               | L               | н               | 1                         | 1                            |                                    |

| 0    | Х                            | 1                      | х                      | х                       | х   | Л                 | х                 | L   | L               | х               | х               | 1                         | Ţ                            | Overcurrent on<br>A                |

| 0    | Х                            | х                      | х                      | 1                       | х   | х                 | Л                 | х   | х               | L               | L               | Ţ                         | 1                            | Overcurrent on<br>B                |

| 0    | х                            | х                      | х                      | х                       | х   | х                 | х                 | L   | L               | L               | L               | 0                         | 0                            | Undervoltage<br>on V <sub>DD</sub> |

## Si9978

## **Vishay Siliconix**

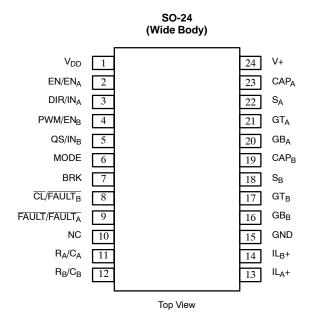

### **PIN CONFIGURATION AND ORDERING INFORMATION**

| ORDERING INFORMATION                                                                   |                |             |             |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|----------------|-------------|-------------|--|--|--|--|--|--|

| Lead (Pb)-Free     Temperature       Part Number     Part Number     Range     Package |                |             |             |  |  |  |  |  |  |

| Si9978DW                                                                               |                | –40 to 85°C | SOIC-24     |  |  |  |  |  |  |

| Si9978DW-T1                                                                            | Si9978DW-T1—E3 | -40 to 85°C | (Wide Body) |  |  |  |  |  |  |

### **PIN DESCRIPTION**

#### Pin 1: V<sub>DD</sub>

$V_{DD}$  is an internally generated voltage. It is connected to this pin to allow connection of a decoupling capacitor. A minimum of 1  $\mu F$  is recommended.

#### Pin 2: EN/EN<sub>A</sub>

The EN input allows normal operation when at logic "1", and turns all gate drive outputs off when at logic "0". When the mode pin is at logic "1", EN controls the entire H-bridge. When the mode pin is at logic "0", this pin becomes the ENABLE pin for half-bridge A.

#### Pin 3: DIR/INA

The function of this pin is determined by the MODE pin. When the MODE pin is at logic "1", it is the DIR pin, and when MODE is at logic "0", it is the  $IN_A$  pin.

As the DIR input, it is the direction control for the H-bridge, and determines which diagonal pair of power MOSFETs is active. A logic "1" turns on  $GT_A$  and enables  $GB_B$ , while a logic "0" turns on  $GT_B$  and enables  $GB_A$ . When implementing an anti-phase PWM control, the DIR input serves as the PWM input.

As the  $IN_A$  pin, it is the input that controls the "A" half-bridge. When at logic "1", the high-side MOSFET is turned on, and when at logic "0", the low-side MOSFET is turned on.

#### Pin 4: PWM/EN<sub>B</sub>

With the mode pin at logic "1", this pin is the PWM input. It controls the switching of the active diagonal pair. A logic "1" turns the active MOSFETs on, while a logic "0" turns it off. The QS input determines whether the bottom or both bottom and top MOSFETs are switched. When implementing an anti-phase PWM control, the PWM input is connected to a logic "1". When the mode pin is at logic "0", this pin becomes the ENABLE pin for half-bridge B.

#### Pin 5: QS/IN<sub>B</sub>

With the mode pin at logic "1", this input determines whether the bottom MOSFETs of the H-bridge or both bottom and top MOSFETs switch in response to the PWM signal. A logic "1" on this input enables only the bottom MOSFETs. This is the default condition as this pin is pulled up internally. When this pin is pulled to ground, both the bottom and top MOSFETs are enabled.

This input controls the B half-bridge when the MODE pin is at logic "0". When at logic "1", the high-side MOSFET is turned on, and when at logic "0", the low-side MOSFET is turned on.

### **PIN DESCRIPTION (CONT'D)**

#### Pin 6: MODE

This input determines whether the Si9978 functions as an H-bridge or as two independent half-bridges. When the MODE pin is at logic "1", the Si9978 functions as an H-bridge, and when MODE is at logic "0", it functions as two independent half-bridges.

#### Pin 7: BRK

When this input and MODE are at logic "1", both bottom gate drives are switched high, turning on the bottom MOSFETs. When this input is at logic "0", the Si9978 operates normally.

#### Pin 8: CL/FAULT<sub>B</sub>

This is an open drain output which is active low. When the MODE pin is at logic "1", this pin functions as  $\overline{CL}$  and indicates that the H-bridge is in current limit. It stays low for the duration of the current limit one-shot. With the MODE pin at logic "0", it serves as the FAULT output for half-bridge B to indicate when an undervoltage or overcurrent condition is detected. When indicating an overcurrent condition, the output stays low for the duration of the current limit one-shot. The FAULT output resets automatically when the condition clears.

#### Pin 9: FAULT/FAULTA

This is an open drain output which is switched low when an undervoltage or overcurrent condition is detected. When indicating an overcurrent condition, the output stays low for the duration of the current limit one-shot. When the MODE pin is at logic "1", this pin is the H-bridge FAULT output. With the MODE pin at logic "0", it serves as the FAULT output for half-bridge A. The FAULT output resets automatically when the condition clears.

#### Pin 10: NC

No internal connection.

#### Pin 11: R<sub>A</sub>/C<sub>A</sub>

The timing resistor and capacitor for the current limit one-shot are connected to this pin. The values of the resistor and capacitor determine the off time set by the one-shot. The one-shot is triggered when the current limit comparator detects an overcurrent condition.

#### Pin 12: R<sub>B</sub>/C<sub>B</sub>

The timing resistor and capacitor for the current limit one-shot are connected to this pin. The values of the resistor and capacitor determine the off time set by the one-shot. The one-shot is triggered when the current limit comparator detects an overcurrent condition.

#### Pin 13: IL<sub>A</sub>+ and Pin 14, IL<sub>B</sub>+

These are the overcurrent sense inputs. Internally, they are connected to the noninverting inputs of the current limit comparators. Externally they are connected to the source(s) of the low-side MOSFET(s) and the current sense resistor.

#### Pin 15: GND

The GND pin is the ground return for V+ and the ground reference for the logic. Also, this is the ground reference input for the current limit comparators and is connected to the ground side of the internal 100-mV references. This pin should be connected directly to the ground side of the current sensing resistors.

#### Pin 16: GB<sub>B</sub> and Pin 20, GB<sub>A</sub>

These pins drive the gates of the low-side power MOSFETs.

#### Pin 17: GT<sub>B</sub> and Pin 21, GT<sub>A</sub>

These pins drive the gates of the high-side power MOSFETs.

#### Pin 18: S<sub>B</sub> and Pin 22, S<sub>A</sub>

These are the source connections of the high-side power MOSFETs, the drain of the external low-side power MOSFET, the negative terminal of the bootstrap capacitor, and the output for each half-bridge.

#### Pin 19: CAP<sub>B</sub> and Pin 23, CAP<sub>A</sub>

These are the connections for the positive terminals of the bootstrap capacitors  $C_{BA}$  and  $C_{BB}$ . A 0.01- $\mu F$  capacitor can be used for most applications.

#### Pin 24: V+

This is the only external power supply required for the Si9978, and must be the same supply used to power the H-bridge it is driving. The Si9978 powers the low-voltage logic, low-side gate driver, and bootstrap/ charge pump circuits from self-contained voltage regulators which require only a bootstrap capacitor on the CAP pins.

No voltage sensing circuitry monitors V+ directly; however, the low-voltage, internally generated supply and the bootstrap voltage (which are derived from V+) are directly protected by undervoltage monitors.

## Si9978

# Vishay Siliconix

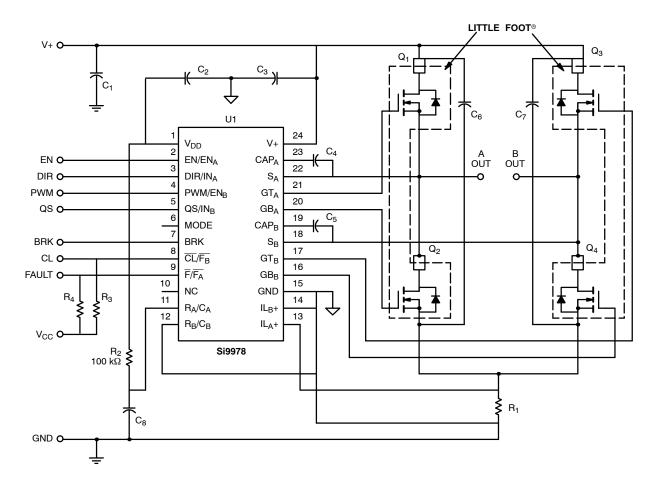

### **APPLICATION CIRCUIT**

FIGURE 1. Basic H-Bridge Circuit

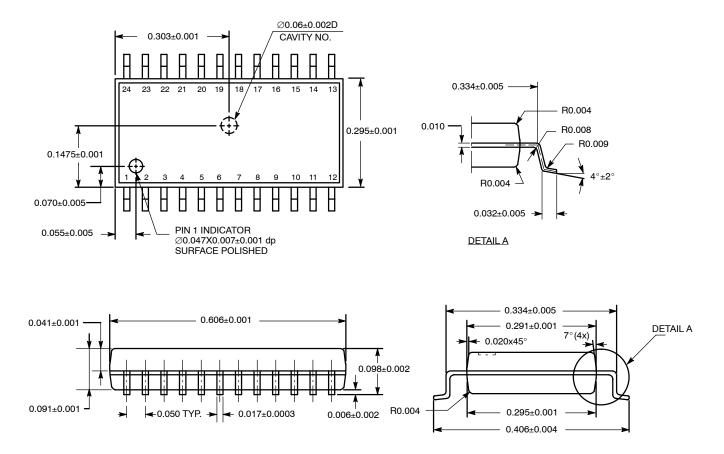

### SOIC (WIDE-BODY): 24-LEAD (POWER IC ONLY)

ECN: S-40085—Rev. A, 02-Feb-04 DWG: 5930

Vishay

# Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

© 2024 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

Revision: 01-Jan-2024