# eFuse Evaluation Board Manual

### INTRODUCTION

This reference board allows the user to evaluate the SiP32433A, SiP32433B, SiP32434A, and SiP32434B single-channel eFuse load switches. It can also be used for AEC-Q100 qualified versions of these devices, which have part numbers starting with SiPQ instead of SiP.

The SiP32433A, SiP32433B, SiP32434A, and SiP32434B integrate multiple control and protection features, which provide increased controllability and reliability with simplified designs and minimal external components. They protect both power sources and downstream circuitry connected to the switch from overloads, short circuits, voltage surges, and excessive inrush currents.

The output current limit can be set by a single external resistor.  $V_{IN}$  overvoltage protection and undervoltage lockout threshold levels can be set with an external resistor network.  $V_{IN}$  inrush current requirements can be set with a single external soft start capacitor.

Upon switch-off due to latchable faults, the SiP32433A and SiP32434A will latch the power switch off and the PGD will remain low. The switch can restart by resetting the EN or  $V_{\rm IN}$ . The SiP32433B and SiP32434B will auto retry if there is no OTP or OVP fault. The retry delay time is 32 times the soft start time set by the CSS.

Overcurrent, overtemperature, and short circuits are latchable faults, while overvoltage, undervoltage, and reverse current flow are non-latchable faults.

### **EVALUATION BOARD FEATURES**

The SiP32433A, SiP32433B, SiP32434A, and SiP32434B eFuse evaluation board features include:

- 3 V to 23 V operation

- Programmable current limit range. 150 mA to 3.5 A for the SiP32533 and 300 mA to 6 A for the SiP32434

- · Programmable soft start output voltage slew rate and auto retry time

- · Input path current sense resistor for current probing

- · Onboard MOSFET for output short test

- Programmable OVP threshold

- Reverse current blocking (SiP32433x only)

### **APPLICATIONS**

The evaluation board can be used for:

- · Servers and data storage

- · Routers and switches

- Hot swap and hot plug devices

- · Optical modules

- PCle and memory

- Industrial controls and automation

- TVs and gaming systems

## **DESCRIPTION**

This evaluation fits the evaluation of the eFuse products listed in Table 1.

| TABLE 1 - EVALUATION BOARD ORDERING INFORMATION |                       |                             |                              |                     |                              |                             |                     |                         |

|-------------------------------------------------|-----------------------|-----------------------------|------------------------------|---------------------|------------------------------|-----------------------------|---------------------|-------------------------|

| PART<br>NUMBER                                  | FAULT OFF<br>RESPONSE | R <sub>DS(ON)</sub><br>(mΩ) | MAX. I <sub>LIM</sub><br>(A) | REVERSE<br>BLOCKING | V <sub>IN</sub> RANGE<br>(V) | EN / UVLO SET ( $k\Omega$ ) | OVP SET $(k\Omega)$ | I <sub>LIM</sub><br>SET |

| SiP32433AEVB                                    | Latch                 | 78                          | 3.5                          | Yes                 | 3.3 to 23                    | 25 / 4.12                   | 15 / 1              | 2433A                   |

| SiP32433BEVB                                    | Auto-retry            | 78                          | 3.5                          | Yes                 | 3.3 to 23                    | 25 /4.12                    | 15 / 1              | 2433B                   |

| SiP32434AEVB                                    | Latch                 | 33                          | 6                            | No                  | 3.3 to 23                    | 25 /4.12                    | 15 / 1              | 2434A                   |

| SiP32434BEVB                                    | Auto-retry            | 33                          | 6                            | No                  | 3.3 to 23                    | 25 /4.12                    | 15 / 1              | 2434B                   |

Revision: 30-Nov-2023 1 Document Number: 62068

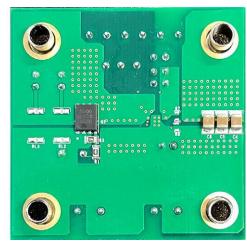

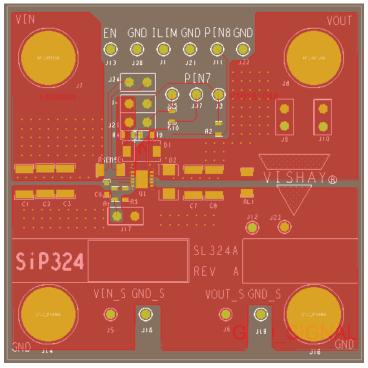

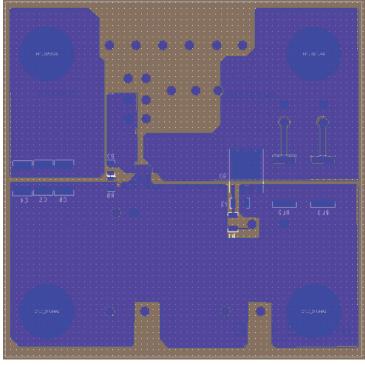

Fig. 1 - SiP32433xEVB, SiP32434xEVB Evaluation Board Rev. A

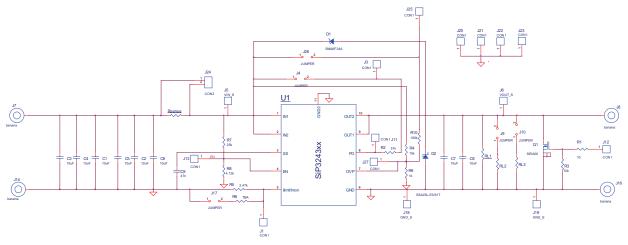

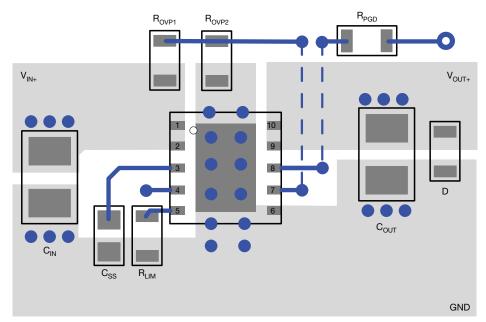

Fig. 2 - SiP3243xxEVB Schematic

## SiP3243XXEVB PHYSICAL ACCESS

Table 2 lists the SiP3243xxEVB eFuse evaluation board's switch on / off control, power input, and output connectors. Table 3 lists the test points. Table 4 describes jumpers and the functions to be set. These jumpers are off at the normal board setting.

| TABLE 2 - INPUT AND OUTPUT CONNECTOR DESCRIPTION |                  |                                                                                                            |  |

|--------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------|--|

| LABEL                                            | NAME             | DESCRIPTION                                                                                                |  |

| J13                                              | EN               | Active high enable and undervoltage input. Voltage divider resistors are 25 k $\Omega$ and 4.12 k $\Omega$ |  |

| J7                                               | V <sub>IN</sub>  | Power input connector                                                                                      |  |

| J14                                              | PGND             | Ground connection for the power input                                                                      |  |

| J16                                              | PGND             | Ground connection for the power output                                                                     |  |

| J8                                               | V <sub>OUT</sub> | Power output connector                                                                                     |  |

| TABLE 3 - TEST POINTS DESCRIPTION |                    |                                                           |  |

|-----------------------------------|--------------------|-----------------------------------------------------------|--|

| LABEL                             | NAME               | DESCRIPTION                                               |  |

| J27                               | OVP                | OVP pin probe point                                       |  |

| J25                               | OVP                | OVP pin probe through a 100 kΩ resistor                   |  |

| J18                               | GND                | IC ground sense                                           |  |

| J12                               | Gate               | High enable gate of MOSFET that shorts the output to GND  |  |

| J24                               | I <sub>SENSE</sub> | Differential sense of input current over a shunt resistor |  |

| J6                                | $V_{OUT\_S}$       | Power output sense point                                  |  |

| J19                               | GND                | IC ground sense                                           |  |

| J3                                | PG                 | PG pull-up voltage bias supply                            |  |

| J5                                | V <sub>IN_S</sub>  | Power input sense point                                   |  |

| TABLE 4 - JUMPER DESCRIPTION AND DEFAULT SETTING |                  |                                                                                                           |  |

|--------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------|--|

| LABEL                                            | NAME             | DESCRIPTION                                                                                               |  |

| J9                                               | RL2              | Connect load resistor                                                                                     |  |

| J10                                              | RL3              | Connect load resistor                                                                                     |  |

| J4                                               | PG               | Jumper that connects PG pull-up resistor to V <sub>IN</sub>                                               |  |

| J17                                              | R <sub>LIM</sub> | Jumper that connects R <sub>6</sub> as a parallel current limit setting resistor to R <sub>5</sub>        |  |

| J26                                              | OVP              | Jumper connects R <sub>10</sub> , OVP voltage divider upper resistor to be paralleled with R <sub>4</sub> |  |

#### **POWER INPUT AND OUTPUT TERMINALS**

The power header terminals are designed to allow a power supply and load to be connected easily to the evaluation board (see Fig. 1). The input voltage range for this evaluation is from 3.3 V to 23 V.

$D_2$  is the Schottky diode placed next to the device output to clamp the negative voltage when abruptly switching off an inductive load. A TVS diode can be placed at the input capacitor location in case input transient protection is required.

### **INPUT AND OUTPUT CAPACITORS**

The input capacitors ( $C_1$  to  $C_6$ ) and output capacitors ( $C_7$ ,  $C_8$ ) are mounted close to the device to ensure a stable voltage right before and after the eFuse load switch. The capacitances of these capacitors are 10  $\mu$ F. The voltage rating for input and output capacitors is 50 V. The SiP32433A, SiP32433A, SiP32434A, and SiP32434B can operate normally up to 23 V. It is important to use capacitors rated at 35 V or higher for the input and output capacitors.

### **ENABLE AND UNDERVOLTAGE LOCKOUT TERMINAL**

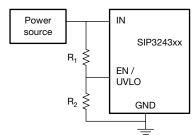

The header J13 is directly connected to the EN pin for the enable function of the device. The voltage rating of the EN pin is 28 V. The enable threshold voltage is 1.25 V and the disable threshold voltage is 1.05 V. A user-defined undervoltage protection can be implemented with a voltage divider (Fig. 3)

Fig. 3 - Settable Undervoltage Protection With Designs

## **PG, POWER GOOD OUTPUT**

The SiP32433A, SiP32433B, SiP32434A, and SiP32434B devices have power good output to indicate their operation. PG is an open drain output pin. When there is no fault, and  $V_{OUT}$  reaches 95 % of  $V_{IN}$ , the PG is off. The header J11 is connected to the PG of the device. An external bias voltage can be applied on header J3. The voltage rating of the power good is 28 V maximum. The pull-high resistor connects it to the  $V_{IN}$  through the J4 jumper when using the  $V_{IN}$  as a PG high bias voltage source.

### **OVERCURRENT LIMIT SETTING**

One of the key features of the devices is they provide overcurrent limit protection. The SiP32433A's and SiP32433B's current limit setting resistor  $R_{SFT}$  can be calculated by the below formula.

$$R_{SET} = \frac{0.6 \text{ V}}{I_{LIM}} \times 10 300$$

The SiP32434A's and SiP32434B's RSET follows the formula below:

$$R_{SET} = \frac{0.6 \text{ V}}{I_{LIM}} \times 20 600$$

- $\bullet$   $R_{SET}$  is paralleled  $R_{5}$  and  $R_{6}$  on the board

- I<sub>LIM</sub> is the target current limit setting

### PROGRAMMABLE SOFT POWER UP

During soft start, the devices control the output voltage to follow the voltage ramp on the SS pin.

$$V_{OUT} = \frac{I_{INRUSH} \times t_{SS}}{C_{OUT}}$$

The output slew rate (SR) and its set capacitor, C<sub>SS</sub>, can be calculated by the following formulas:

$$C_{SS} = \frac{I_{SS} \times 9}{SR}$$

#### Where:

- t<sub>SS</sub> is the soft power up time

- $I_{SS}$  is the built-in current to charge up the  $C_{SS}$ ; the value is 4.5  $\mu A$

- C<sub>SS</sub> is the soft power setting capacitor shown as C<sub>9</sub> on the board

- R<sub>SET</sub> is the current limit resistor

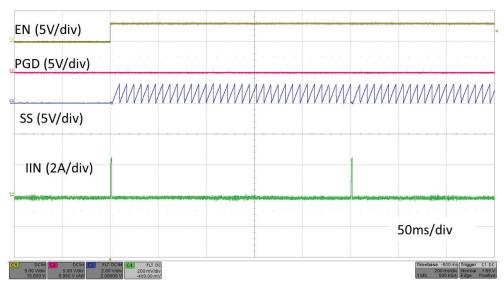

### **HOT-PLUG TEST**

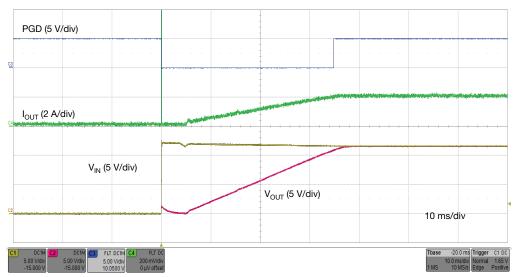

Connect J3 to an external 5 V power source as the PG bias source.

Hot-plug the power supply between J7 and J14.

Fig. 4 - An Example of Inrush Current Captured on the SiP32433 Series eFuse Evaluation Board

## **CURRENT LIMIT TEST**

Connect and turn on the power supply.

Slowly increase the load current. The switch turns off after 6 ms at the set current limit clamping level.

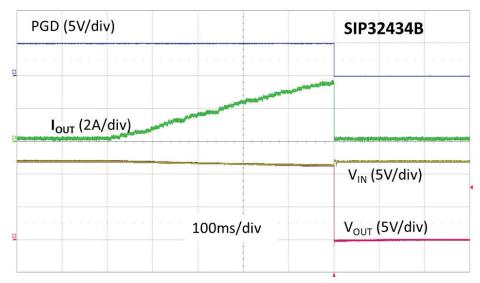

Fig. 5 - An Example of Overcurrent Protection Captured on the SiP32434 eFuse Evaluation Board

### **OUTPUT SHORT TEST**

Short the output through the on-board MOSFET by pulling J12 high.

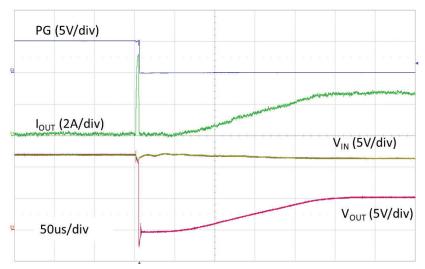

Fig. 6 - An Example of Output Short Protection Captured on the SiP32433 eFuse Evaluation Board

Fig. 7 - An Example of Auto Retry Into an Output Short Condition

## **EVALUATION BOARD LAYOUT AND PROPOSED LAYOUT GUIDELINES**

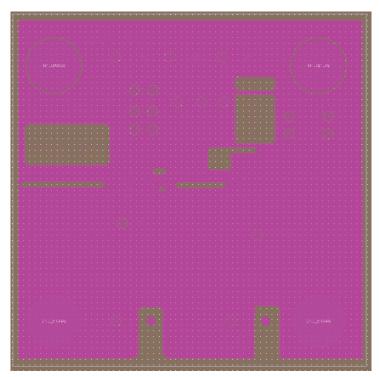

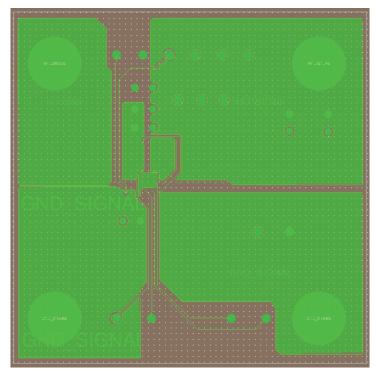

Fig. 8 to Fig. 11 show component placement and PCB layouts.

Fig. 8 - SiP3243xxEVB Board Top Layer

Fig. 9 - SiP3243xxEVB Board Bottom Layer

Fig. 10 - SiP3243xxEVB Board Inner 1 Layer

Fig. 11 - SiP3243xxEVB Board Inner 2 Layer

## **BILL OF MATERIALS**

Table 3 lists the evaluation board bill of materials (BOM).

| SYM. NAME            | COMP. VALUE        | QUANTITY | REFDES                                                 | MANUFACTURE PART NUMBER |  |

|----------------------|--------------------|----------|--------------------------------------------------------|-------------------------|--|

| BANANA Banana        |                    | 4        | J7; J8; J14; J16                                       | 36-575-4-ND             |  |

| C0603-TDK 47 nF      |                    | 1        | C9                                                     | 399-17881-2-ND          |  |

| C1210-TDK 10 uF, 50  |                    | 8        | C1; C2; C3; C4; C5; C6; C7; C8                         | 445-14933-2-ND          |  |

| DO-214               | SSA23L             | 1        | D2                                                     | SSA23L-E3/61TGITR-ND    |  |

| DO-221AC             | SMA6F24A           | 1        | D1                                                     | DNP                     |  |

| JUMPER2              | JUMPER             | 5        | J4; J9; J10; J17; J26                                  | TSW-102-07-L-S          |  |

| JUMPER2              | CON2               | 1        | J24                                                    | TSW-102-07-L-S          |  |

| MLP33-11A IC         |                    | 1        | U1                                                     | SiP3243xx               |  |

| MOSPOWERPAKSO8 SIRAO |                    | 1        | Q1                                                     | SIRA00DP-T1-GE3TR-ND    |  |

| R0603-VISHAY 51 kΩ   |                    | 1        | R2                                                     | 541-5465-2-ND           |  |

| R0603-VISHAY DNP     |                    | 1        | R4                                                     | DNP                     |  |

| R0603-VISHAY DNP     |                    | 1        | R8                                                     | DNP                     |  |

| R0603-VISHAY 12.4 kΩ |                    | 1        | R5                                                     | A140147TR-ND            |  |

| R0603-VISHAY         | 2.05 kΩ            | 1        | R6                                                     | A140445TR-ND            |  |

| R0603-VISHAY         | DNP                | 1        | R7                                                     | DNP                     |  |

| R0603-VISHAY         | 1 kΩ               | 1        | R9                                                     | 541-1.00KHTR-ND         |  |

| R0603-VISHAY         | DNP                | 1        | R10                                                    | DNP                     |  |

| R0805-VISHAY         | 10 Ω               | 1        | R1                                                     | CRCW080510R0FKEB        |  |

| R0805-VISHAY         | 100 kΩ             | 1        | R3                                                     | 541-3950-2-ND           |  |

| R1206-VISHAY         | DNP                | 1        | RL1                                                    | DNP                     |  |

| R1206-VISHAY 25 mΩ   |                    | 1        | R <sub>SENSE</sub>                                     | CSR1206FK25L0TR-ND      |  |

| R2512-VISHAY         | R2512-VISHAY DNP   |          | RL2; RL3                                               | DNP                     |  |

| TP30                 | CON1               | 11       | J1; J3; J11; J12; J13; J20;<br>J21; J22; J23; J25; J27 |                         |  |

| TP30                 | V <sub>IN_S</sub>  | 1        | J5                                                     |                         |  |

| TP30                 | V <sub>OUT_S</sub> |          | J6                                                     | 36-5002-ND              |  |

| TP30                 | GND <sub>S</sub>   | 1        | J18                                                    |                         |  |

| TP30                 | GNS <sub>S</sub>   | 1        | J19                                                    |                         |  |

## **LAYOUT GUIDELINES**

The SiP32434A and SiP32434B are protection switches designed to maintain a constant output load current upon overcurrent faults. An optimized layout with efficient heat sinking is critical. It is recommended to put as much copper as possible on the devices' central exposed pad, which is connected to ground. Connect all ground planes with all possible thermal VIAs. The circuit setting components should be laid close to their connection pins. The components include a current limit setting resistor, soft start setting capacitor, and resistors connected to EN / UVLO and OVP pins.

Protection devices such as an input TVS or output Schottky diode must be located close to the pins to be protected, and routed with short traces to reduce inductance.

Below is a layout example.

Fig. 12

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?62068">www.vishay.com/ppg?62068</a>.