For details on Vishay Siliconix MOSFETs, visit www.vishay.com/mosfets/

## LITTLE FOOT® TSSOP-8 The Next Step in Surface-Mount Power MOSFETs

Wharton McDaniel and David Oldham

When Vishay Siliconix introduced its LITTLE FOOT MOSFETs, it was the first time that power MOSFETs had been offered in a true surface-mount package, the SOIC. LITTLE FOOT immediately found a home in new small form factor disk drives, computers, and cellular phones.

The new LITTLE FOOT TSSOP-8 power MOSFETs are the natural evolutionary response to the continuing demands of many markets for smaller and smaller packages. LITTLE FOOT TSSOP-8 MOSFETs have a smaller footprint and a lower profile than LITTLE FOOT SOICs, while maintaining low  $r_{DS(on)}$  and high thermal performance. Vishay Siliconix has accomplished this by putting one or two high-density MOSFET die in a standard 8-pin TSSOP package mounted on a custom leadframe.

This is the low profile demanded by applications such as PCMCIA cards.

It reduces the power package to the same height as many resistors and capacitors in 0805 and 0605 sizes. It also allows placement on the "passive" side of the PC board.

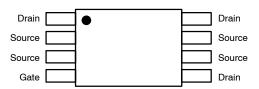

The standard pinouts of the LITTLE FOOT TSSOP-8 packages have been changed from the standard established by LITTLE FOOT. This change minimizes the contribution of interconnection resistance to  $r_{DS(on)}$  and maximizes the transfer of heat out of the package.

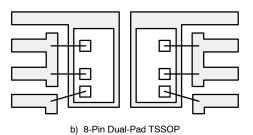

Figure 2 shows the pinouts for a single-die TSSOP. Notice that both sides of the package have Source and Drain connections, whereas LITTLE FOOT has the Source and Gate connections on one side of the package, and the Drain connections are on the opposite side.

### THE TSSOP-8 PACKAGE

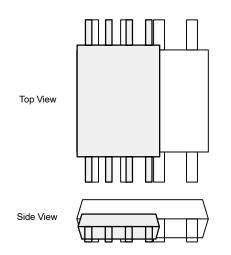

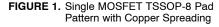

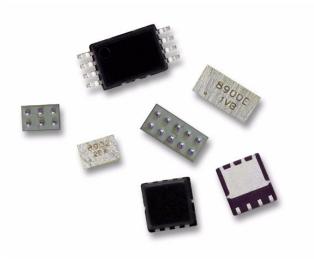

LITTLE FOOT TSSOP-8 power MOSFETs require approximately half the PC board area of an equivalent LITTLE FOOT device (Figure 1). In addition to the reduction in board area, the package height has been reduced to 1.1 mm.

Figure 1. An TSSOP-8 Package Next to a SOIC-8 Package with Views from Both Top and Side

Figure 2. Pinouts for Single Die TSSOP

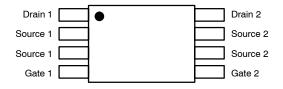

Figure 3 shows the standard pinouts for a dual-die TSSOP-8. In this case, the connections for each individual MOSFET occupy one side.

Figure 3. Pinouts for Dual-Die TSSOP

## AN1001

### **Vishay Siliconix**

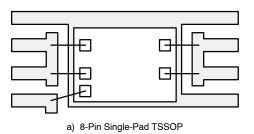

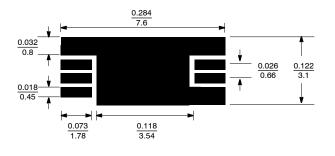

Because the TSSOP has a fine pitch foot print, the pad layout is somewhat more demanding than the layout of the SOIC. Careful attention must be paid to silkscreen-to-pad and soldermask-to-pad clearances. Also, fiduciary marks may be required. The design and spacing of the pads must be dealt with carefully. The pads must be sized to hold enough solder paste to form a good joint, but should not be so large or so placed as to extend under the body, increasing the potential for solder bridging. The pad pattern should allow for typical pick and place errors of 0.25 mm. See Application Note 826, Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs. (http://www.vishay.com/doc?72286), for the recommended pad pattern for PC board layout.

### THERMAL ISSUES

LITTLE FOOT TSSOP MOSFETs have been given thermal ratings using the same methods used for LITTLE FOOT. The maximum thermal resistance junction-to-ambient is 83°C/W for the single die and 125°C/W for dual-die parts. TSSOP relies on a leadframe similar to LITTLE FOOT to remove heat from the package. The single- and dual-die leadframes are shown in Figure 4.

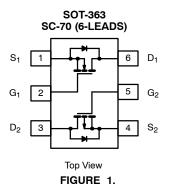

Figure 4. Leadframe

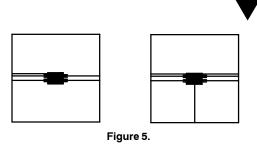

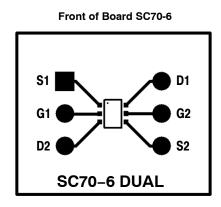

The MOSFETs are characterized using a single pulse power test. For this test the device mounted on a one-square-inch piece of copper clad FR-4 PC board, such as those shown in Figure 5. The single pulse power test determines the maximum amount of power the part can handle for a given pulse width and defines the thermal resistance junction-to-ambient. The test is run for pulse widths ranging from approximately 10 ms to 100 seconds. The thermal resistance at 30 seconds is the rated thermal resistance for the part. This rating was chosen to allow comparison of packages and leadframes. At longer pulse widths, the PC board thermal charateristics become dominant, making all parts look the same.

The actual test is based on dissipating a known amount of power in the device for a known period of time so the junction temperature is raised to  $150^{\circ}$ C. The starting and ending junction temperatures are determined by measuring the forward drop of the body diode. The thermal resistance for that pulse width is defined by the temperature rise of the junction above ambient and the power of the pulse,  $\Delta$ Tja/P.

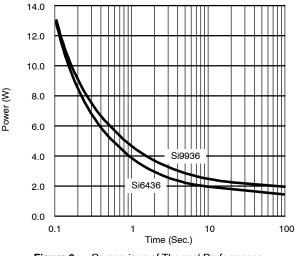

Figure 6 shows the single pulse power curve of the Si6436DQ laid over the curve of the Si9936DY to give a comparison of the thermal performance. The die in the two devices have equivalent die areas, making this a comparison of the packaging. This comparison shows that the TSSOP package performs as well as the SOIC out to 150 ms, with long-term performance being 0.5 W less. Although the thermal performance is less, LITTLE FOOT TSSOP will operate in a large percentage of applications that are currently being served by LITTLE FOOT.

Figure 6. Comparison of Thermal Performance

### CONCLUSION

TSSOP power MOSFETs provide a significant reduction in PC board footprint and package height, allowing reduction in board size and application where SOICs will not fit. This is accomplished using a standard IC package and a custom leadframe, combining small size with good power handling capability.

For the TSSOP-8 package outline visit: http://www.vishay.com/doc?71201

For the SOIC-8 package outline visit: http://www.vishay.com/doc?71192

## Mounting LITTLE FOOT<sup>®</sup> TSSOP-8 Power MOSFETs

Wharton McDaniel

Surface-mounted LITTLE FOOT power MOSFETs use integrated circuit and small-signal packages which have been been modified to provide the heat transfer capabilities required by power devices. Leadframe materials and design, molding compounds, and die attach materials have been changed, while the footprint of the packages remains the same.

See Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFET*, (http://www.vishay.com/doc?72286), for the basis of the pad design for a LITTLE FOOT TSSOP-8 power MOSFET package footprint. In converting the footprint to the pad set for a power device, designers must make two connections: an electrical connection and a thermal connection, to draw heat away from the package.

In the case of the TSSOP-8 package, the thermal connections are very simple. Pins 1, 5, and 8 are the drain of the MOSFET for a single MOSFET package and are connected together. In the dual package, pins 1 and 8 are the two drains. For a small-signal device or integrated circuit, typical connections would be made with traces that are 0.020 inches wide. Since the drain pins also provide the thermal connection to the package, this level of connection is inadequate. The total cross section of the copper may be adequate to carry the current required for the application, but it presents a large thermal impedance. Also, heat spreads in a circular fashion from the heat source. In this case the drain pins are the heat sources when looking at heat spread on the PC board.

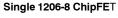

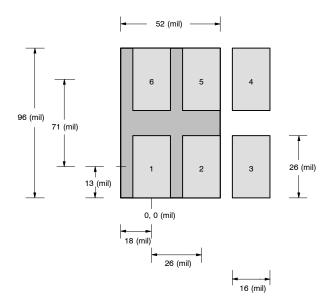

The pad patterns with copper spreading for the single-MOSFET TSSOP-8 (Figure 1) and dual-MOSFET TSSOP-8 (Figure 2) show the starting point for utilizing the board area available for the heat-spreading copper. To create this pattern, a plane of copper overlies the drain pins. The copper plane connects the drain pins electrically, but more importantly provides planar copper to draw heat from the drain leads and start the process of spreading the heat so it can be dissipated into the ambient air. These patterns use all the available area underneath the body for this purpose.

FIGURE 2. Dual MOSFET TSSOP-8 Pad Pattern with Copper Spreading

Since surface-mounted packages are small, and reflow soldering is the most common way in which these are affixed to the PC board, "thermal" connections from the planar copper to the pads have not been used. Even if additional planar copper area is used, there should be no problems in the soldering process. The actual solder connections are defined by the solder mask openings. By combining the basic footprint with the copper plane on the drain pins, the solder mask generation occurs automatically.

A final item to keep in mind is the width of the power traces. The absolute minimum power trace width must be determined by the amount of current it has to carry. For thermal reasons, this minimum width should be at least 0.020 inches. The use of wide traces connected to the drain plane provides a low impedance path for heat to move away from the device.

### Single-Channel 1206-8 ChipFET<sup>®</sup> Power MOSFET Recommended Pad Pattern and Thermal Performance

### INTRODUCTION

New Vishay Siliconix ChipFETs in the leadless 1206-8 package feature the same outline as popular 1206-8 resistors and capacitors but provide all the performance of true power semiconductor devices. The 1206-8 ChipFET has the same footprint as the body of the LITTLE FOOT® TSOP-6, and can be thought of as a leadless TSOP-6 for purposes of visualizing board area, but its thermal performance bears comparison with the much larger SO-8.

This technical note discusses the single-channel ChipFET 1206-8 pin-out, package outline, pad patterns, evaluation board layout, and thermal performance.

### **PIN-OUT**

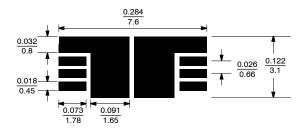

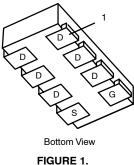

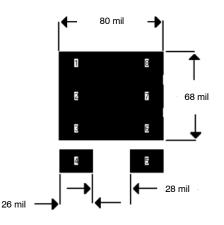

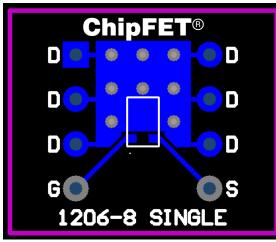

Figure 1 shows the pin-out description and Pin 1 identification for the single-channel 1206-8 ChipFET device. The pin-out is similar to the TSOP-6 configuration, with two additional drain pins to enhance power dissipation and thermal performance. The legs of the device are very short, again helping to reduce the thermal path to the external heatsink/pcb and allowing a larger die to be fitted in the device if necessary.

For package dimensions see the 1206-8 ChipFET package outline drawing (http://www.vishay.com/doc?71151).

### **BASIC PAD PATTERNS**

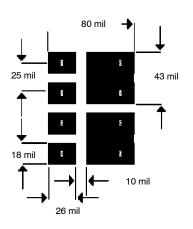

The basic pad layout with dimensions is shown in Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*, (http://www.vishay.com/doc?72286). This is sufficient for low power dissipation MOSFET applications, but power semiconductor performance requires a greater copper pad area, particularly for the drain leads.

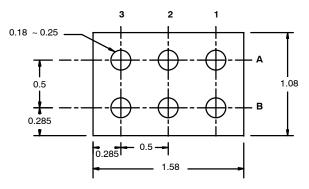

FIGURE 2. Footprint With Copper Spreading

The pad pattern with copper spreading shown in Figure 2 improves the thermal area of the drain connections (pins 1,2,3,6.7,8) while remaining within the confines of the basic footprint. The drain copper area is 0.0054 sq. in. or 3.51 sq. mm). This will assist the power dissipation path away from the device (through the copper leadframe) and into the board and exterior chassis (if applicable) for the single device. The addition of a further copper area and/or the addition of vias to other board layers will enhance the performance still further. An example of this method is implemented on the Vishay Siliconix Evaluation Board described in the next section (Figure 3).

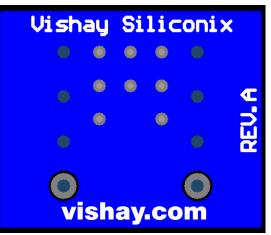

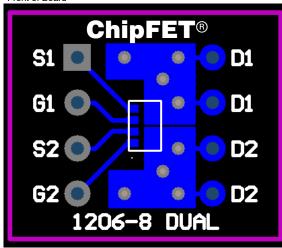

### THE VISHAY SILICONIX EVALUATION BOARD FOR THE SINGLE 1206-8

The ChipFET 1206-08 evaluation board measures 0.6 in by 0.5 in. Its copper pad pattern consists of an increased pad area around the six drain leads on the top-side—approximately 0.0482 sq. in. 31.1 sq. mm—and vias added through to the underside of the board, again with a maximized copper pad area of approximately the board-size dimensions. The outer package outline is for the 8-pin DIP, which will allow test sockets to be used to assist in testing.

The thermal performance of the 1206-8 on this board has been measured with the results following on the next page. The testing included comparison with the minimum recommended footprint on the evaluation board-size pcb and the industry standard one-inch square FR4 pcb with copper on both sides of the board.

## AN811 Vishay Siliconix

Front of Board

Back of Board

FIGURE 3.

### THERMAL PERFORMANCE

# Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the 1206-8 ChipFET measured as junction-to-foot thermal resistance is 15° C/W typical, 20° C/W maximum for the single device. The "foot" is the drain lead of the device as it connects with the body. This is identical to the SO-8 package  $R_{\Theta j \bar{f}}$  performance, a feat made possible by shortening the leads to the point where they become only a small part of the total footprint area.

# Junction-to-Ambient Thermal Resistance (dependent on pcb size)

The typical  $R_{\Theta ja}$  for the single-channel 1206-8 ChipFET is 80°C/W steady state, compared with 68°C/W for the SO-8. Maximum ratings are 95°C/W for the 1206-8 versus 80°C/W for the SO-8.

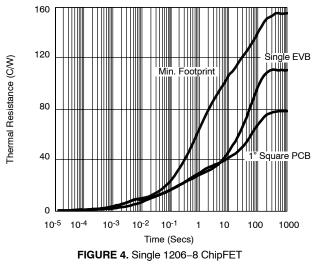

#### Testing

To aid comparison further, Figure 4 illustrates ChipFET 1206-8 thermal performance on two different board sizes and three different pad patterns. The results display the thermal performance out to steady state and produce a graphic account of how an increased copper pad area for the drain connections can enhance thermal performance. The measured steady state values of  $R_{\Theta ja}$  for the single 1206-8 ChipFET are :

| 1) Minimum recommended pad pattern (see<br>Figure 2) on the evaluation board size of<br>0.5 in x 0.6 in. | 156°C/W |

|----------------------------------------------------------------------------------------------------------|---------|

| 2) The evaluation board with the pad pattern described on Figure 3.                                      | 111°C/W |

| 3) Industry standard 1" square pcb with maximum copper both sides.                                       | 78°C/W  |

The results show that a major reduction can be made in the thermal resistance by increasing the copper drain area. In this example, a  $45^{\circ}$ C/W reduction was achieved without having to increase the size of the board. If increasing board size is an option, a further  $33^{\circ}$ C/W reduction was obtained by maximizing the copper from the drain on the larger 1" square pcb.

### SUMMARY

The thermal results for the single-channel 1206-8 ChipFET package display similar power dissipation performance to the SO-8 with a footprint reduction of 80%. Careful design of the package has allowed for this performance to be achieved. The short leads allow the die size to be maximized and thermal resistance to be reduced within the confines of the TSOP-6 body size.

### ASSOCIATED DOCUMENT

1206-8 ChipFET Dual Thermal performance, AN812 (http://www.vishay.com/doc?71127).

## Dual-Channel 1206-8 ChipFET<sup>®</sup> Power MOSFET Recommended Pad Pattern and Thermal Performance

### INTRODUCTION

New Vishay Siliconix ChipFETs in the leadless 1206-8 package feature the same outline as popular 1206-8 resistors and capacitors but provide all the performance of true power semiconductor devices. The 1206-8 ChipFET has the same footprint as the body of the LITTLE FOOT® TSOP-6, and can be thought of as a leadless TSOP-6 for purposes of visualizing board area, but its thermal performance bears comparison with the much larger SO-8.

This technical note discusses the dual ChipFET 1206-8 pin-out, package outline, pad patterns, evaluation board layout, and thermal performance.

### **PIN-OUT**

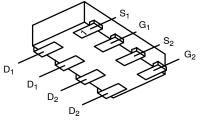

Figure 1 shows the pin-out description and Pin 1 identification for the dual-channel 1206-8 ChipFET device. The pin-out is similar to the TSOP-6 configuration, with two additional drain pins to enhance power dissipation and thus thermal performance. The legs of the device are very short, again helping to reduce the thermal path to the external heatsink/pcb and allowing a larger die to be fitted in the device if necessary.

Dual 1206-8 ChipFET

FIGURE 1.

For package dimensions see the 1206-8 ChipFET package outline drawing (http://www.vishay.com/doc?71151).

### **BASIC PAD PATTERNS**

The basic pad layout with dimensions is shown in Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*, (http://www.vishay.com/doc?72286). This is sufficient for low power dissipation MOSFET applications, but power semiconductor performance requires a greater copper pad area, particularly for the drain leads.

FIGURE 2. Footprint With Copper Spreading

The pad pattern with copper spreading shown in Figure 2 improves the thermal area of the drain connections (pins 5 and 6, pins 7 and 8) while remaining within the confines of the basic footprint. The drain copper area is 0.0019 sq. in. or 1.22 sq. mm. This will assist the power dissipation path away from the device (through the copper leadframe) and into the board and exterior chassis (if applicable) for the dual device. The addition of a further copper area and/or the addition of vias to other board layers will enhance the performance still further. An example of this method is implemented on the Vishay Siliconix Evaluation Board described in the next section (Figure 3).

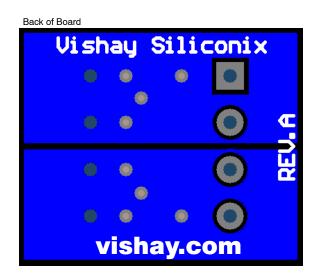

### THE VISHAY SILICONIX EVALUATION BOARD FOR THE DUAL 1206-8

The dual ChipFET 1206-08 evaluation board measures 0.6 in by 0.5 in. Its copper pad pattern consists of an increased pad area around each of the two drain leads on the top-side approximately 0.0246 sq. in. or 15.87 sq. mm—and vias added through to the underside of the board, again with a maximized copper pad area of approximately the board-size dimensions, split into two for each of the drains. The outer package outline is for the 8-pin DIP, which will allow test sockets to be used to assist in testing.

The thermal performance of the 1206-8 on this board has been measured with the results following on the next page. The testing included comparison with the minimum recommended footprint on the evaluation board-size pcb and the industry standard one-inch square FR4 pcb with copper on both sides of the board.

## AN812 Vishay Siliconix

Front of Board

### THERMAL PERFORMANCE

## Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the 1206-8 ChipFET measured as junction-to-foot thermal resistance is 30°C/W typical, 40°C/W maximum for the dual device. The "foot" is the drain lead of the device as it connects with the body. This is identical to the dual SO-8 package  $R_{\Theta jf}$  performance, a feat made possible by shortening the leads to the point where they become only a small part of the total footprint area.

# Junction-to-Ambient Thermal Resistance (dependent on pcb size)

The typical  $R_{\Theta ja}$  for the dual-channel 1206-8 ChipFET is 90°C/W steady state, identical to the SO-8. Maximum ratings are 110°C/W for both the 1206-8 and the SO-8. Both packages have comparable thermal performance on the 1" square pcb footprint with the 1206-8 dual package having a quarter of the body area, a significant factor when considering board area.

#### Testing

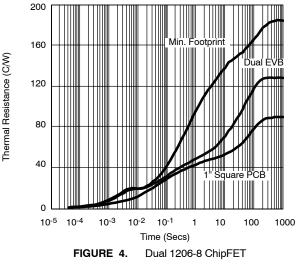

To aid comparison further, Figure 4 illustrates ChipFET 1206-8 dual thermal performance on two different board sizes and three different pad patterns. The results display the thermal performance out to steady state and produce a graphic account on how an increased copper pad area for the drain connections can enhance thermal performance. The measured steady state values of  $R_{\Theta\,j\,a}$  for the Dual 1206-8 ChipFET are :

| 1) Minimum recommended pad pattern (see<br>Figure 2) on the evaluation board size of<br>0.5 in x 0.6 in. | 185°C/W |

|----------------------------------------------------------------------------------------------------------|---------|

| 2) The evaluation board with the pad pattern described on Figure 3.                                      | 128°C/W |

| 3) Industry standard 1" square pcb with maximum copper both sides.                                       | 90°C/W  |

The results show that a major reduction can be made in the thermal resistance by increasing the copper drain area. In this example, a  $57^{\circ}$  C/W reduction was achieved without having to increase the size of the board. If increasing board size is an option, a further  $38^{\circ}$  C/W reduction was obtained by maximizing the copper from the drain on the larger 1" square PCB.

### SUMMARY

The thermal results for the dual-channel 1206-8 ChipFET package display identical power dissipation performance to the SO-8 with a footprint reduction of 80%. Careful design of the package has allowed for this performance to be achieved. The short leads allow the die size to be maximized and thermal resistance to be reduced within the confines of the TSOP-6 body size.

### **ASSOCIATED DOCUMENT**

1206-8 ChipFET Single Thermal performance, AN811, (http://www.vishay.com/doc?71126).

## Single-Channel LITTLE FOOT® SC-70 3-Pin and 6-Pin MOSFET Recommended Pad Pattern and Thermal Peformance

### INTRODUCTION

This technical note discusses pin-outs, package outlines, pad patterns, evaluation board layout, and thermal performance for single-channel LITTLE FOOT power MOSFETs in the SC-70 package. These new Vishay Siliconix devices are intended for small-signal applications where a miniaturized package is needed and low levels of current (around 350 mA) need to be switched, either directly or by using a level shift configuration. Vishay provides these single devices with a range of on-resistance specifications and in both traditional 3-pin and new 6-pin versions. The new 6-pin SC-70 package enables improved on-resistance values and enhanced thermal performance compared to the 3-pin package.

### **PIN-OUT**

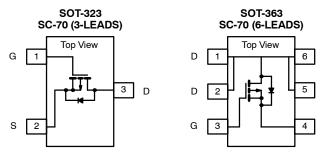

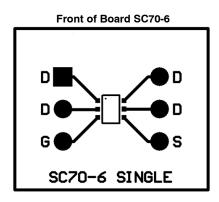

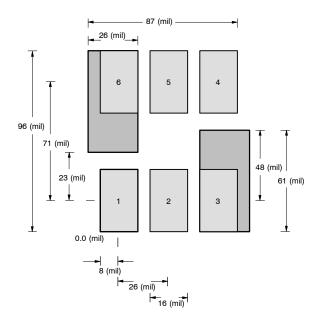

Figure 1 shows the pin-out description and Pin 1 identification for the single-channel SC-70 device in both 3-pin and 6-pin configurations. The pin-out of the 6-pin device allows the use of four pins as drain leads, which helps to reduce on-resistance and junction-to-ambient thermal resistance.

#### FIGURE 1.

For package dimensions see outline drawings: SC-70 (3-Leads) (http://www.vishay.com/doc?71153) SC-70 (6-Leads) (http://www.vishay.com/doc?71154)

###

FIGURE 2.

vishay.com

### **BASIC PAD PATTERNS**

See Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*, (http://www.vishay.com/doc?72286) for the basic pad layout and dimensions for the 3-pin SC-70 and the 6-pin SC-70. These pad patterns are sufficient for the low-power applications for which this package is intended. Increasing the pad pattern has little effect on thermal resistance for the 3-pin device, reducing it by only 10% to 15%. But for the 6-pin device, increasing the pad patterns yields a reduction in thermal resistance on the order of 35% when using a 1-inch square with full copper on both sides of the printed circuit board (PCB). The availability of four drain leads rather than the traditional single drain lead allows a better thermal path from the package to the PCB and external environment.

# EVALUATION BOARDS FOR THE SINGLE SC70-3 AND SC70-6

Figure 2 shows the 3-pin and 6-pin SC-70 evaluation boards (EVB). Both measure 0.6 inches by 0.5 inches. Their copper pad traces are the same as described in the previous section, *Basic Pad Patterns*. Both boards allow interrogation from the outer pins to 6-pin DIP connections, permitting test sockets to be used in evaluation testing.

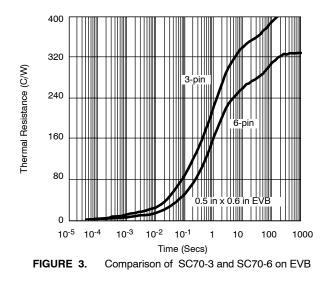

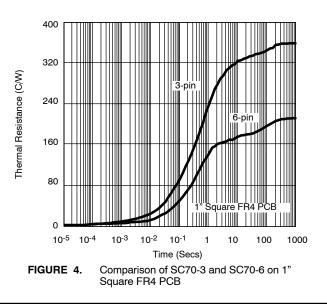

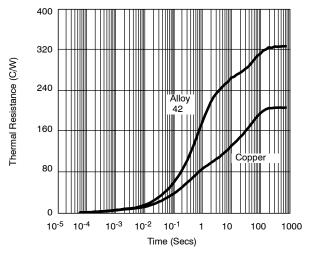

The thermal performance of the single SC-70 has been measured on the EVB for both the 3-pin and 6-pin devices, the results shown in Figures 3 and 4. The minimum recommended footprint on the evaluation board was compared with the industry standard of 1-inch square FR4 PCB with copper on both sides of the board.

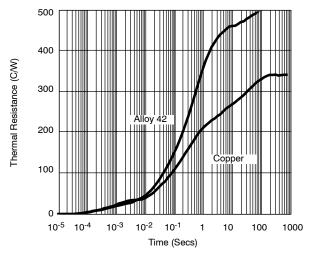

SC70-3 SINGLE

SC70-6 SINGLE

### THERMAL PERFORMANCE

# Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the 3-pin SC-70 measured as junction-to-foot thermal resistance is  $285^{\circ}$ C/W typical,  $340^{\circ}$ C/W maximum. Junction-to-foot thermal resistance for the 6-pin SC70-6 is  $105^{\circ}$ C/W typical,  $130^{\circ}$ C/W maximum — a nearly two-thirds reduction compared with the 3-pin device. The "foot" is the drain lead of the device as it connects with the body. This improved performance is obtained by the increase in drain leads from one to four on the 6-pin SC-70. Note that these numbers are somewhat higher than other LITTLE FOOT devices due to the limited thermal performance of the Alloy 42 lead-frame compared with a standard copper lead-frame.

# Junction-to-Ambient Thermal Resistance (dependent on PCB size)

The typical R $\theta_{JA}$ for the single 3-pin SC-70 is 360°C/W steady state, compared with 180°C/W for the 6-pin SC-70. Maximum ratings are 430°C/W for the 3-pin device versus 220°C/W for the 6-pin device. All figures are based on the 1-inch square FR4 test board. The following table shows how the thermal resistance impacts power dissipation for the two different pin-outs at two different ambient temperatures.

| SC-70 (3-PIN)                                                                                                 |                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Room Ambient 25 °C                                                                                            | Elevated Ambient 60 °C                                                                                        |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{360^{\circ}C/W}$ | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{360^{\circ}C/W}$ |

| $P_D = 347 \text{ mW}$                                                                                        | $P_D = 250 \text{ mW}$                                                                                        |

| SC-70 (6-PIN)                                                                                                 |                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Room Ambient 25 °C                                                                                            | Elevated Ambient 60 °C                                                                                        |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{180^{\circ}C/W}$ | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{180^{\circ}C/W}$ |

| $P_{\rm D} = 694  \rm mW$                                                                                     | $P_{\rm D} = \frac{180^{\circ} \text{C/W}}{180^{\circ} \text{C/W}}$ $P_{\rm D} = 500 \text{ mW}$              |

NOTE: Although they are intended for low-power applications, devices in the 6-pin SC-70 will handle power dissipation in excess of 0.5 W.

#### Testing

To aid comparison further, Figures 3 and 4 illustrate single-channel SC-70 thermal performance on two different board sizes and two different pad patterns. The results display the thermal performance out to steady state and produce a graphic account of the thermal performance variation between the two packages. The measured steady state values of  $R\theta_{JA}$  for the single 3-pin and 6-pin SC-70 are as follows:

| LITTLE FOOT SC-70                                                  |            |           |

|--------------------------------------------------------------------|------------|-----------|

|                                                                    | 3-Pin      | 6-Pin     |

| 1) Minimum recommended pad pattern (see Figure 4) on the EVB.      | 410.31°C/W | 329.7°C/W |

| 2) Industry standard 1" square PCB with maximum copper both sides. | 360°C/W    | 211.8°C/W |

The results show that designers can reduce thermal resistance  $R\theta_{JA}$  on the order of 20% simply by using the 6-pin device rather than the 3-pin device. In this example, a 80°C/W reduction was achieved without an increase in board area. If increasing board size is an option, a further 118°C/W reduction could be obtained by utilizing a 1-inch square PCB area.

## Dual-Channel LITTLE FOOT® SC-70 6-Pin MOSFET Recommended Pad Pattern and Thermal Performance

### INTRODUCTION

This technical note discusses the pin-outs, package outlines, pad patterns, evaluation board layout, and thermal performance for dual-channel LITTLE FOOT power MOSFETs in the SC-70 package. These new Vishay Siliconix devices are intended for small-signal applications where a miniaturized package is needed and low levels of current (around 250 mA) need to be switched, either directly or by using a level shift configuration. Vishay provides these devices with a range of on-resistance specifications in 6-pin versions. The new 6-pin SC-70 package enables improved on-resistance values and enhanced thermal performance.

### **PIN-OUT**

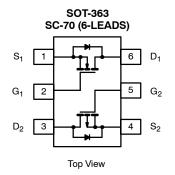

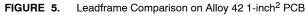

Figure 1 shows the pin-out description and Pin 1 identification for the dual-channel SC-70 device in the 6-pin configuration.

For package dimensions see outline drawing SC-70 (6-Leads) (http://www.vishay.com/doc?71154)

### **BASIC PAD PATTERNS**

See Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFET*s, (http://www.vishay.com/doc?72286) for the 6-pin SC-70. This basic pad pattern is sufficient for the low-power applications for which this package is intended. For the 6-pin device, increasing the pad patterns yields a reduction in thermal resistance on the order of 20% when using a 1-inch square with full copper on both sides of the printed circuit board (PCB).

# EVALUATION BOARDS FOR THE DUAL SC70-6

The 6-pin SC-70 evaluation board (EVB) measures 0.6 inches by 0.5 inches. The copper pad traces are the same as described in the previous section, *Basic Pad Patterns*. The board allows interrogation from the outer pins to 6-pin DIP connections permitting test sockets to be used in evaluation testing.

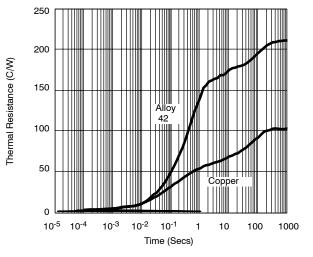

The thermal performance of the dual SC-70 has been measured on the EVB with the results shown below. The minimum recommended footprint on the evaluation board was compared with the industry standard 1-inch square FR4 PCB with copper on both sides of the board.

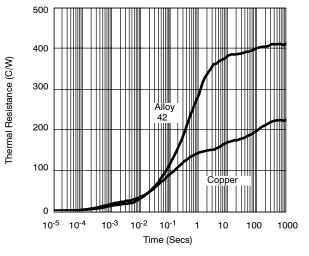

#### THERMAL PERFORMANCE

## Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the dual SC-70 6-pin package measured as junction-to-foot thermal resistance is 300°C/W typical, 350°C/W maximum. The "foot" is the drain lead of the device as it connects with the body. Note that these numbers are somewhat higher than other LITTLE FOOT devices due to the limited thermal performance of the Alloy 42 lead-frame compared with a standard copper lead-frame.

## Junction-to-Ambient Thermal Resistance (dependent on PCB size)

The typical R $\theta_{JA}$  for the dual 6-pin SC-70 is 400°C/W steady state. Maximum ratings are 460°C/W for the dual. All figures based on the 1-inch square FR4 test board. The following example shows how the thermal resistance impacts power dissipation for the dual 6-pin SC-70 package at two different ambient temperatures.

| SC-70 (6-PIN)                                               |                                                                |  |

|-------------------------------------------------------------|----------------------------------------------------------------|--|

| Room Ambient 25 °C                                          | Elevated Ambient 60 °C                                         |  |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\boldsymbol{\theta}_{JA}}$ |  |

| $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{400^{\circ}C/W}$ | $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{400^{\circ}C/W}$    |  |

| $P_D = 312 \text{ mW}$                                      | $P_D = 225 \text{ mW}$                                         |  |

NOTE: Although they are intended for low-power applications, devices in the 6-pin SC-70 will handle power dissipation in excess of 0.2 W.

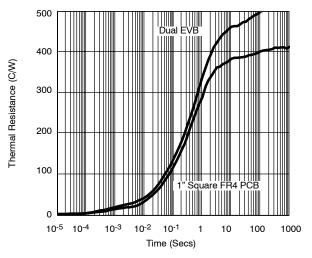

### Testing

To aid comparison further, Figure 2 illustrates the dual-channel SC-70 thermal performance on two different board sizes and two different pad patterns. The results display the thermal performance out to steady state. The measured steady state values of  $R\theta_{JA}$  for the dual 6-pin SC-70 are as follows:

| LITTLE FOOT SC-70 (6-PIN)                                                                      |         |

|------------------------------------------------------------------------------------------------|---------|

| 1) Minimum recommended pad pattern (see<br>Figure 2) on the EVB of 0.5 inches x<br>0.6 inches. | 518°C/W |

| 2) Industry standard 1" square PCB with maximum copper both sides.                             | 413°C/W |

FIGURE 2. Comparison of Dual SC70-6 on EVB and 1" Square FR4 PCB.

The results show that if the board area can be increased and maximum copper traces are added, the thermal resistance reduction is limited to 20%. This fact confirms that the power dissipation is restricted with the package size and the Alloy 42 leadframe.

### **ASSOCIATED DOCUMENT**

Single-Channel LITTLE FOOT SC-70 6-Pin MOSFET Copper Leadframe Version, REcommended Pad Pattern and Thermal Performance, AN815, (http://www.vishay.com/doc?71334).

## Single-Channel LITTLE FOOT® SC-70 6-Pin MOSFET Copper Leadframe Version Recommended Pad Pattern and Thermal Performance

### INTRODUCTION

The new single 6-pin SC-70 package with a copper leadframe enables improved on-resistance values and enhanced thermal performance as compared to the existing 3-pin and 6-pin packages with Alloy 42 leadframes. These devices are intended for small to medium load applications where a miniaturized package is required. Devices in this package come in a range of on-resistance values, in n-channel and p-channel versions. This technical note discusses pin-outs, package outlines, pad patterns, evaluation board layout, and thermal performance for the single-channel version.

### **BASIC PAD PATTERNS**

See Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*, (http://www.vishay.com/doc?72286) for the basic pad layout and dimensions. These pad patterns are sufficient for the low to medium power applications for which this package is intended. Increasing the drain pad pattern yields a reduction in thermal resistance and is a preferred footprint. The availability of four drain leads rather than the traditional single drain lead allows a better thermal path from the package to the PCB and external environment.

### **PIN-OUT**

Figure 1 shows the pin-out description and Pin 1 identification. The pin-out of this device allows the use of four pins as drain leads, which helps to reduce on-resistance and junction-to-ambient thermal resistance.

FIGURE 1.

For package dimensions see outline drawing SC-70 (6-Leads) (http://www.vishay.com/doc?71154)

### **EVALUATION BOARDS — SINGLE SC70-6**

The evaluation board (EVB) measures 0.6 inches by 0.5 inches. The copper pad traces are the same as in Figure 2. The board allows examination from the outer pins to 6-pin DIP connections, permitting test sockets to be used in evaluation testing. See Figure 3.

FIGURE 2. SC-70 (6 leads) Single

The thermal performance of the single 6-pin SC-70 has been measured on the EVB, comparing both the copper and Alloy 42 leadframes. This test was first conducted on the traditional Alloy 42 leadframe and was then repeated using the 1-inch<sup>2</sup> PCB with dual-side copper coating.

## AN815 Vishay Siliconix

FIGURE 3.

### THERMAL PERFORMANCE

# Junction-to-Foot Thermal Resistance (Package Performance)

The junction to foot thermal resistance is a useful method of comparing different packages thermal performance.

A helpful way of presenting the thermal performance of the 6-Pin SC-70 copper leadframe device is to compare it to the traditional Alloy 42 version.

Thermal performance for the 6-pin SC-70 measured as junction-to-foot thermal resistance, where the "foot" is the drain lead of the device at the bottom where it meets the PCB. The junction-to-foot thermal resistance is typically 40°C/W in the copper leadframe and 163°C/W in the Alloy 42 leadframe — a four-fold improvement. This improved performance is obtained by the enhanced thermal conductivity of copper over Alloy 42.

### **Power Dissipation**

The typical R $\theta_{JA}$  for the single 6-pin SC-70 with copper leadframe is 103°C/W steady-state, compared with 212°C/W for the Alloy 42 version. The figures are based on the 1-inch<sup>2</sup> FR4 test board. The following example shows how the thermal resistance impacts power dissipation for the two different leadframes at varying ambient temperatures.

| ALLOY 42 LEADFRAME                                          |                                                             |

|-------------------------------------------------------------|-------------------------------------------------------------|

| Room Ambient 25 °C                                          | Elevated Ambient 60 °C                                      |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           |

| $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{212^{\circ}C/W}$ | $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{212^{\circ}C/W}$ |

| $P_D = 590 \text{ mW}$                                      | $P_{D} = 425 \text{ mW}$                                    |

| COOPER LEADFRAME                                                                                              |                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Room Ambient 25 $^{\circ}$ C                                                                                  | Elevated Ambient 60 °C                                                                                        |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{124^{\circ}C/W}$ | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{124^{\circ}C/W}$ |

| $P_{D} = 1.01 W$                                                                                              | $P_D = 726 \text{ mW}$                                                                                        |

As can be seen from the calculations above, the compact 6-pin SC-70 copper leadframe LITTLE FOOT power MOSFET can handle up to 1 W under the stated conditions.

### Testing

To further aid comparison of copper and Alloy 42 leadframes, Figure 5 illustrates single-channel 6-pin SC-70 thermal performance on two different board sizes and two different pad patterns. The measured steady-state values of  $R\theta_{JA}$  for the two leadframes are as follows:

# LITTLE FOOT 6-PIN SC-70 Alloy 42 Copper 1) Minimum recommended pad pattern on the EVB board V (see Figure 3. 329.7°C/W 208.5°C/W 2) Industry standard 1-inch<sup>2</sup> PCB with maximum copper both sides. 211.8°C/W 103.5°C/W

The results indicate that designers can reduce thermal resistance (R $\theta_{JA}$ ) by 36% simply by using the copper leadframe device rather than the Alloy 42 version. In this example, a 121°C/W reduction was achieved without an increase in board area. If increasing in board size is feasible, a further 105°C/W reduction could be obtained by utilizing a 1-inch<sup>2</sup> square PCB area.

The copper leadframe versions have the following suffix:

| Single:        | Si14xxEDH |

|----------------|-----------|

| Dual:          | Si19xxEDH |

| Complementary: | Si15xxEDH |

FIGURE 4. Leadframe Comparison on EVB

## Dual-Channel LITTLE FOOT® 6-Pin SC-70 MOSFET Copper Leadframe Version Recommended Pad Pattern and Thermal Performance

### INTRODUCTION

The new dual 6-pin SC-70 package with a copper leadframe enables improved on-resistance values and enhanced thermal performance as compared to the existing 3-pin and 6-pin packages with Alloy 42 leadframes. These devices are intended for small to medium load applications where a miniaturized package is required. Devices in this package come in a range of on-resistance values, in n-channel and p-channel versions. This technical note discusses pin-outs, package outlines, pad patterns, evaluation board layout, and thermal performance for the dual-channel version.

### **PIN-OUT**

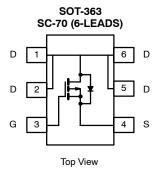

Figure 1 shows the pin-out description and Pin 1 identification for the dual-channel SC-70 device in the 6-pin configuration. Both n-and p-channel devices are available in this package – the drawing example below illustrates the p-channel device.

For package dimensions see outline drawing SC-70 (6-Leads) (http://www.vishay.com/doc?71154)

### **BASIC PAD PATTERNS**

See Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*, (http://www.vishay.com/doc?72286) for the SC-70 6-pin basic pad layout and dimensions. This pad pattern is sufficient for the low-power applications for which this package is intended. Increasing the drain pad pattern (Figure 2) yields a reduction in thermal resistance and is a preferred footprint.

FIGURE 2. SC-70 (6 leads) Dual

### EVALUATION BOARD FOR THE DUAL-CHANNEL SC70-6

The 6-pin SC-70 evaluation board (EVB) shown in Figure 3 measures 0.6 in. by 0.5 in. The copper pad traces are the same as described in the previous section, *Basic Pad Patterns*. The board allows for examination from the outer pins to the 6-pin DIP connections, permitting test sockets to be used in evaluation testing.

The thermal performance of the dual 6-pin SC-70 has been measured on the EVB, comparing both the copper and Alloy 42 leadframes. This test was then repeated using the 1-inch<sup>2</sup> PCB with dual-side copper coating.

A helpful way of displaying the thermal performance of the 6-pin SC-70 dual copper leadframe is to compare it to the traditional Alloy 42 version.

## AN816 Vishay Siliconix

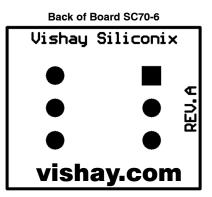

Back of Board SC70-6

### THERMAL PERFORMANCE

Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the dual SC-70 6-pin package is measured as junction-to-foot thermal resistance, in which the "foot" is the drain lead of the device as it connects with the body. The junction-to-foot thermal resistance for this device is typically  $80^{\circ}$ C/W, with a maximum thermal resistance of approximately  $100^{\circ}$ C/W. This data compares favorably with another compact, dual-channel package – the dual TSOP-6 – which features a typical thermal resistance of  $75^{\circ}$ C/W and a maximum of  $90^{\circ}$ C/W.

### **Power Dissipation**

The typical R $\theta_{JA}$  for the dual-channel 6-pin SC-70 with a copper leadframe is 224°C/W steady-state, compared to 413°C/W for the Alloy 42 version. All figures are based on the 1-inch<sup>2</sup> FR4 test board. The following example shows how the thermal resistance impacts power dissipation for the dual 6-pin SC-70 package at varying ambient temperatures.

Alloy 42 Leadframe

| ALLOY 42 LEADFRAME                                          |                                                             |

|-------------------------------------------------------------|-------------------------------------------------------------|

| Room Ambient 25 $^\circ$ C                                  | Elevated Ambient 60 °C                                      |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           |

| $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{413^{\circ}C/W}$ | $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{413^{\circ}C/W}$ |

| $P_D = 303 \text{ mW}$                                      | $P_D = 218 \text{ mW}$                                      |

| COOPER LEADFRAME                                                                        |                                                             |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Room Ambient 25 °C                                                                      | Elevated Ambient 60 °C                                      |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$                                       | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           |

| $P_{\rm D} = \frac{150^{\circ}{\rm C} - 25^{\circ}{\rm C}}{224^{\circ}{\rm C}/{\rm W}}$ | $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{224^{\circ}C/W}$ |

| $P_D = 558 \text{ mW}$                                                                  | $P_D = 402 \text{ mW}$                                      |

Although they are intended for low-power applications, devices in the 6-pin SC-70 dual-channel configuration will handle power dissipation in excess of 0.5 W.

### TESTING

To further aid the comparison of copper and Alloy 42 leadframes, Figures 4 and 5 illustrate the dual-channel 6-pin SC-70 thermal performance on two different board sizes and pad patterns. The measured steady-state values of  $R\theta_{JA}$  for the dual 6-pin SC-70 with varying leadframes are as follows:

| LITTLE | FOOT | 6-PIN | SC-70 | ) |

|--------|------|-------|-------|---|

|        |      |       |       |   |

|                                                                                                  | Alloy 42 | Copper  |

|--------------------------------------------------------------------------------------------------|----------|---------|

| 1) Minimum recommended pad pattern on the EVB board (see Figure 3).                              | 518°C/W  | 344°C/W |

| <ol> <li>Industry standard 1-inch<sup>2</sup> PCB with<br/>maximum copper both sides.</li> </ol> | 413°C/W  | 224°C/W |

The results indicate that designers can reduce thermal resistance ( $\theta$ JA) by 34% simply by using the copper leadframe device as opposed to the Alloy 42 version. In this example, a 174°C/W reduction was achieved without an increase in board area. If an increase in board size is feasible, a further 120°C/W reduction can be obtained by utilizing a 1-inch<sup>2</sup>. PCB area.

The Dual copper leadframe versions have the following suffix:

| Dual:   | Si19xxEDH |

|---------|-----------|

| Compl.: | Si15xxEDH |

FIGURE 4. Dual SC70-6 Thermal Performance on EVB

FIGURE 5. Dual SC70-6 Comparison on 1-inch<sup>2</sup> PCB

VISHAY SILICONIX

www.vishay.com

### **Power MOSFETs**

Application Note AN821

# **PowerPAK® SO-8 Mounting and Thermal Considerations**

#### by Wharton McDaniel

MOSFETs for switching applications are now available with die on resistances around 1 m $\Omega$  and with the capability to handle 85 A. While these die capabilities represent a major advance over what was available just a few years ago, it is important for power MOSFET packaging technology to keep pace. It should be obvious that degradation of a high performance die by the package is undesirable. PowerPAK is a new package technology that addresses these issues. In this application note, PowerPAK's construction is described. Following this mounting information is presented including land patterns and soldering profiles for maximum reliability. Finally, thermal and electrical performance is discussed.

### THE PowerPAK PACKAGE

The PowerPAK package was developed around the SO-8 package (figure 1). The PowerPAK SO-8 utilizes the same footprint and the same pin-outs as the standard SO-8. This allows PowerPAK to be substituted directly for a standard SO-8 package. Being a leadless package, PowerPAK SO-8 utilizes the entire SO-8 footprint, freeing space normally occupied by the leads, and thus allowing it to hold a larger die than a standard SO-8. In fact, this larger die is slightly larger than a full sized DPAK die. The bottom of the die attach pad is exposed for the purpose of providing a direct, low resistance thermal path to the substrate the device is mounted on. Finally, the package height is lower than the standard SO-8, making it an excellent choice for applications with space constraints.

Fia. 1 PowerPAK 1212 Devices

### PowerPAK SO-8 SINGLE MOUNTING

The PowerPAK single is simple to use. The pin arrangement (drain, source, gate pins) and the pin dimensions are the same as standard SO-8 devices (see figure 2). Therefore, the PowerPAK connection pads match directly to those of the SO-8. The only difference is the extended drain connection area. To take immediate advantage of the PowerPAK SO-8 single devices, they can be mounted to existing SO-8 land patterns.

Fig. 2

The minimum land pattern recommended to take full advantage of the PowerPAK thermal performance see Application Note 826, Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs. Click on the PowerPAK SO-8 single in the index of this document.

In this figure, the drain land pattern is given to make full contact to the drain pad on the PowerPAK package.

This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the thermal resistance from the foot of the PowerPAK to the PC board and  $^{

m >}$ therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight and layer stack, experiments have found that >> more than about 0.25 in<sup>2</sup> to 0.5 in<sup>2</sup> of additional copper -(in addition to the drain land) will yield little improvement in thermal performance.

Revision: 16-Mai-13

1

Document Number: 7162

For technical guestions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

### PowerPAK<sup>®</sup> SO-8 Mounting and Thermal Considerations

### **PowerPAK SO-8 DUAL**

The pin arrangement (drain, source, gate pins) and the pin dimensions of the PowerPAK SO-8 dual are the same as standard SO-8 dual devices. Therefore, the PowerPAK device connection pads match directly to those of the SO-8. As in the single-channel package, the only exception is the extended drain connection area. Manufacturers can likewise take immediate advantage of the PowerPAK SO-8 dual devices by mounting them to existing SO-8 dual land patterns.

To take the advantage of the dual PowerPAK SO-8's thermal performance, the minimum recommended land pattern can be found in Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*. Click on the PowerPAK 1212-8 dual in the index of this document.

The gap between the two drain pads is 24 mils. This matches the spacing of the two drain pads on the PowerPAK SO-8 dual package.

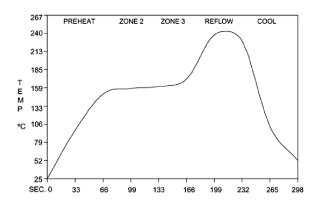

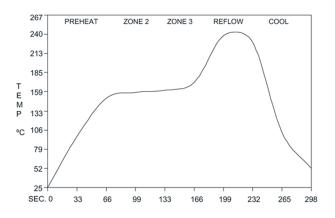

#### **REFLOW SOLDERING**

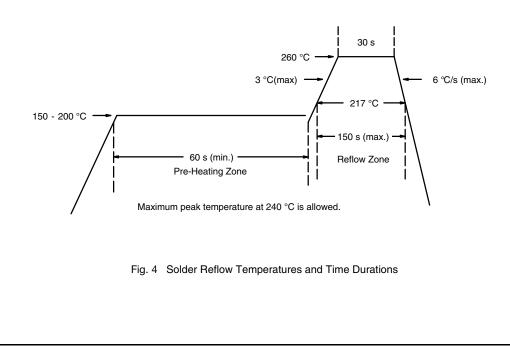

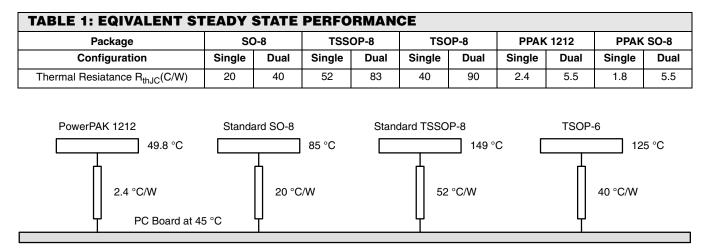

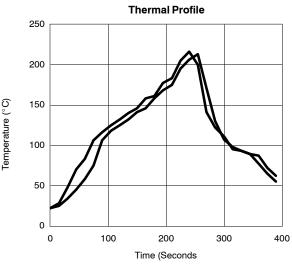

Vishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a test preconditioning and are then reliability-tested using temperature cycle, bias humidity, HAST, or pressure pot. The solder reflow temperature profile used, and the temperatures and time duration, are shown in figures 3 and 4. For the lead (Pb)-free solder profile, see <u>www.vishay.com/doc?73257</u>.

Fig. 3 Solder Reflow Temperature Profile

| Ramp-Up Rate                   | + 3 °C /s max. |  |

|--------------------------------|----------------|--|

| Temperature at 150 - 200 °C    | 120 s max.     |  |

| Temperature Above 217 °C       | 60 - 150 s     |  |

| Maximum Temperature            | 255 + 5/- 0 °C |  |

| Time at Maximum<br>Temperature | 30 s           |  |

| Ramp-Down Rate                 | + 6 °C/s max.  |  |

ш

F O Z

PLICATION

Δ

4

Document Number: 71622

## PowerPAK<sup>®</sup> SO-8 Mounting and Thermal Considerations

### THERMAL PERFORMANCE

#### Introduction

A basic measure of a device's thermal performance is the junction-to-case thermal resistance, R<sub>thJC</sub>, or the junction-to-foot thermal resistance, RthJF This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows a comparison of the DPAK, PowerPAK SO-8, and standard SO-8. The PowerPAK has thermal performance equivalent to the DPAK, while having an order of magnitude better thermal performance over the SO-8.

| TABLE 1 - DPAK AND POWERPAK SO-8EQUIVALENT STEADY STATEPERFORMANCE |          |                  |                  |  |

|--------------------------------------------------------------------|----------|------------------|------------------|--|

|                                                                    | DPAK     | PowerPAK<br>SO-8 | Standard<br>SO-8 |  |

| Thermal<br>Resistance Rthuc                                        | 1.2 °C/W | 1 °C/W           | 16 °C/W          |  |

#### Thermal Performance on Standard SO-8 Pad Pattern

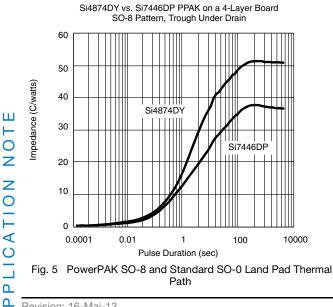

Because of the common footprint, a PowerPAK SO-8 can be mounted on an existing standard SO-8 pad pattern. The question then arises as to the thermal performance of the PowerPAK device under these conditions. A characterization was made comparing a standard SO-8 and a PowerPAK device on a board with a trough cut out underneath the PowerPAK drain pad. This configuration restricted the heat flow to the SO-8 land pads. The results are shown in figure 5.

Because of the presence of the trough, this result suggests a minimum performance improvement of 10 °C/W by using a PowerPAK SO-8 in a standard SO-8 PC board mount.

The only concern when mounting a PowerPAK on a standard SO-8 pad pattern is that there should be no traces running between the body of the MOSFET. Where the standard SO-8 body is spaced away from the pc board, allowing traces to run underneath, the PowerPAK sits directly on the pc board.

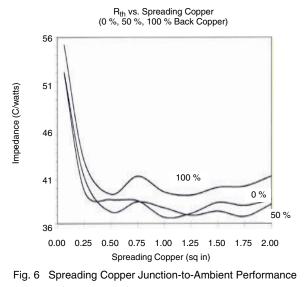

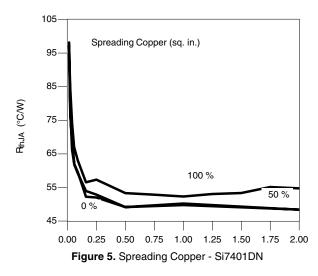

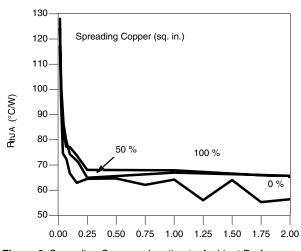

#### **Thermal Performance - Spreading Copper**

Designers may add additional copper, spreading copper, to the drain pad to aid in conducting heat from a device. It is helpful to have some information about the thermal performance for a given area of spreading copper.

Figure 6 shows the thermal resistance of a PowerPAK SO-8 device mounted on a 2-in. 2-in., four-layer FR-4 PC board. The two internal layers and the backside layer are solid copper. The internal layers were chosen as solid copper to model the large power and ground planes common in many applications. The top layer was cut back to a smaller area and at each step junction-to-ambient thermal resistance measurements were taken. The results indicate that an area above 0.3 to 0.4 square inches of spreading copper gives no additional thermal performance improvement. Α subsequent experiment was run where the copper on the back-side was reduced, first to 50 % in stripes to mimic circuit traces, and then totally removed. No significant effect was observed.

4

3

Document Number: 71622

PowerPAK<sup>®</sup> SO-8 Mounting and Thermal Considerations

# SYSTEM AND ELECTRICAL IMPACT OF PowerPAK SO-8

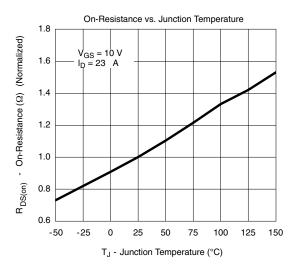

In any design, one must take into account the change in MOSFET  $R_{\text{DS}(\text{on})}$  with temperature (figure 7).

#### Fig. 7 MOSFET RDS(on) vs. Temperature

A MOSFET generates internal heat due to the current passing through the channel. This self-heating raises the junction temperature of the device above that of the PC board to which it is mounted, causing increased power dissipation in the device. A major source of this problem lies in the large values of the junction-to-foot thermal resistance of the SO-8 package.

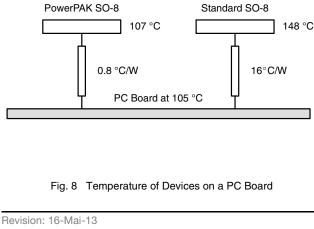

PowerPAK SO-8 minimizes the junction-to-board thermal resistance to where the MOSFET die temperature is very close to the temperature of the PC board. Consider two devices mounted on a PC board heated to 105 °C by other components on the board (figure 8).

Suppose each device is dissipating 2.7 W. Using the junction-to-foot thermal resistance characteristics of the PowerPAK SO-8 and the standard SO-8, the die temperature is determined to be 107 °C for the PowerPAK (and for DPAK) and 148 °C for the standard SO-8. This is a 2 °C rise above the board temperature for the PowerPAK and a 43 °C rise for the standard SO-8. Referring to figure 7, a 2 °C difference has minimal effect on  $R_{DS(on)}$  whereas a 43 °C difference has a significant effect on  $R_{DS(on)}$ .

Minimizing the thermal rise above the board temperature by using PowerPAK has not only eased the thermal design but it has allowed the device to run cooler, keep  $r_{DS(on)}$  low, and permits the device to handle more current than the same MOSFET die in the standard SO-8 package.

### CONCLUSIONS

PowerPAK SO-8 has been shown to have the same thermal performance as the DPAK package while having the same footprint as the standard SO-8 package. The PowerPAK SO-8 can hold larger die approximately equal in size to the maximum that the DPAK can accommodate implying no sacrifice in performance because of package limitations.

Recommended PowerPAK SO-8 land patterns are provided to aid in PC board layout for designs using this new package.

Thermal considerations have indicated that significant advantages can be gained by using PowerPAK SO-8 devices in designs where the PC board was laid out for the standard SO-8. Applications experimental data gave thermal performance data showing minimum and typical thermal performance in a SO-8 environment, plus information on the optimum thermal performance obtainable including spreading copper. This further emphasized the DPAK equivalency.

PowerPAK SO-8 therefore has the desired small size characteristics of the SO-8 combined with the attractive thermal characteristics of the DPAK package.

4 For technical guestions, contact: powermosfettechsupport@vishay.com Document Number: 71622

## PowerPAK<sup>®</sup> 1212 Mounting and Thermal Considerations

### Johnson Zhao

MOSFETs for switching applications are now available with die on resistances around 1 m $\Omega$  and with the capability to handle 85 A. While these die capabilities represent a major advance over what was available just a few years ago, it is important for power MOSFET packaging technology to keep pace. It should be obvious that degradation of a high performance die by the package is undesirable. PowerPAK is a new package technology that addresses these issues. The PowerPAK 1212-8 provides ultra-low thermal impedance in a small package that is ideal for space-constrained applications. In this application note, the PowerPAK 1212-8's construction is described. Following this, mounting information is presented. Finally, thermal and electrical performance is discussed.

### **THE PowerPAK PACKAGE**

The PowerPAK 1212-8 package (Figure 1) is a derivative of PowerPAK SO-8. It utilizes the same packaging technology, maximizing the die area. The bottom of the die attach pad is exposed to provide a direct, low resistance thermal path to the substrate the device is mounted on. The PowerPAK 1212-8 thus translates the benefits of the PowerPAK SO-8 into a smaller package, with the same level of thermal performance. (Please refer to application note "PowerPAK SO-8 Mounting and Thermal Considerations.")

Figure 1. PowerPAK 1212 Devices

The PowerPAK 1212-8 has a footprint area comparable to TSOP-6. It is over 40 % smaller than standard TSSOP-8. Its die capacity is more than twice the size of the standard TSOP-6's. It has thermal performance an order of magnitude better than the SO-8, and 20 times better than TSSOP-8. Its thermal performance is better than all current SMT packages in the market. It will take the advantage of any PC board heat sink capability. Bringing the junction temperature down also increases the die efficiency by around 20 % compared with TSSOP-8. For applications where bigger packages are typically required solely for thermal consideration, the PowerPAK 1212-8 is a good option.

Both the single and dual PowerPAK 1212-8 utilize the same pin-outs as the single and dual PowerPAK SO-8. The low 1.05 mm PowerPAK height profile makes both versions an excellent choice for applications with space constraints.

### **PowerPAK 1212 SINGLE MOUNTING**

To take the advantage of the single PowerPAK 1212-8's thermal performance see Application Note 826,

<u>Recommended Minimum Pad Patterns With Outline</u> <u>Drawing Access for Vishay Siliconix MOSFETs.</u> Click on the PowerPAK 1212-8 single in the index of this document.

In this figure, the drain land pattern is given to make full contact to the drain pad on the PowerPAK package.

This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the thermal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-toambient thermal resistance. Under specific conditions of board configuration, copper weight, and layer stack, experiments have found that adding copper beyond an area of about 0.3 to 0.5 in<sup>2</sup> of will yield little improvement in thermal performance.

To take the advantage of the dual PowerPAK 1212-8's thermal performance, the minimum recommended land pattern can be found in Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*. Click on the PowerPAK 1212-8 dual in the index of this document.

The gap between the two drain pads is 10 mils. This matches the spacing of the two drain pads on the PowerPAK 1212-8 dual package.

This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the thermal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-toambient thermal resistance. Under specific conditions of board configuration, copper weight, and layer stack, experiments have found that adding copper beyond an area of about 0.3 to 0.5 in<sup>2</sup> of will yield little improvement in thermal performance.

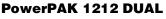

### **REFLOW SOLDERING**

Vishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a preconditioning test and are then reliability-tested using temperature cycle, bias humidity, HAST, or pressure pot. The solder reflow tempera-

ture profile used, and the temperatures and time duration, are shown in Figures 2 and 3. For the lead (Pb)-free solder profile, see http://www.vishay.com/ doc?73257.

| Ramp-Up Rate                | + 6 °C /Second Maximum |  |

|-----------------------------|------------------------|--|

| Temperature at 155 ± 15 °C  | 120 Seconds Maximum    |  |

| Temperature Above 180 °C    | 70 - 180 Seconds       |  |

| Maximum Temperature         | 240 + 5/- 0 °C         |  |

| Time at Maximum Temperature | 20 - 40 Seconds        |  |

| Ramp-Down Rate              | + 6 °C/Second Maximum  |  |

Figure 2. Solder Reflow Temperature Profile

Figure 4. Temperature of Devices on a PC Board

### THERMAL PERFORMANCE

### Introduction

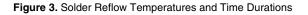

A basic measure of a device's thermal performance is the junction-to-case thermal resistance,  $R\theta jc$ , or the junction to- foot thermal resistance,  $R\theta jf$ . This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows a comparison of the PowerPAK 1212-8, PowerPAK SO-8, standard TSSOP-8 and SO-8 equivalent steady state performance.

By minimizing the junction-to-foot thermal resistance, the MOSFET die temperature is very close to the temperature of the PC board. Consider four devices mounted on a PC board with a board temperature of 45 °C (Figure 4). Suppose each device is dissipating 2 W. Using the junction-to-foot thermal resistance characteristics of the PowerPAK 1212-8 and the other SMT packages, die temperatures are determined to be 49.8 °C for the PowerPAK 1212-8, 85 °C for the standard SO-8, 149 °C for standard TSSOP-8, and 125 °C for TSOP-6. This is a 4.8 °C rise above the board temperature for the PowerPAK 1212-8, and over 40 °C for other SMT packages. A 4.8 °C rise has minimal effect on  $r_{DS(ON)}$  whereas a rise of over 40 °C will cause an increase in  $r_{DS(ON)}$  as high as 20 %.

### **Spreading Copper**

Designers add additional copper, spreading copper, to the drain pad to aid in conducting heat from a device. It is helpful to have some information about the thermal performance for a given area of spreading copper.

Figure 5 and Figure 6 show the thermal resistance of a PowerPAK 1212-8 single and dual devices mounted on a 2-in. x 2-in., four-layer FR-4 PC boards. The two internal layers and the backside layer are solid copper. The internal layers were chosen as solid copper to model the large power and ground planes common in many applications. The top layer was cut back to a smaller area and at each step junction-to-ambient thermal resistance measurements were taken. The results indicate that an area above 0.2 to 0.3 square inches of spreading copper gives no additional thermal performance improvement. A subsequent experiment was run where the copper on the back-side was reduced, first to 50 % in stripes to mimic circuit traces, and then totally removed. No significant effect was observed.

## AN822

### Vishay Siliconix

Figure 6. Spreading Copper - Junction-to-Ambient Performance

### CONCLUSIONS

As a derivative of the PowerPAK SO-8, the PowerPAK 1212-8 uses the same packaging technology and has been shown to have the same level of thermal performance while having a footprint that is more than 40 % smaller than the standard TSSOP-8.

Recommended PowerPAK 1212-8 land patterns are provided to aid in PC board layout for designs using this new package.

The PowerPAK 1212-8 combines small size with attractive thermal characteristics. By minimizing the thermal rise above the board temperature, PowerPAK simplifies thermal design considerations, allows the device to run cooler, keeps  $r_{DS(ON)}$  low, and permits the device to handle more current than a same- or larger-size MOS-FET die in the standard TSSOP-8 or SO-8 packages.

## AN824 Vishay Siliconix

## PCB Design and Assembly Guidelines For MICRO FOOT<sup>®</sup> Products

Johnson Zhao

### INTRODUCTION

Vishay Siliconix's MICRO FOOT product family is based on a wafer-level chip-scale packaging (WL-CSP) technology that implements a solder bump process to eliminate the need for an outer package to encase the silicon die. MICRO FOOT products include power MOSFETs, analog switches, and power ICs.

For battery powered compact devices, this new packaging technology reduces board space requirements, improves thermal performance, and mitigates the parasitic effect typical of leaded packaged products. For example, the 6-bump MICRO FOOT Si8902EDB common drain power MOSFET, which measures just 1.6 mm x 2.4 mm, achieves the same performance as TSSOP-8 devices in a footprint that is 80% smaller and with a 50% lower height profile (Figure 1). A MICRO FOOT analog switch, the 6-bump DG3000DB, offers low charge injection and 1.4 W on-resistance in a footprint measuring just 1.08 mm x 1.58 mm (Figure 2).

Vishay Siliconix MICRO FOOT products can be handled with the same process techniques used for high-volume assembly of packaged surface-mount devices. With proper attention to PCB and stencil design, the device will achieve reliable performance without underfill. The advantage of the device's small footprint and short thermal path make it an ideal option for space-constrained applications in portable devices such as battery packs, PDAs, cellular phones, and notebook computers.

This application note discusses the mechanical design and reliability of MICRO FOOT, and then provides guidelines for board layout, the assembly process, and the PCB rework process.

FIGURE 1. 3D View of MICRO FOOT Products Si8902DB and Si8900EDB

FIGURE 2. Outline of MICRO FOOT CSP & Analog Switch DG3000DB

AN824

| TABLE 1           Main Parameters of Solder Bumps in MICRO FOOT Designs |                               |             |                |              |

|-------------------------------------------------------------------------|-------------------------------|-------------|----------------|--------------|

| MICRO FOOT CSP                                                          | Bump Material                 | Bump Pitch* | Bump Diameter* | Bump Height* |

| MICRO FOOT CSP MOSFET                                                   | <b>5</b>                      | 0.8         | 0.37-0.41      | 0.26-0.29    |

| MICRO FOOT CSP Analog Switch                                            | Eutectic Solder:<br>63Sm/37Pb | 0.5         | 0.18-0.25      | 0.14-0.19    |

| MICRO FOOT UCSP Analog Switch                                           |                               | 0.5         | 0.32-0.34      | 0.21-0.24    |

\* All measurements in millimeters

### **MICRO FOOT'S DESIGN AND RELIABILITY**

As a mechanical, electrical, and thermal connection between the device and PCB, the solder bumps of MICRO FOOT products are mounted on the top active surface of the die. Table 1 shows the main parameters for solder bumps used in MICRO FOOT products. A silicon nitride passivation layer is applied to the active area as the last masking process in fabrication, ensuring that the device passes the pressure pot test. A green laser is used to mark the backside of the die without damaging it. Reliability results for MICRO FOOT products mounted on a FR-4 board without underfill are shown in Table 2.

| TABLE 2           MICRO FOOT Reliability Results |              |  |  |  |

|--------------------------------------------------|--------------|--|--|--|

| Test Condition C: -65° to 150°C                  | >500 Cycles  |  |  |  |

| Test condition B: -40° to 125°C                  | >1000 Cycles |  |  |  |

| 121°C @ 15PSI 100% Humidity Test                 | 96 Hours     |  |  |  |

The main failure mechanism associated with wafer-level chip-scale packaging is fatigue of the solder joint. The results shown in Table 2 demonstrate that a high level of reliability can be achieved with proper board design and assembly techniques.

### **BOARD LAYOUT GUIDELINES**

**Board materials**. Vishay Siliconix MICRO FOOT products are designed to be reliable on most board types, including organic boards such as FR-4 or polyamide boards. The package qualification information is based on the test on 0.5-oz. FR-4 and polyamide boards with NSMD pad design.

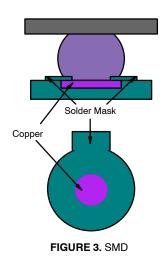

*Land patterns.* Two types of land patterns are used for surface-mount packages. Solder mask defined (SMD) pads have a solder mask opening smaller than the metal pad (Figure 3), whereas on-solder mask defined (NSMD) pads have a metal pad smaller than the solder-mask opening (Figure 4).

NSMD is recommended for copper etch processes, since it provides a higher level of control compared to SMD etch processes. A small-size NSMD pad definition provides more area (both lateral and vertical) for soldering and more room for escape routing on the PCB. By contrast, SMD pad definition introduces a stress -concentration point near the solder mask on the PCB side that may result in solder joint cracking under extreme fatigue conditions.

Copper pads should be finished with an organic solderability preservative (OSP) coating. For electroplated nickel-immersion gold finish pads, the gold thickness must be less than 0.5  $\mu$ m to avoid solder joint embrittlement.

Solder Mask Copper

**Board pad design.** The landing-pad size for MICRO FOOT products is determined by the bump pitch as shown in Table 3. The pad pattern is circular to ensure a symmetric, barrel-shaped solder bump.

| TABLE 3           Dimensions of Copper Pad and Solder Mask           Opening in PCB and Stencil Aperture |                    |                        |                                                                                       |  |

|----------------------------------------------------------------------------------------------------------|--------------------|------------------------|---------------------------------------------------------------------------------------|--|

| Pitch                                                                                                    | Copper Pad         | Solder Mask<br>Opening | Stencil<br>Aperture                                                                   |  |

| 0.80 mm                                                                                                  | 0.30 $\pm$ 0.01 mm | 0.41 $\pm$ 0.01 mm     | $0.33 \pm 0.01 \text{ mm}$ in ciircle aperture                                        |  |

| 0.50 mm                                                                                                  | 0.17 $\pm$ 0.01 mm | 0.27 $\pm$ 0.01 mm     | $\begin{array}{c} 0.30\ \pm\ 0.01\ \text{mm}\\ \text{in square aperture} \end{array}$ |  |

### ASSEMBLY PROCESS

MICRO FOOT products' surface-mount-assembly operations include solder paste printing, component placement, and solder reflow as shown in the process flow chart (Figure 5).

FIGURE 5. SMT Assembly Process Flow

**Stencil design**. Stencil design is the key to ensuring maximum solder paste deposition without compromising the assembly yield from solder joint defects (such as bridging and extraneous solder spheres). The stencil aperture is dependent on the copper pad size, the solder mask opening, and the quantity of solder paste.

In MICRO FOOT products, the stencil is 0.125-mm (5-mils) thick. The recommended apertures are shown in Table 3 and are fabricated by laser cut.

**Solder-paste printing.** The solder-paste printing process involves transferring solder paste through pre-defined apertures via application of pressure.

In MICRO FOOT products, the solder paste used is UP78 No-clean eutectic 63 Sn/37Pb type3 or finer solder paste.

*Chip pick-and-placement.* MICRO FOOT products can be picked and placed with standard pick-and-place equipment. The recommended pick-and-place force is 150 g. Though the part will self-center during solder reflow, the maximum placement offset is 0.02 mm.

**Reflow Process.** MICRO FOOT products can be assembled using standard SMT reflow processes. Similar to any other package, the thermal profile at specific board locations must be determined. Nitrogen purge is recommended during reflow operation. Figure 6 shows a typical reflow profile.

FIGURE 6. Reflow Profile

### **PCB REWORK**

To replace MICRO FOOT products on PCB, the rework procedure is much like the rework process for a standard BGA or CSP, as long as the rework process duplicates the original reflow profile. The key steps are as follows:

- 1. Remove the MICRO FOOT device using a convection nozzle to create localized heating similar to the original reflow profile. Preheat from the bottom.

- 2. Once the nozzle temperature is +190°C, use tweezers to remove the part to be replaced.

- 3. Resurface the pads using a temperature-controlled soldering iron.

- 4. Apply gel flux to the pad.

- 5. Use a vacuum needle pick-up tip to pick up the replacement part, and use a placement jig to placed it accurately.

- 6. Reflow the part using the same convection nozzle, and preheat from the bottom, matching the original reflow profile.

Vishay

## Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.