# Single-Channel LITTLE FOOT® SC-70 6-Pin MOSFET Copper Leadframe Version Recommended Pad Pattern and Thermal Performance

## INTRODUCTION

The new single 6-pin SC-70 package with a copper leadframe enables improved on-resistance values and enhanced thermal performance as compared to the existing 3-pin and 6-pin packages with Alloy 42 leadframes. These devices are intended for small to medium load applications where a miniaturized package is required. Devices in this package come in a range of on-resistance values, in n-channel and p-channel versions. This technical note discusses pin-outs, package outlines, pad patterns, evaluation board layout, and thermal performance for the single-channel version.

## **BASIC PAD PATTERNS**

See Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*, (http://www.vishay.com/doc?72286) for the basic pad layout and dimensions. These pad patterns are sufficient for the low to medium power applications for which this package is intended. Increasing the drain pad pattern yields a reduction in thermal resistance and is a preferred footprint. The availability of four drain leads rather than the traditional single drain lead allows a better thermal path from the package to the PCB and external environment.

## **PIN-OUT**

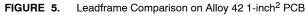

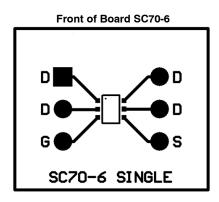

Figure 1 shows the pin-out description and Pin 1 identification. The pin-out of this device allows the use of four pins as drain leads, which helps to reduce on-resistance and junction-to-ambient thermal resistance.

FIGURE 1.

For package dimensions see outline drawing SC-70 (6-Leads) (http://www.vishay.com/doc?71154)

# **EVALUATION BOARDS — SINGLE SC70-6**

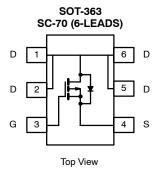

The evaluation board (EVB) measures 0.6 inches by 0.5 inches. The copper pad traces are the same as in Figure 2. The board allows examination from the outer pins to 6-pin DIP connections, permitting test sockets to be used in evaluation testing. See Figure 3.

FIGURE 2. SC-70 (6 leads) Single

The thermal performance of the single 6-pin SC-70 has been measured on the EVB, comparing both the copper and Alloy 42 leadframes. This test was first conducted on the traditional Alloy 42 leadframe and was then repeated using the 1-inch<sup>2</sup> PCB with dual-side copper coating.

# AN815 Vishay Siliconix

FIGURE 3.

## THERMAL PERFORMANCE

# Junction-to-Foot Thermal Resistance (Package Performance)

The junction to foot thermal resistance is a useful method of comparing different packages thermal performance.

A helpful way of presenting the thermal performance of the 6-Pin SC-70 copper leadframe device is to compare it to the traditional Alloy 42 version.

Thermal performance for the 6-pin SC-70 measured as junction-to-foot thermal resistance, where the "foot" is the drain lead of the device at the bottom where it meets the PCB. The junction-to-foot thermal resistance is typically 40°C/W in the copper leadframe and 163°C/W in the Alloy 42 leadframe — a four-fold improvement. This improved performance is obtained by the enhanced thermal conductivity of copper over Alloy 42.

## **Power Dissipation**

The typical R $\theta_{JA}$  for the single 6-pin SC-70 with copper leadframe is 103°C/W steady-state, compared with 212°C/W for the Alloy 42 version. The figures are based on the 1-inch<sup>2</sup> FR4 test board. The following example shows how the thermal resistance impacts power dissipation for the two different leadframes at varying ambient temperatures.

| ALLOY 42 LEADFRAME                                          |                                                             |  |

|-------------------------------------------------------------|-------------------------------------------------------------|--|

| Room Ambient 25 °C                                          | Elevated Ambient 60 °C                                      |  |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           |  |

| $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{212^{\circ}C/W}$ | $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{212^{\circ}C/W}$ |  |

| $P_D = 590 \text{ mW}$                                      | $P_{D} = 425 \text{ mW}$                                    |  |

| COOPER LEADFRAME                                                                                              |                                                                                                               |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| Room Ambient 25 $^{\circ}$ C                                                                                  | Elevated Ambient 60 °C                                                                                        |  |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{124^{\circ}C/W}$ | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{124^{\circ}C/W}$ |  |

| $P_{D} = 1.01 W$                                                                                              | $P_D = 726 \text{ mW}$                                                                                        |  |

As can be seen from the calculations above, the compact 6-pin SC-70 copper leadframe LITTLE FOOT power MOSFET can handle up to 1 W under the stated conditions.

## Testing

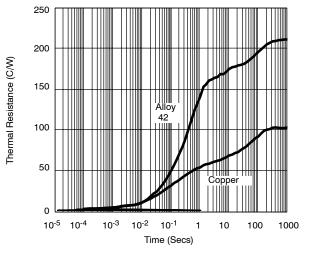

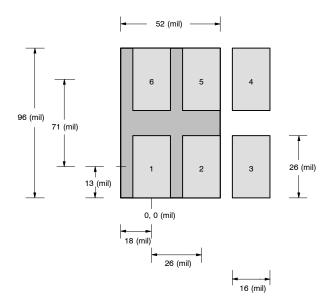

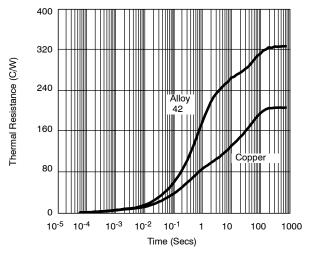

To further aid comparison of copper and Alloy 42 leadframes, Figure 5 illustrates single-channel 6-pin SC-70 thermal performance on two different board sizes and two different pad patterns. The measured steady-state values of  $R\theta_{JA}$  for the two leadframes are as follows:

# LITTLE FOOT 6-PIN SC-70 Alloy 42 Copper 1) Minimum recommended pad pattern on the EVB board V (see Figure 3. 329.7°C/W 208.5°C/W 2) Industry standard 1-inch<sup>2</sup> PCB with maximum copper both sides. 211.8°C/W 103.5°C/W

The results indicate that designers can reduce thermal resistance (R $\theta_{JA}$ ) by 36% simply by using the copper leadframe device rather than the Alloy 42 version. In this example, a 121°C/W reduction was achieved without an increase in board area. If increasing in board size is feasible, a further 105°C/W reduction could be obtained by utilizing a 1-inch<sup>2</sup> square PCB area.

The copper leadframe versions have the following suffix:

| Single:        | Si14xxEDH |

|----------------|-----------|

| Dual:          | Si19xxEDH |

| Complementary: | Si15xxEDH |

FIGURE 4. Leadframe Comparison on EVB