### VISHAY SEMICONDUCTORS

www.vishay.com

### **Optocouplers**

**Application Note 60**

# SSR Design Using VO1263

### INTRODUCTION

A solid state relay (SSR) is a semiconductor device that can be used in place of a mechanical relay in many applications to switch electricity to a load. SSRs are purely electronic and normally composed of a low-current control side (equivalent to the coil on an mechanical relay) and a high-current load side (equivalent to the contact on a conventional mechanical relay). SSRs typically feature electrical isolation to several thousands volts between the control and load sides. Because of this isolation, the load side of the relay is actually powered by the switched line; both line voltage and a load (not to mention a control signal) must be present for the relay to operate.

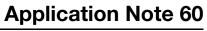

An SSR contains one or more LEDs in the input (drive) section and provides optical coupling to a phototransistor or photodiode array, which in turn connects to driver circuitry that provides an interface to the switching device or devices at the output. The switching device is typically a MOSFET or TRIAC.

The advantages of solid-state relays vs. their mechanical counterparts are numerous:

- 1. Higher reliability

- 2. Smaller size

- 3. Faster switching times

- 4. Elimination of switch bounce

- 5. Elimination of HV arcing

- 6. Lower triggering currents

- 7. Robust packaging

The list of benefits could go on and is limited only by the designer's imagination.

Several issues held back the adoption of solid-state relays as a replacement for their mechanical counterparts:

- 1. High relative on-resistances

- 2. Low load current capacity

- 3. Price

- 4. Ease of design

Of these features the first three have been almost eliminated by the quantum advances in power MOSFET technology. MOSFETs now come in packages that offer ever-increasing load currents, with lower on-resistances, and at lower prices. If "a picture can replace a thousand words," then the illustration in figure 1 should speak for itself. One can see a mechanical relay with a current handling capacity of 25 A and a power MOSFET with a current handling capacity of 30 A side by side.

The last issue, ease of design, is one that will be addressed in this document.

In order to utilize the benefits and flexibility of power MOSFET technology, it is often required that sophisticated driver circuitry be designed to drive these devices. When added to the fact that one often requires the input and output sides of switch to be galvanically isolated, this frequently discourages designers from seeking solid state solutions for switching problems.

The term SSR is often used interchangeably with optically isolated power TRIAC devices. This is especially true in the industrial control field, but this is not the type of solid-state switch that this document is concerned with. However, it is important to note that Vishay also offers an extensive assortment of phototriac devices (please refer to appropiate Vishay applications notes on phototriac devices). MOSFET - based SSRs are far more versatile than their TRIAC based counterparts. In the case of TRIAC-based devices, they are limited to AC load applications, while MOSFET based devices can handle AC and DC loads with equal ease.

Moreover, with the rapid development of low cost, and high current power MOSFETs, the price for 'true' (non-thyristor based devices) bi-directional SSRs is rapidly falling. If one is not readily available off-the-shelf, it is a simple design exercise to design one using readily available photovoltaic diode arrays (PDAs) such as Vishay's VO1263.

Document Number: 81225

For technical questions, contact: optocoupleranswers@vishay.com

### SSR Design Using VO1263

### VO1263 BASICS

A photovoltaic MOSFET driver such as Vishay's VO1263 offers what is most probably the simplest solution to driving power MOSFETs with the fewest possible number of parts. It also inherently provides the designer with the important advantage of galvanic isolation of input to output. The VO1263 consists of an LED similar to any other optocoupler device. However, instead of the LED driving a phototransistor or other such low power detector element, it drives a photovoltaic stack. Thus it is able to generate a sufficient voltage and current to drive MOSFETs. The detector or output side of the VO1263 can be thought of schematically as a matrix of series photodiodes similar to what is illustrated in figure 1.

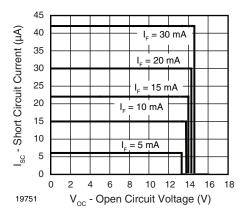

This type of arrangement generates a current versus voltage (IV) characteristic very similar to what would be expected from a solar cell. This IV curve is illustrated in figure 6, and demonstrates a curve typical of what would be found in a battery or solar cell, mainly that at low output currents the device exhibits a maximum output voltage, more commonly referred to as the "open-circuit voltage". As the current increases the voltage drops until it reaches a minimum. At the point where the voltage drops to zero, the current reaches its maximum, known commonly as the "short circuit current".

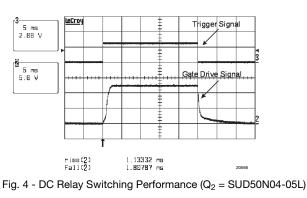

The drive current available from the device is sufficient to actively drive push-pull MOSFET drivers with comparable MOSFET switching times. Typical switching times are in millisecond range which is more than acceptable in terms of delay when compared to electromechanical relays.

### **OPTO-MOSFET**

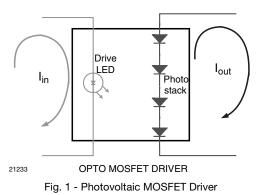

Figure 2 illustrates a design/model for what is probably the simplest possible MOSFET switch.

Fig. 2 - Simplest MOSFET Switch Model

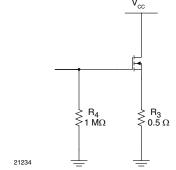

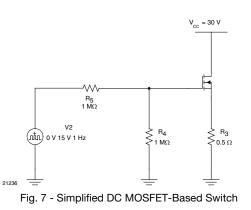

A DC MOSFET based relay can be designed/modeled with VO1263 driver and a MOSFET as illustrated in figure 3. As a matter of fact, the whole design only consists of four parts. This is an excellent starting point to develop a working understanding of the possibilities of photovoltaic MOSFET drivers, in the creation of custom SSRs.

Document Number: 81225

For technical questions, contact: <u>optocoupleranswers@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

Ш

### SSR Design Using VO1263

#### **TURN-ON TIME**

Optimizing the MOSFET drive circuit is most important to a successful design, whether one is considering the design of a simple one MOSFET DC switch or the more complex applications to be discussed later on in this document.

In many cases the process of optimization of MOSFET drive circuit does not require a tremendous amount of mathematics to accomplish. All that is required is a couple of simple arithmetic relations. The first and most useful relation is:

Equation 1:

$$t_{on} = \frac{Q_g}{I_{SC}}$$

Where:

$Q_g$  = Amount of charge required to fully turn-on a MOSFET I<sub>SC</sub> = Amount of current available from the PDA of the VO1263 driver

This relationship flows from the basic definition of electrical current, which is charge over time. In most cases, the datasheet for a power MOSFETs provide the total charge required to turn the device on. However, in some cases, instead of certain gate charge, a capacitance value at a certain gate voltage may be provided. The relationship between gate capacitance, gate charge and gate voltage is as follows:

Equation 2:

$$C_g = \frac{Q_g}{V_{GS}}$$

This relationship can now be used to convert from a capacitive-based parameter to a charge-based parameter that can be used in equation 1.

In terms of turn-on performance several measures can also be taken to speed up this process. However, in essence all these measurements involve the same idea, mainly increasing the amount of drive of the PDA. This goal can be accomplished by either driving the LEDs more vigorously, or placing to PDAs in parallel to double the current driving capability of the MOSFET driver.

### ○ TURN-OFF TIME

Turn-off time is equally simple to calculate in the case of a simple passive resistive turn-off. In such a case the turn-off of the MOSFET is simply the gate capacitance discharged across the gate discharge resistor (R4). The relationship is given by the one time constant relationship illustrated in equation 3:

Equation 3:

$$f_{\text{max.}} = \frac{I_{\text{SC (min.)}}}{Q_{\text{g}}}$$

In the case of figure 7 and where SUD50N04 is used:  $R_g$  = 1  $M\Omega$  and  $C_g$  = 5600 pF, turn-off time is calculated to be:

$t_{off} = 5 \text{ ms}$

A quick calculation of the maximum allowable switching frequency can be made using equation 4 when using the minimum  $I_{SC}$  value (7.5 µA) for  $I_F$  = 10 mA per the data sheet.

Equation 4:

$$f_{\text{max.}} = \frac{I_{\text{SC (min.)}}}{Q_{\text{g}}}$$

Example:

$$f_{\text{max.}} = \frac{7.5 \,\mu\text{A}}{19 \,\text{nC}} = 394.7 \,\text{Hz}$$

In most practical cases turn-off is the main point of performance contention, and various techniques will be discussed further on this document.

### **"SPICE"ING THINGS UP**

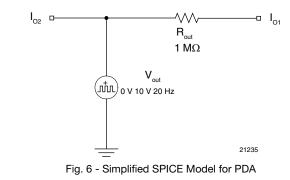

Aside from some simple equations the best way to predict turn-on and turn-off performance would be using SPICE. The model for the VO1263 is very simple and since very detailed models for power MOSFETs are readily available from various manufacturers such as Vishay Siliconix, very reliable predictions can be made with minimal effort.

There are two approaches to modeling a PDA. One is to model the VO1263 as a current source, where the current is specified as some drive current equal to or less. But current sources are problematical because they source current regardless of the impedance they drive and this can lead to unrealistic scenarios. A better approach is to model the PDA of VO1263 as a voltage source driving a high output impedance. The output impedance is approximated by the following equation:

Equation 5:

$$R_{out} = \frac{V_{OC}}{I_{SC}}$$

Document Number: 81225

Where:

V<sub>OC</sub> = Maximum output voltage

$I_{SC}$  = Maximum output current available from the part  $% I_{SC}$

Rev. 1.2, 20-Mar-12

3 For technical guestions, contact: optocoupleranswers@vishay.com

s@vishav.com

APPLICATION NC

н

### SSR Design Using VO1263

For a more precise modeling of the output resistance, it is advised that the voltage and current used in equation 4 be to be taken from the typical PDA IV curve illustrated in figure 5. This should be done by selecting the closest voltage and current on the PDA IV curve to the actual operating point of the circuit in question.

Fig. 5 - VO1263 PDA Short Circuit Current vs. Open Circuit Voltage

The voltage value of the voltage source is either taken as  $V_{\rm OC}$ , or a suitable point along the IV operating curve of the PDA.

Based on the information presented in figure 7, the  $\rm R_{out}$  range is calculated to be as follows.

For

$I_F$  = 5 mA,  $V_{OC}$  = 13.3 V,  $I_{SC}$  = 6  $\mu A,\,R_{out}$  = 2.2  $M\Omega$

and for

$I_F$  = 10 mA,  $V_{OC}$  = 14.6 V,  $I_{SC}$  = 42  $\mu A,\,R_{out}$  = 348 k $\Omega.$

Hence,  $R_{out}$  = 1  $M\Omega$  which is the average of the above calculated values is selected.

Thus one is left with the simple model illustrated in figure 6.

This simple model can now be combined with various readily available models of MOSFETs to come up with various configurations of MOSFET based solid state switches.

Since figure 6 is a highly simplistic approach to the problem, a better, but slightly more complicated approach would be to use a diode array model as the voltage source.

#### **HIGH-CURRENT SSRs**

The addition of a power MOSFET can lead to a complete model of a DC, MOSFET-based switch.

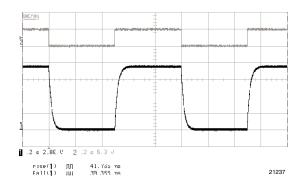

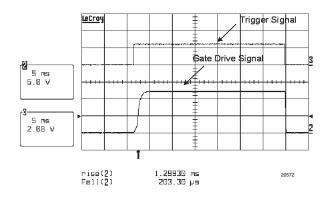

Fig. 8 - Switching Level and Time with only the 1  $M\Omega$  from the Scope Shunted across the Output

It is important to note that when using a probe the equivalent 500 k $\Omega$  discharge resistor usually represents a 1 M $\Omega$  discrete resistor included in figure 7 in parallel with the 1 M $\Omega$  impedance of the oscilloscope probe. Not taking into account the impedance of the oscilloscope probe when dealing with high output impedance devices such as the VO1263 can lead to very confusing results as shown in figures 8 and 9.

ш

⊢

Rev. 1.2, 20-Mar-12

4

www.vishay.com

ISHA

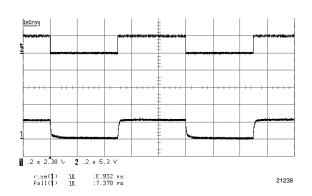

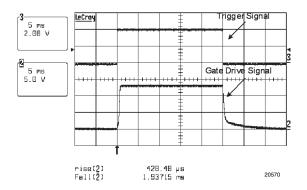

Fig. 9 - Switching Level and Time with having the 1 M $\Omega$  Resistor in and using Standard Passive 1 M $\Omega$  Probe across the Output

If direct gate drive measurements are required, it is important to either use an extremely high impedance active probe or, more economically, simply take into account the probe impedance as stated above.

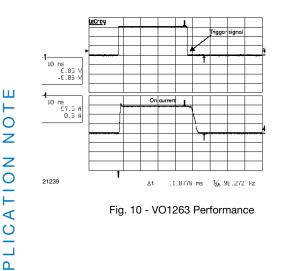

In many applications the simple scenario outlined above is sufficient to meet the requirements of many solid-state relay applications. If on the other hand faster switching is required, this need can be met with a minimal amount of additional complexity. Using the VO1263 a designer can implement galvanic isolation into a MOSFET switch design with a minimum amount of additional parts. Even with large MOSFETs, capable of extremely high current carrying capacity, the VO1263 provides a large enough current drive to make it an effective alternative to larger and less reliable mechanical relays. This current capability is well illustrated in figure 10.

### **AC RELAYS**

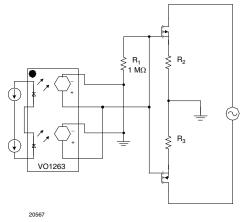

Addition of a second MOSFET can quite easily allow for the simple synthesis of an AC switch per figure 11, as apposed to the simple DC switch illustrated in figure 7.

Fig. 11 - MOSFET AC Relay Schematic

The function of AC switching can be performed using TRIACs or phototriacs. However, the MOSFET AC relay approach has several advantages over the more traditional thyristor switch approach:

- 1. Lower Ron losses

- 2. Higher output dV/dt performance

- 3. Higher operating frequencies

- 4. Lower power consumption

- 5. Faster switching rates

- 6. AC/DC switching capability

These advantages are only getting more accentuated as power MOSFET technology rapidly progresses both in terms of cost and performance.

#### **INCREASING SWITCHING SPEED**

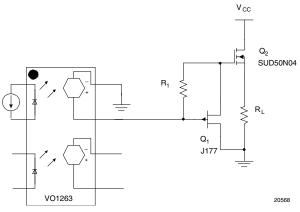

Of the two switching cycles, turn-off and turn-on, that govern the overall switching speed of a PDA based SSR, turn-off is probably by far the most significant as shown in figure 12. Consequently, this document will first focus on ways to decrease the turn-off time of PDA driven MOSFETs.

Rev. 1.2, 20-Mar-12

5

### SSR Design Using VO1263

#### **IMPROVING TURN-OFF TIME**

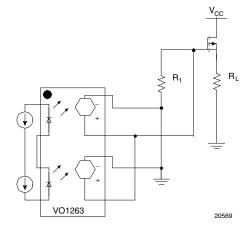

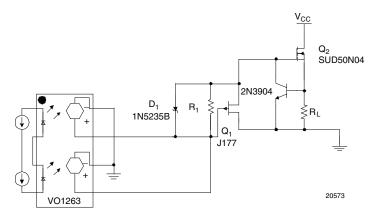

The most popular approach to reduce the turn-off time of an SSR is using a depletion mode device such as a JFET.

The fundamental concept behind this approach is simple. The JFET is in its conduction mode until a certain voltage is developed across the gate of the MOSFET. At this point the JFET is turned off and the gate is allowed to charge. Once the PDA turns off the JFET once again goes into conduction mode and discharges the gate to source capacitance, producing the desired faster turn-off time. This approach also has the added advantage of reducing the amount of current shunted off during the normal turn on cycle, thus reducing the time for turn on, which is the case in the resistor "bleed off" method of gate discharge. Thus for the cost of an inexpensive p-channel JFET and a resistor, an SSR with respectable switching performance can be obtained. This is shown on figure 12. The same could be achieved with a depletion mode MOSFET, but they are significantly harder to find.

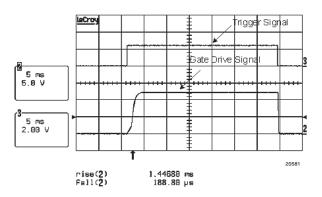

This improved turn-off approach is verified by subsequent lab results illustrated in figure 13. Figure 13 can be compared to the results in figure 10 to dramatically illustrate the improved turn-off results.

Fig. 12 - Improving Turn-off Time by using a JFET

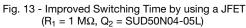

There are some limitations to the preceding fast turn-off circuit. Mainly, that the presence of R<sub>1</sub> of the JFET in conjunction with C<sub>g</sub> of the MOSFET severely limits the turn-on time of the device by adding an unwanted time constant on the gate of the output MOSFET. A simple way to resolve this issue is to remove R<sub>1</sub> until the required threshold voltage of the output MOSFET is reached. This can be accomplished by adding a zener diode in parallel with R<sub>1</sub>. The value of the zener voltage should be V<sub>Z</sub> > V<sub>pinch</sub>. This refinement of the basic JFET SSR turn-off technique is illustrated in figure 14.

Fig. 14 - Improving Turn-on Time by Adding a Zener in Parallel to R1

Document Number: 81225

Rev. 1.2, 20-Mar-12

For technical questions, contact: optocoupleranswers@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <a href="http://www.vishay.com/doc?91000">www.vishay.com/doc?91000</a>

# SSR Design Using VO1263

Fig. 15 - Improved Turn-on Time by adding a Zener in Parallel to  $R_1$   $(R_1$  = 1  $M\Omega, \, Q_2$  = SUD50N04-05L)

### **IMPROVING TURN-ON TIME**

To improve the turn-on time of an SSR design further, it is necessary to either decrease the gate capacitance of the output MOSFET, or increase the drive current available to drive the output MOSFETs. However, there isn't a great deal that can be done in terms of changing the gate characteristics of the output MOSFET. It is taken for granted that a designer will utilize a MOSFET that has the lowest permissible gate capacitance given an applications performance and economic constraints, consequently one is left with improving the drive circuit.

The most obvious solution is to increase the drive output current of the PDA. Fortunately, because Vishay's PDA is available in dual package configurations this can be easily accomplished by simply placing two of the outputs in parallel to drive the same output MOSFET gate. This approach, shown on figure 16, doubles the available drive current, thereby increasing the turn-on time.

Fig. 16 - Improving Turn-on Time by using Two Channels

Fig. 17 - Improved Turn-on Time by using Two Channels (R1 = 1 M\Omega)

ш

Rev. 1.2, 20-Mar-12

7 For technical questions, contact: <u>optocoupleranswers@vishay.com</u> Document Number: 81225

## SSR Design Using VO1263

Table 1 illustrates the differences in MOSFET gate turn-on and turn-off time for different configurations.

| TABLE 1 - TURN-ON AND TURN-OFF TIMES FOR DIFFERENT CONFIGURATIONS ( $V_{DD}$ = 25 V, $R_2$ = 500 $\Omega$ , $Q_2$ = SUD50N04-05L) |                        |                                |         |          |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|---------|----------|

| I <sub>F</sub>                                                                                                                    | R <sub>1</sub><br>(MΩ) | JFET, D <sub>1</sub>           | TURN-ON | TURN-OFF |

|                                                                                                                                   |                        | Single channel                 |         | •        |

| 10 mA                                                                                                                             | 1                      | Not used                       | 1.13 ms | 1.81 ms  |

|                                                                                                                                   | 2                      | Not used                       | 737 µs  | 2.67 ms  |

|                                                                                                                                   | 3                      | Not used                       | 559 µs  | 3.06 ms  |

|                                                                                                                                   |                        | Dual channel                   |         |          |

| 10 mA                                                                                                                             | 1                      | Not used                       | 420 µs  | 1.94 ms  |

|                                                                                                                                   | 2                      | Not used                       | 301 µs  | 2.39 ms  |

|                                                                                                                                   | 3                      | Not used                       | 2.72 ms | 2.744 ms |

|                                                                                                                                   |                        | Single channel and JFET        |         |          |

| 10 mA                                                                                                                             | 0.560                  | J177                           | 946 µs  | 140 µs   |

|                                                                                                                                   | 1                      | J177                           | 1.44 ms | 188 µs   |

|                                                                                                                                   | 2                      | J177                           | 2.66 ms | 295 µs   |

|                                                                                                                                   | Sing                   | gle channel and JFET and 6.9 V | Zener   |          |

| 10 mA                                                                                                                             | 0.560                  | J177, IN5235B                  | 863 µs  | 123 µs   |

|                                                                                                                                   | 1                      | J177, IN5235B                  | 1.29 ms | 203 µs   |

|                                                                                                                                   | 2                      | J177, IN5235B                  | 1.54 ms | 295 µs   |

#### **ADDING CURRENT LIMIT FEATURES**

In many SSR applications, in addition to switching performance requirements, there are also requirements for current limit. This too can be easily included into a simple PDA driven SSR design using a few inexpensive components. The design approach is a very common one,

where a sense resistor is used to "look" at the current across the output of the SSR. In this case RLMT is used to drive an NPN, which shunts away the driving current from the PDA to the gate of the output MOSFET at a predetermined voltage. Such a circuit is illustrated in figure 18.

Fig. 18 - SSR Application with Current Limit and Improved Switching Performance

Document Number: 81225

# SSR Design Using VO1263

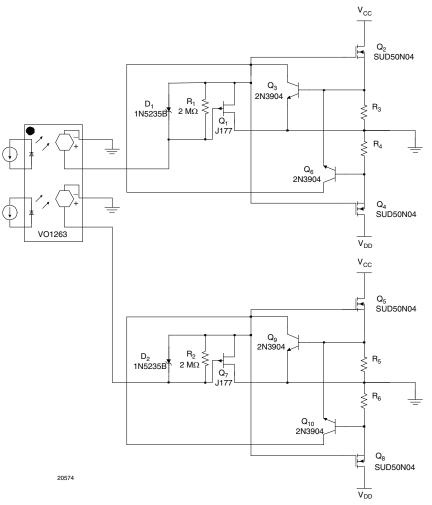

Figure 19 is simply a dual channel bipolar output extension of figure 18.

Fig. 19 - Full Feature Discrete Dual Bidirectional SSR

ш

Rev. 1.2, 20-Mar-12

9 For technical questions, contact: <u>optocoupleranswers@vishay.com</u> Document Number: 81225