VISHAY SEMICONDUCTORS

www.vishay.com

### Diodes

Application Note

# Soldering Recommendations for Chip Level Package (CLP)

#### By Henry Karrer

#### INTRODUCTION

The trend in mobile applications towards reducing the package size and thickness of components is supported by Vishay Semiconductors chip level package (CLP) technology. The following guidelines are intended to help customers avoid trial and error in PCB design and reflow process tuning.

The following parameters are key to success:

- · Using solder mask defined (SMD) solder lands

- · Using the right amount of solder paste

By following these guidelines, the quality of the soldered CLP product will meet key requirements:

- · Self-centering of the CLP product on the PCB

- Optimum stand-off

- · Minimum tilt, and rotation

- No shorts

These parameters have been verified by internal tests at Vishay.

#### PCB SOLDER LAND DESIGN

#### Non-Solder Mask Defined (NSMD) Solder Lands

The size of the solder lands is defined by the copper area (and its tolerances), with the effective solder land being equal to the copper area. The solder mask layer does not touch the solder lands; the typical solder mask layer offset must be at least 75 µm wider than the solder land. This value may vary depending on the class of PCB used. NSMD solder lands are not recommended for CLP products.

#### Solder Mask Defined (SMD) Solder Lands

The solder land size is defined by the solder mask opening. Considering the offset tolerances for the solder masking process, the copper must be larger than the actual solder land by at least 75 µm on each side. This value may vary depending on the class of PCB used.

The advantage of SMD solder lands is that their size is much more accurate compared to NSMD solder lands, independent of any process tolerances in PCB copper etching and solder mask placement.

SMD solder lands are recommended for CLP products.

#### Solder Land Size

For CLP products, the exact size of the solder land is very important. The device foot-pad size must be the same as the solder land size.

| TABLE 1: SOLDER LAND SIZES |                 |                 |

|----------------------------|-----------------|-----------------|

|                            | LAND SIZE 1     | LAND SIZE 2     |

| CLP0603-2L<br>(VBUS, VCUT) | 140 µm x 240 µm | 140 μm x 240 μm |

| CLP0603-2M<br>(VSKY)       | 120 µm x 210 µm | 120 μm x 190 μm |

| CLP0805-2L<br>(VSKY)       | 330 µm x 400 µm | 115 μm x 400 μm |

| CLP1006-2L<br>(VSKY)       | 240 µm x 490 µm | 240 μm x 490 μm |

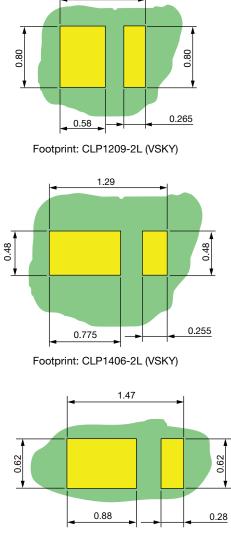

| CLP1209-2L<br>(VSKY)       | 580 µm x 800 µm | 265 µm x 800 µm |

| CLP1406-2L<br>(VSKY)       | 775 µm x 480 µm | 255 µm x 480 µm |

| CLP1608-2L<br>(VSKY)       | 880 µm x 620 µm | 280 µm x 620 µm |

Document Number: 85917

Revision: 01-Jul-2024

1 For technical questions, contact: <a href="mailto:Design-support@vishay.com">Design-support@vishay.com</a>

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

**Vishay Semiconductors**

The DNA of tech.

Soldering Recommendations for Chip Level Package (CLP)

### FOOTPRINT (in millimeters)

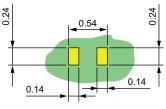

Footprint: CLP0603-2L (VBUS, VCUT)

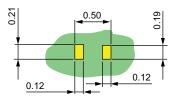

Footprint: CLP0603-2M (VSKY)

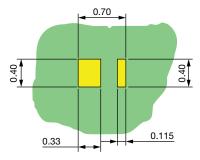

Footprint: CLP0805-2L (VSKY)

Revision: 01-Jul-2024

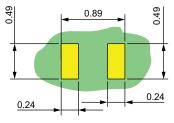

Footprint: CLP1006-2L (VSKY)

1.09

Footprint: CLP1608-2L (VSKY)

Easte abaired averation

For technical questions, contact: <u>Design-support@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

2

The DNA of tech.

## Soldering Recommendations for Chip Level Package (CLP)

#### PCB SOLDERING PAD METALLIZATION

There are several common soldering pad metallization / finishes, including organic solderability protectant (OSP), hot air solder level (HASL), and electroless nickel / immersion gold (ENiAu) over copper pad plating. For CLP products, Vishay only recommends ENiAu over copper pad plating.

#### AMOUNT OF SOLDER PASTE

There are different methods available for applying the solder paste to the PCB.

#### Screen Print Using a Stencil

Stencil screening of the solder paste onto the PCB is commonly used in the industry. Laser-cut openings with plasma treatment for good release of the solder paste are important features of the stencil in applying an accurate amount of solder paste onto the PCB.

Stencil thickness, openings, and opening design (radius) are all considerations in applying the right amount of solder paste onto the PCB.

# Recommendation for Amount of Solder Paste (Liquid State)

| TABLE 2: SOLDER PASTE AMOUNT (LIQUID) |                                              |                                              |

|---------------------------------------|----------------------------------------------|----------------------------------------------|

|                                       | VOLUME OF SOLDER PASTE                       |                                              |

|                                       | PAD 1<br>(10 <sup>-3</sup> mm <sup>3</sup> ) | PAD 2<br>(10 <sup>-3</sup> mm <sup>3</sup> ) |

| CLP0603-2L<br>(VBUS, VCUT)            | 2.02                                         | 2.02                                         |

| CLP0603-2M<br>(VSKY)                  | 1.51                                         | 1.37                                         |

| CLP0805-2L<br>(VSKY)                  | 7.92                                         | 2.76                                         |

| CLP1006-2L<br>(VSKY)                  | 7.06                                         | 7.06                                         |

| CLP1209-2L<br>(VSKY)                  | 27.84                                        | 12.72                                        |

| CLP1406-2L<br>(VSKY)                  | 22.3                                         | 7.34                                         |

| CLP1608-2L<br>(VSKY)                  | 32.7                                         | 10.4                                         |

#### Example of solder paste calculation based on:

CLP1608-2L / Pad 1 (large pad):

0.88 mm x 0.62 mm x 60  $\mu$ m stencil height = 32.7 x 10<sup>-3</sup> mm<sup>3</sup>

#### Ink Jet

Lately a new method for solder paste application has been established. Originally this application method had been developed for the soldering of through-hole devices (reflow instead of wave or hand soldering). However, the process is also available for solder paste amounts required for CLP products. The accuracy of jet printing and easy fine tuning of the solder paste amount are both advantage of the process.

For the amount of solder paste to be applied, see Table 2

### **RECOMMENDED SOLDER PASTE**

#### **Stencil Screening**

Use type 4 or higher (smaller ball size). In our evaluations we used the Cookson Electronics Alpha OM-338 CSP (96.5 % Sn / 3 % Ag / 0.5 % Cu) solder paste.

#### Ink Jet Application

Use type 5 or higher (smaller ball size). Usually ink jet equipment suppliers recommend the solder paste to be used. In our evaluations we used the Senju UK - M705 LFAC19 (96.5 % Sn / 3 % Ag / 0.5 % Cu).

**Vishay Semiconductors**

The DNA of tech.

# Soldering Recommendations for Chip Level Package (CLP)

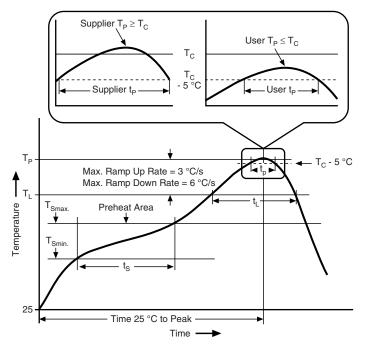

### **REFLOW SOLDERING PROCESS**

A standard surface-mount reflow soldering process can be used (reference: JPC/JEDEC® J-STD-020E).

However, for an optimum process, recommendations from the solder paste supplier should be considered. Variations in chemistry and viscosity of the fluxer may require small adjustments to the soldering profile.

Fig. 1 - Reflow Soldering profile according to JEDEC<sup>®</sup> - J-STD-020E

Document Number: 85917 🔳

The DNA of tech.

# Soldering Recommendations for Chip Level Package (CLP)

| TABLE 3 - CLASSIFICATION PROFILES                                                                        |                                                                                                                                                                    |                                                                                                                                                                    |  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PROFILE FEATURE                                                                                          | SnPb EUTECTIC ASSEMBLY                                                                                                                                             | LEAD (Pb)-FREE ASSEMBLY                                                                                                                                            |  |

| PREHEAT AND SOAK                                                                                         |                                                                                                                                                                    |                                                                                                                                                                    |  |

| Temperature min. (T <sub>Smin.</sub> )                                                                   | 100 °C                                                                                                                                                             | 150 °C                                                                                                                                                             |  |

| Temperature max. (T <sub>Smax.</sub> )                                                                   | 150 °C                                                                                                                                                             | 200 °C                                                                                                                                                             |  |

| Time (t <sub>S</sub> ) from (T <sub>Smin.</sub> to T <sub>Smax.</sub> )                                  | 60 s to 120 s                                                                                                                                                      | 60 s to 120 s                                                                                                                                                      |  |

| Ramp-up rate (T <sub>L</sub> to T <sub>p</sub> )                                                         | 3 °C/s max.                                                                                                                                                        | 3 °C/s max.                                                                                                                                                        |  |

| Liquidus temperature (TL)                                                                                | 183 °C                                                                                                                                                             | 217 °C                                                                                                                                                             |  |

| Time $(t_L)$ maintained above $(T_L)$                                                                    | 60 s to 150 s                                                                                                                                                      | 60 s to 150 s                                                                                                                                                      |  |

| Peak package body temperature (T <sub>p</sub> )                                                          | For users $T_p$ must not exceed the classification temperature in Table 4-1. For suppliers $T_p$ must equal or exceed the classification temperature in Table 4-1. | For users $T_p$ must not exceed the classification temperature in Table 4-2. For suppliers $T_p$ must equal or exceed the classification temperature in Table 4-2. |  |

| Time ( $t_p$ ) <sup>(1.)</sup> with 5 °C of the specified classification temperature ( $T_c$ ) see Fig.1 | 20 s                                                                                                                                                               | 30 s                                                                                                                                                               |  |

| Ramp-down rate ( $T_p$ to $T_L$ )                                                                        | 6 °C/s max.                                                                                                                                                        | 6 °C/s max.                                                                                                                                                        |  |

| Time 25 °C to peak temperature                                                                           | 6 min max.                                                                                                                                                         | 8 min max.                                                                                                                                                         |  |

#### Notes

1. Tolerance for peak profile temperature  $(T_p)$  is defined as a supplier minimum and a user maximum.

2. All temperatures refer to the center of the package, measured on the package body surface that is facing up during assembly reflow (e.g. live-bug). If parts are reflowed in other than the normal live bug assembly reflow orientation (i.e. dead-bug), T<sub>p</sub> shall be within ± 2 °C of the live-bug T<sub>p</sub> and still meet the T<sub>C</sub> requirements, otherwise, the profile shall be adjusted to achieve the latter. To accurately measure actual peak package body temperatures refer to JEP140 for the recommended thermocouple use.

3. Reflow profiles in this document are for classification / preconditioning and are not meant to specify board assembly profiles. Actual board assembly profiles should be developed based on specific process needs and board designs and should not exceed the parameters in this table. For example, if T<sub>C</sub> is 260 °C and time t<sub>p</sub> is 30 s, this means the following for the supplier and the user:

- For a supplier: the peak temperature must be at least 260 °C. The time above 255 °C must be at least 30 s.

- For a user: the peak temperature must not exceed 260 °C. The time above 255 °C must not exceed 30 s.

4. All components in the test load shall meet the classification profile requirements.

5. SMD packages classified to a given moisture sensitivity level by using procedures or criteria defined within any previous version of J-STD-020, JESD22-A112 (rescinded), IPC-SM-786 (rescinded) do not need to be reclassified to the current revision unless a change in classification level or a higher peak classification temperature is desired.

| TABLE 4-1 - SnPb EUTECTIC PROCESS - CLASSIFICATION TEMPERATURES (T <sub>C</sub> ) |                              |                              |

|-----------------------------------------------------------------------------------|------------------------------|------------------------------|

| PACKAGE THICKNESS                                                                 | VOLUME mm <sup>3</sup> < 350 | VOLUME mm <sup>3</sup> ≥ 350 |

| < 2.5 mm                                                                          | 235 °C                       | 220 °C                       |

| ≥ 2.5 mm                                                                          | 220 °C                       | 220 °C                       |

| TABLE 4-2 - LEAD (Pb)-FREE PROCESS - CLASSIFICATION TEMPERATURES (T <sub>c</sub> ) |                              |                                    |                                      |

|------------------------------------------------------------------------------------|------------------------------|------------------------------------|--------------------------------------|

| PACKAGE THICKNESS                                                                  | VOLUME mm <sup>3</sup> < 350 | VOLUME mm <sup>3</sup> 350 to 2000 | <b>VOLUME</b> mm <sup>3</sup> > 2000 |

| < 1.6 mm                                                                           | 260 °C                       | 260 °C                             | 260 °C                               |

| 1.6 mm to 2.5 mm                                                                   | 260 °C                       | 250 °C                             | 245 °C                               |

| > 2.5 mm                                                                           | 250 °C                       | 245 °C                             | 245 °C                               |

#### Notes

Package volume excludes external terminals (e.g., balls, bumps, lands, leads) and / or non-integral heatsinks. Package volume includes the external dimensions of the package

At the direction of the device manufacturer, but not the heard assembler / user, the maximum neak package body temperature (T.) can

2. At the direction of the device manufacturer, but not the board assembler / user, the maximum peak package body temperature ( $T_p$ ) can exceed the values specified in tables 2 and 3. The use of a higher  $T_p$  does not change the classification temperature ( $T_c$ ).

3. The maximum component temperature reached during reflow depends on package thickness and volume. The use on convection reflow processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD packages may still exist.

4. Moisture sensitivity levels of components intended for use in a lead (Pb)-free assembly process shall be evaluated using the lead (Pb)-free classification temperatures and profiles defined in table 4-1 and 4-2, whether or not lead (Pb)-free.

5. SMD packages classified to a given moisture sensitivity level by using procedures or criteria defined within any previous version of J-STD-020, JESD22-A112 (rescinded), or IPC-SM-786 (rescinded) do not need to be reclassified to the current revision unless a change in Classification level or a higher peak classification temperature is desired.

| Revision: | 01-Jul-2024 |

|-----------|-------------|

|-----------|-------------|

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

Document Number: 85917

⊳ פ

U

$\mathbf{\Sigma}$

0

The DNA of tech.

## Soldering Recommendations for Chip Level Package (CLP)

#### SOLDERING QUALITY INSPECTION

www.vishay.com

An X-ray inspection system is required to find defects such as shorts between pads, open contacts, and voids within the solder.

#### **REWORK PROCEDURE**

For rework, the CLP package must be removed from the PCB if there is any issue with the solder joints. Standard SMT rework systems are recommended for this. Due to the small size of the package, the rework system should be equipped with a proper magnification aid.

### INTERCHANGEABILITY OF THE CLP PRODUCTS WITH A PLASTIC PACKAGE OF THE SAME SIZE

Based on our studies, the CLP is 100 % compatible with competitor's products, and exchangeable with plastic packages of the same size and foot print.