VISHAY SEMICONDUCTORS

www.vishay.com

### **Diodes and Rectifiers**

Application Note

# **Soldering Recommendations for Power DFN Packages**

By Ida Li, Joden Liu, and Robert Bai

#### INTRODUCTION

In order to support customers' downsizing programs in many applications, such as automotive, industrial, telecom, and mobile, Vishay offers new Power DFN series leadless packages, which help to maximize board space and enhance thermal performance. In addition, to fulfill automated optical inspection (AOI) requirements, the packages' lead sidewall is wettable. This application note provides recommendation for the handling of Vishay Power DFN packages during PCB assembly, in order to help customers avoid trial and error in PCB design and reflow process tuning.

#### PCB SOLDER MASK DESIGN

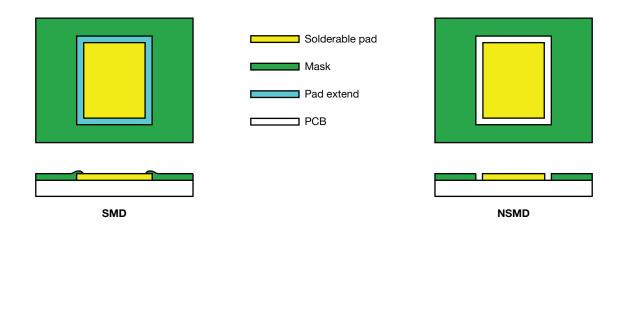

Two types of PCB solder mask openings are commonly used for surface-mount leadless packages:

- 1. Non solder mask defined (NSMD): contact pads have the solder mask pulled away from the solderable metallization

- 2. Solder mask defined (SMD): contact pads have the solder mask over the edge of the metallization

With SMD pads, the solder mask restricts the flow of solder paste to the top of the metallization, preventing the solder from flowing along the sides of the metal pad. This is different from the NSMD pads, in which the solder will flow around both the top and the sides of the metallization.

Both solder mask designs can be used. The solderable area of the center pad, as defined by the solder mask (SMD or NSMD), should match the size of the ePAD of the component. The PCB solder land design selection is made based on the design rule applied by the customer.

⋗

Revision: 19-Dec-2023 1 Document Number: 98535 ☐ For technical questions within your region: <u>DiodesAmericas@vishay.com</u>, <u>DiodesAsia@vishay.com</u>, <u>DiodesEurope@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Vishay Semiconductors

The DNA of tech.

Soldering Recommendations for Power DFN Packages

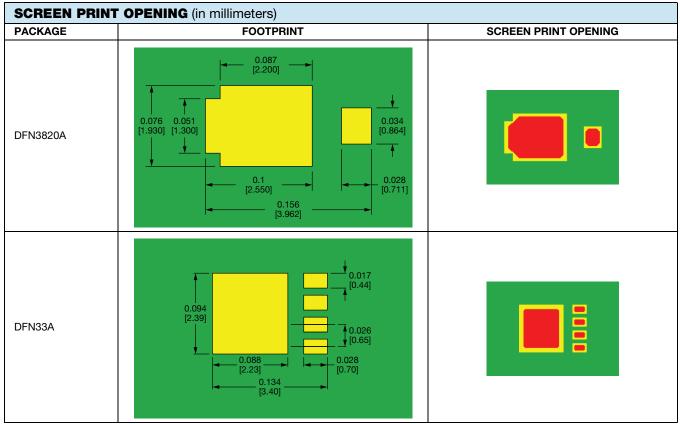

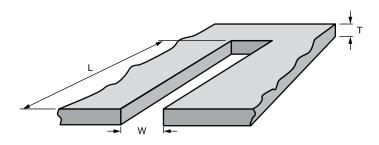

Stencil screening the solder on the PCB is common practice in the industry. The sidewalls of the stencil openings should be tapered to approximately 5° to ease the release of the paste when the stencil is removed from the PCB.

The general stencil design rule should be followed to ensure a safe and repeatable stencil printing process:

- Aspect ratio (AS) = width of the aperture / thickness of the stencil foil = W/T > 1.5

- Area ratio (AR) = area of the aperture opening / area of aperture walls = (W x L) / (2T x (W+L)) > 0.66

Depending on the customer's application (components of different sizes can require more or less solder paste), the stencil thickness may vary. According to the stencil thickness that the user will use, the stencil opening has to be adjusted to use the recommended amount of solder paste.

With an insufficient amount of solder paste, the lifetime of the solder joint will be affected.

With an excess of solder, AOI performance may be affected. In the worst case scenario, bridging solder will cause an electrical failure (short).

The DNA of tech.

Soldering Recommendations for Power DFN Packages

#### SCREEN PRINT USING A STENCIL

Stencil screening of the solder paste onto the PCB is a common practice in the industry. In order to apply an accurate amount of solder paste onto the PCB, laser-cut openings with plasma treatment for good release of the solder paste are important features of the stencil.

Stencil thickness, openings, and opening design (radius) are all considerations in applying the right amount of solder paste onto the PCB.

#### **RECOMMENDED SOLDER PASTE**

#### Stencil Screening

Use type 4 or higher (smaller ball size). In our evaluations we used the Cookson Electronics Alpha OM-338 (96.5 % Sn / 3 % Ag / 0.5 % Cu) solder paste.

#### **REFLOW SOLDERING PROCESS**

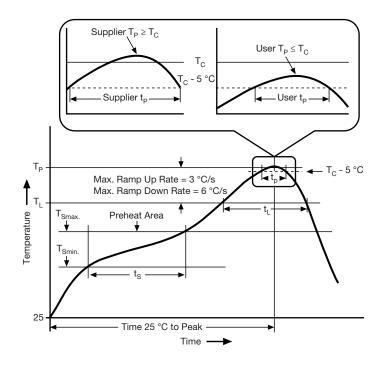

A standard surface-mount reflow soldering process can be used (reference: JPC / JEDEC® J-STD-020E).

Vishay Semiconductors

The DNA of tech.

**Soldering Recommendations for Power DFN Packages**

| TABLE 1 - CLASSIFICATION PROFILES                                                |                                           |                                           |  |  |  |

|----------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--|--|--|

| PROFILE FEATURE                                                                  | SnPb EUTECTIC ASSEMBLY                    | LEAD (Pb)-FREE ASSEMBLY                   |  |  |  |

| PREHEAT AND SOAK                                                                 |                                           |                                           |  |  |  |

| Temperature min. (T <sub>Smin.</sub> )                                           | 100 °C 150 °C                             |                                           |  |  |  |

| Temperature max. (T <sub>Smax.</sub> )                                           | 150 °C                                    | 200 °C                                    |  |  |  |

| Time (t <sub>S</sub> ) from (T <sub>Smin.</sub> to T <sub>Smax.</sub> )          | 60 s to 120 s 60 s to 120 s               |                                           |  |  |  |

| Average ramp-up rate (T <sub>Smax.</sub> to T <sub>p</sub> )                     | 3 °C/s max.                               |                                           |  |  |  |

| Liquidus temperature (TL)                                                        | 183 °C                                    | 217 °C                                    |  |  |  |

| Time to liquidus (t <sub>L</sub> )                                               | 60 s to 150 s                             | 60 s to 150 s                             |  |  |  |

| Peak package body temperature $(T_p)^{(1)}$                                      | See classification temperature in Table 2 | See classification temperature in Table 3 |  |  |  |

| Time $(t_p)^{(2)}$ with 5 °C of the specified classification temperature $(T_C)$ | 20 s <sup>(2)</sup> 30 s <sup>(2)</sup>   |                                           |  |  |  |

| Average ramp-down rate (Tp to TSmax.)                                            | 6 °C/s max.                               |                                           |  |  |  |

| Time 25 °C to peak temperature                                                   | 6 min max. 8 min max.                     |                                           |  |  |  |

#### Notes

<sup>(1)</sup> The tolerance for peak profile temperature (T<sub>p</sub>) is defined as a supplier minimum and a user maximum

$^{(2)}$  The tolerance for time at peak profile temperature (T<sub>p</sub>) is defined as a supplier minimum and user maximum

| TABLE 2 - SnPb EUTECTIC PROCESS - CLASSIFICATION TEMPERATURES (T <sub>c</sub> ) |                              |                              |  |  |

|---------------------------------------------------------------------------------|------------------------------|------------------------------|--|--|

| PACKAGE THICKNESS                                                               | VOLUME mm <sup>3</sup> < 350 | VOLUME mm <sup>3</sup> ≥ 350 |  |  |

| < 2.5 mm                                                                        | 235 °C                       | 220 °C                       |  |  |

| ≥ 2.5 mm                                                                        | 220 °C                       | 220 °C                       |  |  |

| TABLE 3 - LEAD (Pb)-FREE PROCESS - CLASSIFICATION TEMPERATURES (T <sub>c</sub> ) |                              |                                    |                               |  |  |

|----------------------------------------------------------------------------------|------------------------------|------------------------------------|-------------------------------|--|--|

| PACKAGE THICKNESS                                                                | VOLUME mm <sup>3</sup> < 350 | VOLUME mm <sup>3</sup> 350 to 2000 | VOLUME mm <sup>3</sup> > 2000 |  |  |

| < 1.6 mm                                                                         | 260 °C                       | 260 °C                             | 260 °C                        |  |  |

| 1.6 mm to 2.5 mm                                                                 | 260 °C                       | 250 °C                             | 245 °C                        |  |  |

| > 2.5 mm                                                                         | 250 °C                       | 245 °C                             | 245 °C                        |  |  |

#### Notes

Package volume excludes external terminals (e.g., balls, bumps, lands, leads) and / or non-integral heatsinks

The maximum component temperature reached during reflow depends on package thickness and volume. The use of convection reflow

processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD

packages may still exist.

Moisture sensitivity levels of components intended for use in a lead (Pb)-free assembly process shall be evaluated using the lead (Pb)-free classification temperatures and profiles defined in Table 3, whether or not lead (Pb)-free

Recommended soldering process in accordance with J-STD-020E

Document Number: 98535 🔳

The DNA of tech.

## Soldering Recommendations for Power DFN Packages

#### **AOI CAPABLE**

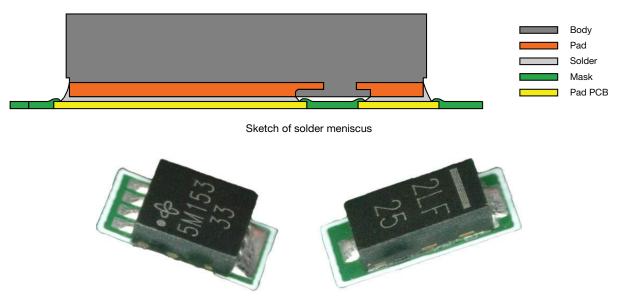

The solderable sidewall / flanks (with guaranteed Sn plating thickness, the same as on the bottom side) enable customers to use AOI with a camera instead of an X-ray system. With a proper PCB footprint design (extended on both sides) and right amount of solder paste, a homogenous solder meniscus will be formed after reflow soldering.

This solder meniscus can be inspected / measured with an optical camera system to judge for a proper soldering result.

Real picture of DFN33A and DFN3820A after reflow soldering showing meniscus

#### WETTABLE SIDEWALL PLATED SOLDER PADS ON DFN33A AND DFN3820A

Wettable sidewall plated solder pads

Sketch of solder meniscus

- Side-wettable flanks for easy AOI

- Robust solder joints, high reliability

APPLICATION NOTE

Revision: 19-Dec-2023

5

Document Number: 98535 п

For technical questions within your region: <u>DiodesAmericas@vishay.com</u>, <u>DiodesAsia@vishay.com</u>, <u>DiodesEurope@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>