## Design High Frequency, Higher Power Converters With Si9166

by Kin Shum

#### INTRODUCTION

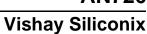

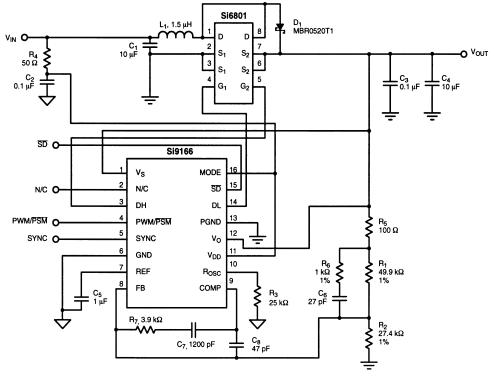

The Si9166 is a controller IC designed for dc-to-dc conversion applications with 2.7-V to 6-V input voltage. Like its sister device, the Si9165, the Si9166 provides operation with high operating frequencies, high efficiency, a high level of integration, and low-noise performance. The key difference from the Si9165 is that the Si9166 uses external MOSFETs, which gives designers more flexibility in increasing the power level of dc-to-dc conversion circuitry. The Si9166 can be easily configured as a synchronous buck or a boost converter with external MOSFETs operating at switching frequencies as high as 2 MHz, which enables smaller and lighter designs. High efficiency can be preserved at light load by running the converter in Pulse Skipping Modulation (PSM) mode.

Key functions of the Si9166 controller are discussed in the "Description" section of the data sheet. In this application note, additional information is provided, including design guidelines for both buck and boost configurations. Some test results are also presented. Note that the tips provided apply only to designing with the Si9166 controller. Please review Siliconix application notes AN715 and AN710 for more general design guidelines.

#### IC DESCRIPTION

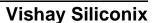

The Si9166 is a BiCMOS controller for dc-to-dc conversion applications. A functional block diagram of the IC internal structure is shown in Figure 1.

FIGURE 1.

# VISHAY

#### Start-Up/UVLO

The internal under voltage lock out (UVLO) circuit keeps most of the IC function blocks off until the supply voltage ( $V_{DD}$ ) increases above 2.4 V. A 100-mV hysteresis is built in to the UVLO point, so the controller will be functional until  $V_{DD}$  drops below 2.3 V. This helps to eliminate the IC from bouncing between ON and OFF stages. After the IC is turned ON, it takes about 4 ms for the POR to be ready, the error amp output to charge up, and the output voltage to start ramping up. The output voltage will need an additional 3 to 4 ms to reach regulation, depending on load condition.

#### **By-Pass Mode**

When using the Si9166, the output voltage regulation point can be set within the input voltage range, regardless of whether a buck or boost configuration is being used. For instance, for an input range of 2.7 V to 4.2 V, the output voltage could be set to 3.3 V.

For a boost converter, when the input is higher than 3.3 V, the duty cycle of the switch stays at 0%, and the output voltage follows the input voltage by a voltage drop consisting of inductor resistance and MOSFET (in PWM mode) or diode (in PSM mode) drop. When the input decreases and approaches 3.3 V, the output drops to the regulation point, and the main switch starts to switch at a minimum duty cycle to keep the output regulated at 3.3 V. This duty cycle increases as the input voltage decreases. In some instances, noise can be generated during the transition because there is a minimum controllable duty cycle for any PWM controller. The frequency and amplitude of this transition noise vary depending on the compensation network. The wider the loop bandwidth (BW), the higher the switching frequency and the lower the output ripple.

For a buck converter, when input voltage is higher than 3.3 V, it is stepped down to 3.3 V at the output. As the input decreases and approaches 3.3 V, the switching duty cycle increases to the maximum duty cycle, jumping to 100% and making the high-side switch work like a saturated linear regulator. The output voltage will simply follow the input voltage by the saturation voltage until the input drops below the UVLO voltage or until another user-defined control signal disables the converter. The same noise considerations as for a boost converter apply in this case.

#### **Buck/Boost Configuration**

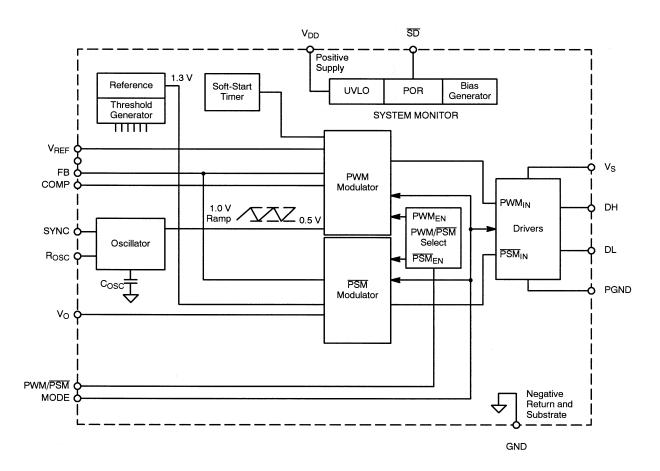

The Si9166 can be easily configured to function as a step-down (buck) or a step-up (boost) converter. Figures 2 and 3 show the typical application circuit for buck and boost converters, respectively. The list in Table 1 shows the key IC connection differences in the two topologies.

TABLE 1. Buck and Boost Pin Connection Comparison

| Name of Pin    | Buck  | Boost  |

|----------------|-------|--------|

| Mode           | Low   | High   |

| V <sub>S</sub> | Input | Output |

#### **DESIGN GUIDELINES**

Following are some design guidelines for buck and boost converters. Key components required for a complete converter design are MOSFETs, an inductor, input/output capacitors, and a compensation network.

#### **MOSFET Selection**

The switching frequency needs to be determined at the beginning of the design. High switching frequencies allow the use of smaller L/C power stage filters without sacrificing current/voltage ripple characteristics or increasing conduction losses. In addition, fast switching cycles help speed up transient response times. High switching frequencies are often associated with high gate charge and crossover switching losses, which can impair converter efficiency. However, conversion efficiency can be optimized by properly setting the switching frequency and careful selection of the power MOSFETs.

The key selection criteria for the MOSFETs include maximum specifications for on-resistance, drain-source voltage, gate-source, current, and total gate charge  $Q_g$ . While the voltage ratings are fairly straightforward, it is important to carefully balance on-resistance and gate charge. In typical MOSFETs, the lower the on-resistance, the higher the gate charge. The power loss of a MOSFET consists of conduction losses, gate charge losses, and crossover losses. For lower-current application, gate charge losses become a significant factor, so low gate charge MOSFETs, such as Vishay Siliconix's LITTLE FOOT family of PWM-optimized devices, are desirable.

The Si9166 is designed to drive a pair of external p- and n-channel MOSFETs. The Si6801DQ is a PWM-optimized low gate charge complementary p-n MOSFET pair. It is the perfect choice for current levels of 1.2 A or lower, while the sibling Si6803DQ is the perfect choice for current levels up to about 1.8 A.

FIGURE 2. Buck Configuration

FIGURE 3. Boost Configuration

#### **Inductor Selection**

An inductor is the energy storage component in a converter. Choosing an inductor means specifying its size, structure, material, inductance, saturation level, dc-resistance (DCR), and core loss. Fortunately, there are many inductor vendors that offer wide selections with ample specifications and test data, such as Vishay Dale, Coilcraft, Coiltronics, and Sumida. The following are some key parameters that users should focus on.

In PWM mode, inductance has a direct impact on the ripple current. The peak-to-peak inductor ripple current can be calculated as

For Buck,

$$I_{p-p} = \frac{V_{OUT}(V_{IN} - V_{OUT})}{V_{IN}Lf}$$

(1)

For Boost,

$$I_{p-p} = \frac{V_{IN}(V_{OUT} - V_{IN})}{V_{OUT}Lf}$$

(2)

where f = switching frequency.

Higher inductance means lower ripple current, lower rms current, lower voltage ripple on both input and output, and higher efficiency, unless the resistive loss of the inductor dominates the overall conduction loss. However, higher inductance also means a bigger inductor size and a slower response to transients. In PSM mode, inductance affects inductor peak current, and consequently impacts the load capability and switching frequency. For fixed line and load conditions, higher inductance results in a lower peak current for each pulse, a lower load capability, and a higher switching frequency.

The saturation level is another important parameter in choosing inductors. Note that the saturation levels specified in data sheets are maximum currents. For a dc-to-dc converter operating in PWM mode, it is the maximum peak inductor current that is relevant, and which can be calculated using these equations:

For Buck,

$$I_{pk} = I_{OUT} + \frac{I_{p-p}}{2}$$

(3)

For Boost,

$$I_{pk} = \frac{V_{OUT}I_{OUT}}{\eta V_{IN}} + \frac{I_{p-p}}{2}$$

(4)

where  $\eta$  = converter efficiency.

This peak current varies with inductance tolerance and other errors, and the rated saturation level varies over temperature. So a sufficient design margin is required when choosing current ratings.

A high-frequency core material, such as ferrite, should be chosen, since at 2 MHz, the core loss could lead to serious

efficiency penalties. The DCR should be kept as low as possible to reduce conduction losses.

With a switching frequency (Fsw) capability as high as 2 MHz, the Si9166 allows use of small surface-mount inductors which are essential for compact cellular phone designs. The recommended inductance at a 2-MHz Fsw is 1.5  $\mu$ H, which offers a good balance between size, ripple current, and efficiency. When a lower switching frequency is chosen, higher inductance is required to match the efficiency and ripple performance at 2 MHz. For instance, a 3- $\mu$ H inductor is preferred for a 1-MHz switching frequency. In PSM mode, however, the operation is affected by inductance value but not the switching frequency.

#### Input/Output Capacitor Selection

Low-ESR (Effective Series Resistance) capacitors are required on both the input and output to minimize voltage ripple. The ESR of the output capacitor also changes the loop stability, and it will be discussed later. At a 2-MHz Fsw, a 10-µF surface-mount ceramic capacitor is recommended at the output of the Si9166. A 10-µF ceramic or 22-µF low-ESR tantalum capacitor is recommended as the input filtering capacitor. Of course, the voltage rating on capacitor must not be neglected.

#### **Diode Selection**

To maximize converter efficiency, the use of an external Schottky diode is strongly recommended over utilizing the internal body diode of the MOSFET, which will typically have a higher forward voltage drop by comparison. The Schottky diode must be connected across the synchronous rectifying switch. In PWM mode, it carries the inductor current flow during BBM time; in PSM mode, this diode conducts all the time during inductor discharge since the rectifier switch is turned off during PSM. A low forward drop diode is preferable for its efficiency advantages and fast recovery times, which help reduce high-frequency noise.

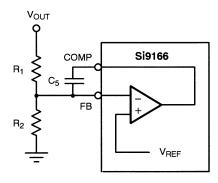

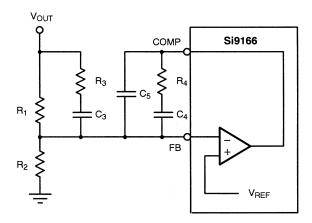

#### **Compensation Network**

Voltage mode control is used in the Si9166 for both buck and boost converter configurations. The output voltage is sensed and fed back (pin 10, FB) to be compared with a reference voltage. The difference is amplified by the internal error amplifier. Then the output of the error amp (pin 11, COMP) is compared with a fixed ramp signal (see Figure 1), and the comparator output is a controlled pulse width used to drive the switches. As the switching duty cycle varies, the output voltage is regulated. This single control loop needs to be compensated so that the converter meets following specifications:

- · Control loop stability margin

- Overshoot/undershoot at the output voltage induced by load and line transients

- · Settling time for overshoot/undershoot

# VISHAY

## **Vishay Siliconix**

FIGURE 4. Type I Compensation Network

The peak overshoot/undershoot voltage is determined by closed-loop output impedance (Zo). The higher the output impedance, the higher the peak. Although heavily dependent on output capacitance and inductance, Zo is also closely related to closed loop gain. With fixed power stage components, a control loop with high bandwidth (BW) has low Zo. Improving the compensation network is more cost-effective than increasing the size of the output capacitor and inductor. Fast settling times also rely on good loop design with high BW. Adding capacitance at the output of the power supply can reduce the peak deviation, but it can also produce several unintended results, including low BW, long settling times, reduced phase margin, and even system instability.

For voltage-mode control, a simple Type I compensation network can easily stabilize the loop but at a cost of lower BW, which has to be at least one decade below the L-C corner frequency to preserve a good stability margin. However, Type III compensation, a more complicated design, enables higher BW even above the L-C double-pole. This double pole is straight forward for a buck converter, but more complicated for a boost converter, in which input and output conditions vary. The formula for this double pole is shown in (5).

$$f_{double-pole} = \frac{V_{IN}}{2\pi V_{OUT} \sqrt{LC}}$$

(5)

As this double pole shifts to lower frequencies, the phase delay also comes in at a lower frequency, making it difficult to cross over with the same BW. Another troublesome feature of boost power stages are their right-half-plane (RHP) zero, which can create difficulties for power supply designers. This RHP zero also varies with operating conditions as shown in (6).

$$f_{RHP-zero} = \frac{V_{IN}^2}{2\pi V_{OUT}I_{OUT}L}$$

(6)

When high boost ratios and heavy loads are required, this zero can move to low frequency. The negative effect of this is

FIGURE 5. Type III Compensation Network

that it results in gain boost with an extra phase delay that will introduce instability into the loop gain.

For both buck and boost converters, the close loop design goal with Type III compensation is to have the final loop gain crossing over after the worst case (lowest) double-pole. To achieve this, two zeroes are required before the double-pole to build up phase boost. The two poles should be placed one decade after the best case (highest) crossover frequency to avoid any phase dragging.

The divider resistor pair, R1 and R2 in Figure 3 and R2 and R4 in Figure 2, determine the output regulation point. Since R1 is part of the compensation network, Vishay Siliconix recommends adjusting R2 to change the regulation voltage without affecting the loop gain. With fixed R1, R2 can be easily calculated by (7) for the desired output voltage setting.

$$R_2 = \frac{R_1}{\frac{V_{OUT}}{V_{REE}} - 1} \tag{7}$$

The typical value for V<sub>REF</sub> is 1.3 V.

#### **Layout Issues**

One of the very few drawbacks of switching power supplies is the noise level induced by their high-frequency switching performance. Parasitic inductance and junction capacitance become significant noise sources when a converter is switching at megahertz frequencies. However, noise levels can be minimized by properly laying out the components. Here are some tips for laying out buck and boost converters with the Si9166 controller.

Minimize power traces. Since most power traces, in both buck and boost converters, carry pulsating current, energy stored in trace inductance during the pulse will be released when the pulse current stops, causing high frequency ringing with junction capacitor of the MOSFETs/diode or even the input/output capacitor. Designers will need to keep external power traces as short as possible, including the trace from input/output capacitor to the switch, inductor to

switch, inductor to input/output capacitor, and, of course, the ground trace.

- The decoupling capacitor V<sub>DD</sub> has to be as close as possible to the pin to reduce the noise on this power source for the internal logic circuit.

- The V<sub>S</sub> pin has to be close to input or output capacitor for buck or boost converters, respectively, to provide enough gate drive current without sacrificing much driving voltage. If this creates an impossible layout situation, designers may want to consider adding a 1-µF ceramic capacitor at the V<sub>S</sub> pin, depending on the noise level.

- A high-frequency capacitor, normally a 0.1-µF ceramic capacitor, is recommended across the sources of the two MOSFETs-right at the pins if possible-to reduce highfrequency noise. The impedance of these capacitors is lower at high frequencies compared with higher-value capacitors.

- To keep the gate signal clean, they have to be placed away from the inductor, since the alternating magnetic field is the primary noise source in a switching converter.

See Si9166 buck and boost demo board layout as examples.

#### Other Issues

Sometimes higher input capacitance values are required when ultra-high-speed, large-scale load transients occur at a 2.7-V or lower input voltages. If the voltage level at  $V_{DD}$  drops below 2.3 V, the UVLO circuit will instantaneously shut off the IC and collapse the output. Best results can be achieved when a higher-value R-C filter is used on  $V_{DD}$  pin in conjunction with higher input capacitance.

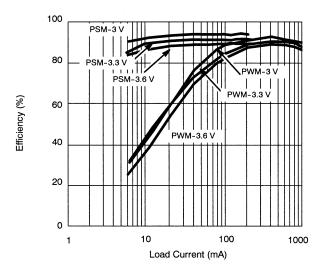

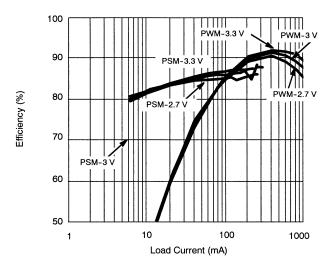

The PSM feature is designed to increase efficiency under light load conditions and extend battery life. It does not offer an efficiency advantage over PWM mode when the load exceeds 100 mA and a 1.5-µH inductor is used. (Efficiency data is given in the "Experimental Results" section.) However, with a maximum of 1.5-µH inductance, the Si9166 PSM mode guarantees output regulation up to a 150-mA load for both buck and boost converters under any input/output condition.

#### **EXPERIMENTAL RESULTS**

The Si9166 controller has been fully tested in both buck and boost modes on demo boards. Some test results are summarized here.

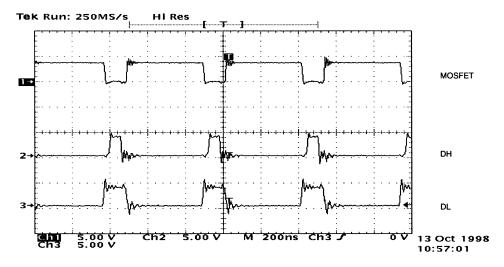

#### **Typical Waveforms**

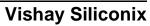

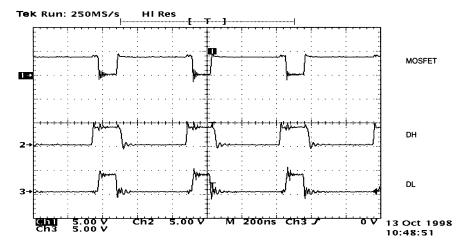

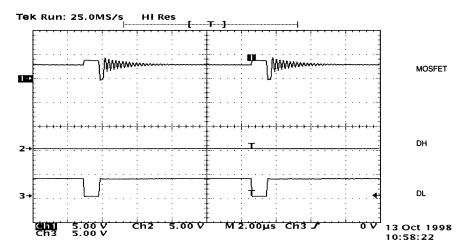

For the waveforms shown, the channel lineup from top to bottom is:

- Channel 1 MOSFET drain (pin 1 and 8)

- Channel 2 High side switch drive (Si9166 pin 3)

- Channel 3 Low side switch drive (Si9166 pin 14)

**FIGURE 6.** Buck DB PWM Mode:  $V_{IN} = 3.6 \text{ V}$ ,  $V_{O} = 2.7 \text{ V}$ , Load = 200 mA

**FIGURE 7.** Buck DB PWM Mode:  $V_{IN} = 3 \text{ V}$ ,  $V_{O} = 3.6 \text{ V}$ , Load = 200 mA

**FIGURE 8.** Buck DB PSM Mode:  $V_{IN} = 3.6 \text{ V}$ ,  $V_{O} = 2.7 \text{ V}$ , Load = 20 mA

**FIGURE 9.** Buck DB PSM Mode:  $V_{IN} = 3.0 \text{ V}$ ,  $V_O = 3.6 \text{ V}$ , Load = 20 mA

### **Efficiency**

**FIGURE 10.** Buck Mode Efficiency w/  $V_{OUT} = 2.7 \text{ V}$

**FIGURE 11.** Bost Mode Efficiency w/  $V_{OUT} = 3.6 \text{ V}$