## New Product

Si4738CY

**Vishay Siliconix**

# N-Channel Synchronous MOSFETs With Break-Before-Make

#### FEATURES

- 0- to 20-V Operation

- Under-Voltage Lockout

- Shoot Through Resistant

- Fast Switching Times

- SO-16 Package

- Driver Impedance—3 Ω

- 20-V MOSFETs

- High Side: 0.010  $\Omega$  @ V\_DD = 4.5 V

- Low Side: 0.006  $\Omega$  @ V\_DD = 4.5 V

- Switching Frequency: 250 kHz to 1 MHz

#### DESCRIPTION

The Si4738CY n-channel synchronous MOSFET with break-before-make (BBM) is a high speed driver designed to operate in high frequency dc-dc switch-mode power supplies. It's purpose is to simplify the use of n-channel MOSFETs in high frequency buck regulators. This device is designed to be used with any single output PWM IC or ASIC to produce a highly efficient, low cost, synchronous rectifier converter.

The LITTLE FOOT *Plus* <sup>™</sup> Drivers Si4738DY is packaged in Vishay-Siliconix's high-performance SO-16 package.

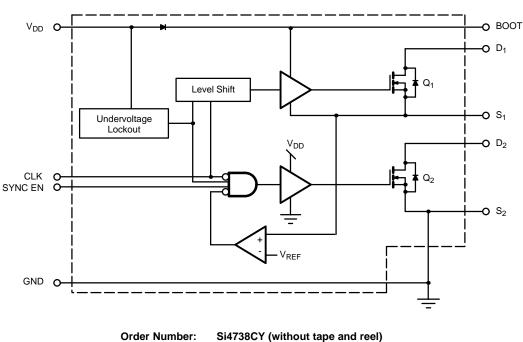

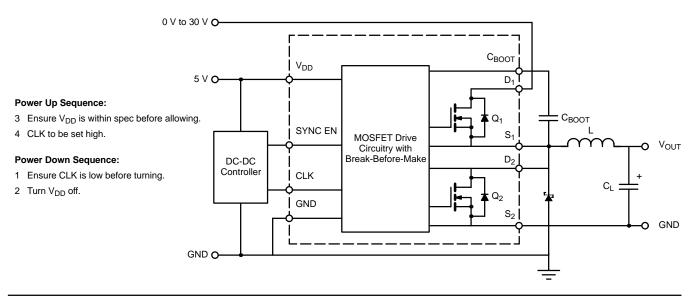

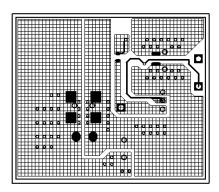

## **FUNCTIONAL BLOCK DIAGRAM**

Si4738CY-T1 (with tape and reel)

**Vishay Siliconix**

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25 $^{\circ}$ C UNLESS OTHERWISE NOTED) |                                   |                                   |                               |      |  |

|------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|-------------------------------|------|--|

| Parameter                                                                          |                                   | Symbol                            | Steady State                  | Unit |  |

| Logic Supply                                                                       |                                   | V <sub>DD</sub>                   | 7                             | v    |  |

| Logic Inputs                                                                       |                                   | V <sub>IN</sub>                   | -0.7 to V <sub>DD</sub> + 0.3 |      |  |

| Drain Voltage                                                                      |                                   | V <sub>D1</sub>                   | 20                            |      |  |

| Bootstrap Voltage                                                                  |                                   | V <sub>BOOT</sub>                 | V <sub>S1</sub> + 7           |      |  |

|                                                                                    | $T_A = 25^{\circ}C$               |                                   | 8.9                           |      |  |

|                                                                                    | $T_A = 70^{\ensuremath{\oplus}}C$ | I <sub>D1</sub>                   | 7.1                           |      |  |

| Continuous Drain Current (T <sub>J</sub> = 150 <sup>®</sup> C) <sup>a</sup>        | $T_A = 25^{\ensuremath{\oplus}}C$ |                                   | 14.29                         | A    |  |

|                                                                                    | $T_A = 70^{\circ}C$               | I <sub>D2</sub>                   | 11.43                         |      |  |

| Maximum Power Dissipation <sup>a</sup>                                             |                                   | PD                                | 1.2                           | W    |  |

|                                                                                    | Driver                            |                                   | -65 to 125                    |      |  |

| Operating Junction and Storage Temperature Range                                   | MOSFETs                           | T <sub>j</sub> , T <sub>stg</sub> | -65 to 150                    | °C   |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING CONDITIONS |                   |                                          |      |  |

|----------------------------------|-------------------|------------------------------------------|------|--|

| Parameter                        | Symbol            | Steady State                             | Unit |  |

| Drain Voltage                    | V <sub>D1</sub>   | 0 to 20                                  |      |  |

| Logic Supply                     | V <sub>DD</sub>   | 4.5 to 5.5                               | v    |  |

| Input Logic High Voltage         | V <sub>IH</sub>   | 0.6 x V <sub>DD</sub> to V <sub>DD</sub> | v    |  |

| Input Logic Low Voltage          | V <sub>IL</sub>   | -0.3 to 0.3 x V <sub>DD</sub>            |      |  |

| Bootstrap Capacitor              | C <sub>BOOT</sub> | 100 n to 1 μ                             | F    |  |

| Ambient Temperature              | T <sub>A</sub>    | -40 to 85                                | °C   |  |

| THERMAL RESISTANCE RATINGS                      |              |                    |         |         |      |

|-------------------------------------------------|--------------|--------------------|---------|---------|------|

| Parameter                                       |              | Symbol             | Typical | Maximum | Unit |

| High-Side Junction-to-Ambient <sup>a</sup>      |              | R <sub>thJA1</sub> | 85      | 105     |      |

| Low-Side Junction-to-Ambient <sup>a</sup>       | Steady State | R <sub>thJA2</sub> | 68      | 85      |      |

| High-Side Junction-to-Foot (Drain) <sup>b</sup> |              | R <sub>thJF1</sub> | 24      | 30      | °C/W |

| Low-Side Junction-to-Foot (Drain) <sup>b</sup>  |              | R <sub>thJF2</sub> | 16      | 20      |      |

Notes

Junction-to-foot thermal impedance represents the effective thermal impedance of all heat carrying leads in parallel and is intended for use in conjunction with the thermal impedance of the PC board pads to ambient ( $R_{thJA} = R_{thJF} + R_{thPCB-A}$ ). It can also be used to estimate chip temperature if power dissipation and the lead temperature of a heat carrying (drain) lead is known. b.

Surface mounted on 1" x1" FR4 board, 0.062" thick, 2-oz copper double sided. a.

## **New Product**

# Vishay Siliconix

|                                                      |                       | Test Conditions Unless Specified<br>$T_A = 25^{\circ}$ 4.5 V < V <sub>DD</sub> <5.5 V, 4.5 V < V <sub>D1</sub> <20 V                       |                         | Limits |                  |      |          |

|------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|------------------|------|----------|

| Parameter                                            | Symbol                |                                                                                                                                            |                         | Min    | Typ <sup>a</sup> | Max  | Unit     |

| Power Supplies                                       | •                     |                                                                                                                                            |                         |        |                  |      |          |

| Logic Voltage                                        | V <sub>DD</sub>       |                                                                                                                                            |                         | 4.5    |                  | 5.5  | V        |

|                                                      | I <sub>DD(EN)</sub>   | V <sub>DD</sub> = 4.5 V, V <sub>CLK, SYNC</sub> = 4.5 V<br>V <sub>DD</sub> = 4.5 V, V <sub>CLK</sub> , <sub>SYNC</sub> = 0 V               |                         |        | 280              | 500  | μΑ       |

| Logic Current (Static)                               | I <sub>DD(DIS)</sub>  |                                                                                                                                            |                         |        | 220              | 500  |          |

|                                                      | I <sub>DD1(DYN)</sub> | $V_{DD} = 5 \text{ V}, \text{ f}_{clk} = 250 \text{ kHz}$                                                                                  |                         |        | 20               |      | <u> </u> |

| Logic Current (Dynamic)                              | I <sub>DD2(DYN)</sub> | V <sub>DD</sub> = 5 V, f <sub>clk</sub> = 1                                                                                                | MHz                     |        | 70               |      | mA       |

| Logic Input                                          | •                     |                                                                                                                                            |                         |        | •                | -    |          |

| Logic Input Voltage—High<br>(VCLK, SYNC)             | V <sub>HIGH</sub>     | - V <sub>DD</sub> = 4.5 V                                                                                                                  |                         | 2.7    | 2.3              |      | v        |

| Logic Input Voltage—Low<br>(V <sub>CLK, SYNC</sub> ) | V <sub>LOW</sub>      |                                                                                                                                            |                         | -0.3   | 2.25             | 0.8  |          |

| Protection                                           |                       |                                                                                                                                            |                         |        |                  |      |          |

| Break-Before-Make Reference                          | V <sub>BBM</sub>      | V <sub>DD</sub> = 5.5 V                                                                                                                    |                         |        | 2.4              |      | v        |

| Under-Voltage Lockout                                | V <sub>UVLO</sub>     |                                                                                                                                            |                         | 3.75   | 4                | 4.25 |          |

| Under-Voltage Lockout Hysteresis                     | V <sub>H</sub>        | - V <sub>DD</sub> = 4.5 V                                                                                                                  |                         |        | 0.4              |      | 1        |

| MOSFETs                                              |                       |                                                                                                                                            |                         |        |                  | •    |          |

| Drain-Source Voltage                                 | V <sub>DS</sub>       | I <sub>D</sub> = 250 μA                                                                                                                    | I <sub>D</sub> = 250 μA |        |                  |      | V        |

|                                                      | r <sub>DS(on)1</sub>  |                                                                                                                                            | Q1                      |        | 7                | 10   |          |

| Drain-Source On-State Resistance <sup>a</sup>        | r <sub>DS(on)2</sub>  |                                                                                                                                            | Q2                      |        | 3.5              | 6    | mΩ       |

|                                                      | V <sub>SD1</sub>      | I <sub>S</sub> = 2 A, V <sub>GS</sub> = 0 V                                                                                                | Q1                      |        | 0.7              | 1.1  | v        |

| Diode Forward Voltage <sup>a</sup>                   | V <sub>SD2</sub>      |                                                                                                                                            | Q2                      |        | 0.7              | 1.1  |          |

| Dynamic <sup>b</sup>                                 |                       |                                                                                                                                            |                         |        |                  |      |          |

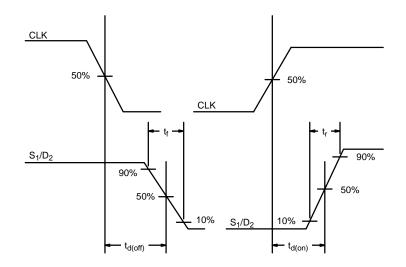

| Driver CLK to S1/D2 Off Delay                        | t <sub>d(off)</sub>   | $\label{eq:fs} \begin{array}{l} f_{s}=1 \text{ MHz}, I_{D}=10 \text{ A} \\ V_{IN}=12 \text{ V}, \text{ V}_{OUT}=1.6 \text{ V} \end{array}$ |                         |        | 43.6             | 60   |          |

| Driver CLK to S1/D2 Fall Time                        | t <sub>f</sub>        |                                                                                                                                            |                         |        | 5.8              | 10   |          |

| Driver CLK to S1/D2 On Delay                         | t <sub>d(on)</sub>    |                                                                                                                                            |                         |        | 81.5             | 150  | ns       |

| Driver CLK to S1/D2 Rise Time                        | tr                    |                                                                                                                                            |                         |        | 17.5             | 40   |          |

| Source-Drain Reverse Recovery<br>Time—Q <sub>2</sub> | t <sub>rr</sub>       | I <sub>F</sub> 2.7 A, di/dt = 100 A/μs                                                                                                     |                         |        | 50               | 80   |          |

Notes

a. Pulse test: pulse width ≤ 300 ms, duty cycle ≤ 2%.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

# Vishay Siliconix

New Product

## TIMING DIAGRAMS

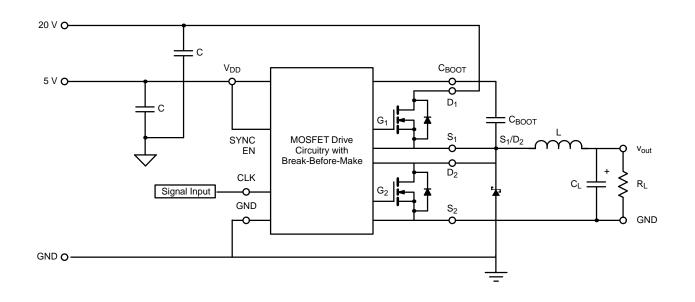

## SWITCHING TEST SET-UP

## **New Product**

# Vishay Siliconix

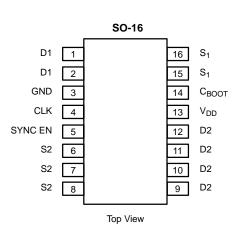

#### **PIN CONFIGURATION**

| TRUTH TABLE |     |                |                       |  |

|-------------|-----|----------------|-----------------------|--|

| Sync EN     | CLK | Q <sub>1</sub> | <b>Q</b> <sub>2</sub> |  |

| Н           | н   | ON             | OFF                   |  |

| Н           | L   | OFF            | ON                    |  |

| L           | Н   | ON             | OFF                   |  |

| L           | Ĺ   | OFF            | OFF                   |  |

| PIN DESCRIPTION |                   |                                                                      |  |  |

|-----------------|-------------------|----------------------------------------------------------------------|--|--|

| Pin             | Symbol            | Description                                                          |  |  |

| 1, 2            | D <sub>1</sub>    | High-Side MOSFET Drain                                               |  |  |

| 3               | GND               | Signal Ground                                                        |  |  |

| 4               | CLK               | Input Logic Signal                                                   |  |  |

| 5               | SYNC EN           | Synchronous Enable                                                   |  |  |

| 6, 7, 8         | S <sub>2</sub>    | Low-Side MOSFET Source                                               |  |  |

| 9, 10, 11, 12   | D <sub>2</sub>    | Low-Side MOSFET Drain                                                |  |  |

| 13              | V <sub>DD</sub>   | Logic Supply; Decoupling to GND (with a Dap is strongly recommended) |  |  |

| 14              | C <sub>BOOT</sub> | Bootstrap Capacitor for Upper MOSFET                                 |  |  |

| 15, 16          | S <sub>1</sub>    | High-Side MOSFET Source                                              |  |  |

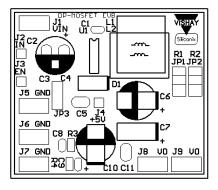

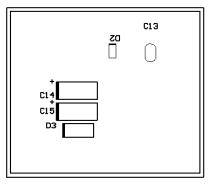

#### **APPLICATION CIRCUIT**

## **Vishay Siliconix**

## New Product

## **DEVICE OPERATION**

The Vishay Siliconix MOSFET plus driver product is optimized for dc-dc conversion in all aspects—driver design through MOSFET optimization. The integrated packaged allows the PCB designer to ignore the MOSFET driving current loops and focus on one board layout aspect—output current loop. It also allows for simplicity when adding additional phases to a system.

The MOSFET driver is designed to eliminate any shoot-through currents in the output MOSFET stage by integrating a break-before-make circuit topology. When the low-side MOSFET is to be turned on, there is an internal reference voltage,  $V_{BBM}$ , that the S<sub>1</sub> node needs to be below before the low-side MOSFET is turned on. When the high-side MOSFET is to be turned on, there is an optimized delay time (based on the MOSFET pair used) that will ensure that the low-side is turned off, and minimize the body diode conduction. In addition, the low impedance MOSFET drivers are optimized with the MOSFET gate impedance to help ensure an "off" state gate voltage during any shoot-through conditions when the high-side MOSFET is turned on.

The MOSFETs are designed to meet a specific set of conditions to provide the best performance possible. These requirements are as follows.

- 1. The size of the MOSFET is selected to provide a good compromise between power dissipation and size.

- The high-side MOSFET is designed to minimize the r<sub>DS(on)</sub>-Q<sub>g</sub> figure-of-merit and to have a low R<sub>g</sub> for short switching times.

- 3. The low-side MOSFET is designed to have the optimum  $r_{DS(on)}$ , low Rg for short switching times, and low Qgd/Qgs ratio to eliminate shoot-through conditions.

#### **Switch Timing**

The Si4738CY has a built-in delay time that is optimized for the MOSFET pair. When the CLK signal goes low, the high-side driver will turn off, and the output will start to ramp down,  $t_f$ . After a total delay,  $t_d(off)$ , the low-side driver turns on to provide the synchronous rectification.

When the CLK goes high, the low-side driver turns off; as the body diode starts to conduct, the high-side MOSFET turns on after a total delay,  $t_{d(on)}$ . The output then ramps up,  $t_r$ .

#### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

#### **Representative Safe Operating Curve**

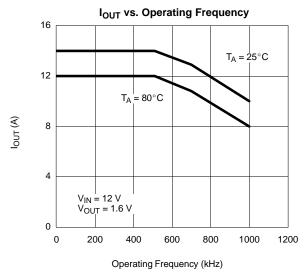

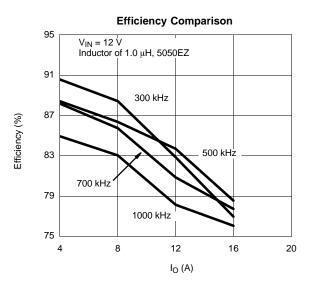

The following guidelines are meant to allow the designer the quickest and simplest method to working with the Vishay Siliconix MOSFET plus driver products.

1. The Si4738CY has a limited maximum output current capability, depending on the frequency, duty cycle and ambient temperature. The following graph shows the limitation

#### **Typical Performance**

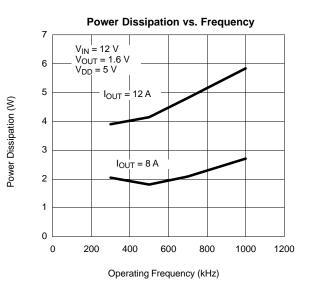

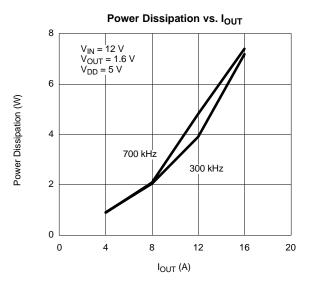

2. The following chart shows experimental results based on a specific set of operating conditions.

**New Product**

# **Vishay Siliconix**

#### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

The dissipation of the heat generated by the MOSFET plus driver product is highly dependent on the board thermal impedance and the R<sub>thJF</sub> of the SO-16 package.

#### **BOARD DESIGN GUIDELINES**

The performance characteristics shown above was done using a board that follows a suggested layout of the device and surrounding components. The basic design rules are as follows.

1. Minimize the distance of the  $V_{\text{DD}}$  capacitor to the  $V_{\text{DD}}$  pins and ground.

When all of these factors are put together, a set of efficiency curves are developed as shown. This experimental result is based on a spreading copper area on the board of one and a half square inches.

- Place the output inductor close to the S<sub>1</sub> and D<sub>2</sub> pads. Using a large copper area around these pads help improve the thermal performance. Adding thermal vias to help dissipate the heat also improves performance.

- 3. Use a large copper area for the  $D_1$  and  $S_2$  pads. Again, using thermal vias in this area will help the thermal performance.

# **Vishay Siliconix**

## **New Product**

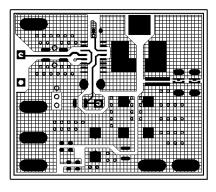

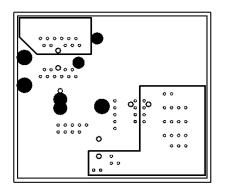

## **BOARD LAYOUT**

**Top Layer Overlay**

Top Layer

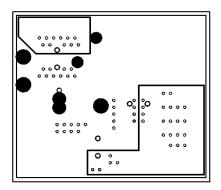

Internal Plane 1

**Bottom Layer**

Internal Plane 2

**Bottom Layer Overlay**

Vishay

# Disclaimer

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.