The DNA of tech."

SiZF640DT Symmetric Dual N-Channel 40 V MOSFET

Save Space While Simplifying PCB Layouts and Minimizing Parasitic Inductance

# 7

# **ADVANTAGE**

In space-constrained applications, the SiZ640DT reduces PCB requirements by 50 % compared to discrete devices.

# **KEY PRODUCT FEATURES**

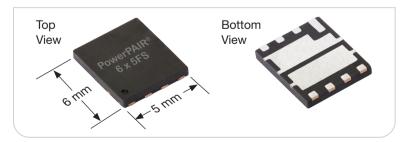

- ✓ PowerPAIR® 6 x 5FS symmetric dual integrated package

- High side and low side MOSFETs form optimized combination for 50 % duty cycles

- ✓ Pin assignment matches layout concept

- ✓ Gate return for short loop and minimized parasitic inductance

- Maximum V<sub>IN</sub> and GND pad for enhanced thermal dissipation

- √ 100 % R<sub>a</sub> and UIS tested

#### MARKETS AND APPLICATIONS

#### **INDUSTRIAL**

Half-bridge synchronous rectification in brushless DC motor drives, welding equipment, converters, robotics, power tools, and garden equipment

#### COMPUTER

Half-bridge synchronous rectification in servers, embedded applications, edge computing, portable computers, tablets, and super computers; type C chargers

#### **CONSUMER**

Half-bridge synchronous rectification in cleaning robots

#### CONNECTIVITY

Half-bridge synchronous rectification in telecom mobile infrastructure, including radio base stations and PSUs

#### RESOURCES

# SiZF640DT Symmetric Dual N-Channel 40 V MOSFET

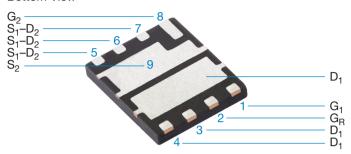

# POWERPAIR® 6 × 5FS PIN ASSIGNMENTS

Pin assignments for the PowerPAIR 6  $\times$  5FS are designed to facilitate layouts and to minimize parasitic inductance by making the equivalent loop area covered by traces as small as possible.

#### **Bottom View**

# SPECIFICATION TABLE

| Part number                           | SiZ640DT           |

|---------------------------------------|--------------------|

| Package                               | PowerPAIR® 6 × 5FS |

| Configuration                         | Symmetric Dual N   |

| V <sub>DS</sub> (V)                   | 40                 |

| V <sub>GS</sub> (V)                   | +20 / –16          |

| R <sub>DS(ON)</sub> typ. @ 10 V (mΩ)  | 1.0                |

| R <sub>DS(ON)</sub> max. @ 10 V (mΩ)  | 1.37               |

| R <sub>DS(ON)</sub> typ. @ 4.5 V (mΩ) | 1.6                |

| R <sub>DS(ON)</sub> max. @ 4.5 V (mΩ) | 2.4                |

| Q <sub>g</sub> @ 10 V (nC)            | 69                 |

| Q <sub>g</sub> @ 4.5 V (nC)           | 30                 |

| Q <sub>gs</sub> (nC)                  | 21                 |

| Q <sub>gd</sub> (nC)                  | 1.5                |

| R <sub>g</sub> typ. (Ω)               | 1.7                |

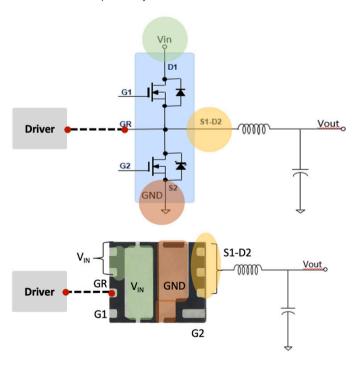

# **BUCK CONVERTER BLOCK DIAGRAM**

- Optimal V<sub>IN</sub> and GND pad

- Ultra short loop for switching

- Gate return simplifies layout

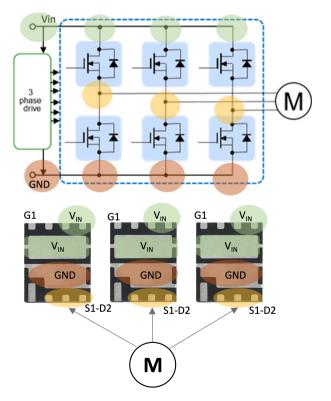

# MOTOR DRIVE BLOCK DIAGRAM

- Optimal V<sub>IN</sub> and GND pad

- Ultra short loop for switching

© 2023 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

www.vishay.com