Vishay Siliconix

### 8 A, 2.7 V to 23 V, 9.2 m $\Omega$ eFuse with Transient Over Current Blanking

#### DESCRIPTION

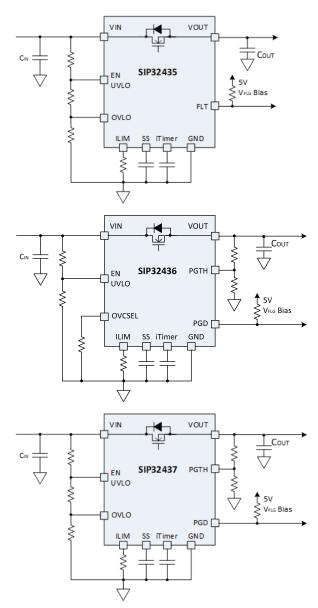

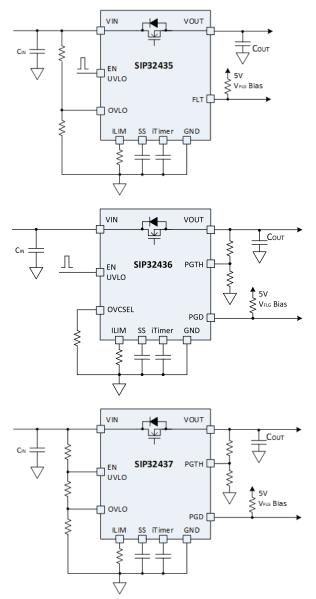

The SiP32435, SiP32436, and SiP32437 are single channel eFuses in compact 2 x 2mm package.

The family integrates multiple power management, circuit control, and protection features which provide robust defense against voltage surges, excessive inrush current, short circuit, overcurrent, and load dynamic.

The family provides increase controllability and reliability with simplified design, protect both power source and the downstream circuitry connected to the switch.

### FEATURES

- 2.7 V to 23 V operation voltage

- 9.2 mΩ typical switch resistance

- Overvoltage protection

- Overvoltage clamp with pin-selectable threshold and 5  $\mu s$  response time or

- Settable overvoltage lockout with 1 µs response time

- Programmable output turn-on slew rate

- Adjustable UVLO through EN / UVLO pin

- Adjustable OVP

- ESD / HBM: > 2 kV

- ESD / CDM: > 500 V

- Status output

- Fault indication or

- Power Good with settable threshold (PGTH)

- Compact TDFN10 2 mm x 2 mm package

- Material categorization: for definitions of compliance please see <u>www.vishay.com/doc?99912</u>

#### APPLICATIONS

- · Server, computer, and add-in cards

- Networking and data storage

- · Medical, healthcare, and patient monitoring devices

- Pad, table, and ebook

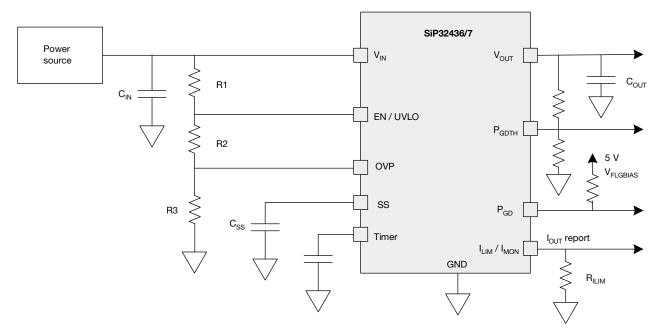

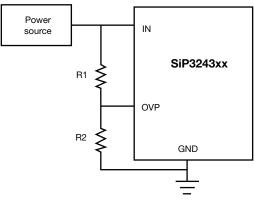

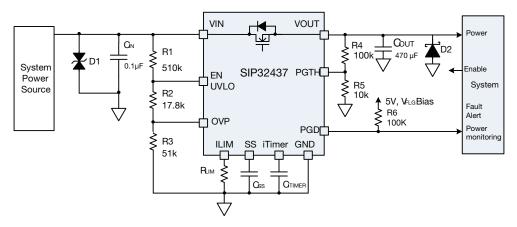

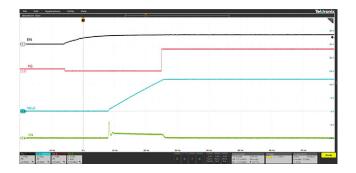

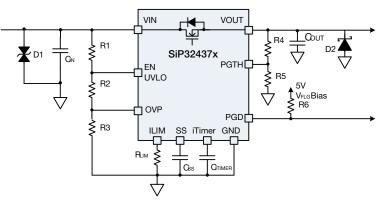

Fig. 1 - Application Circuit

1 For technical questions, contact: <u>powerictechsupport@vishay.com</u> Document Number: 61536

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

**TYPICAL APPLICATION CIRCUIT**

Vishay Siliconix

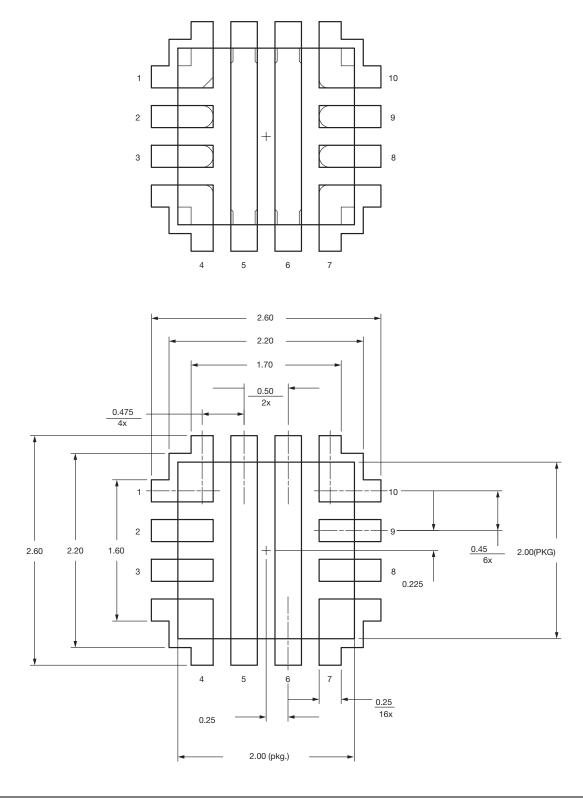

### PACKAGE OUTLINE

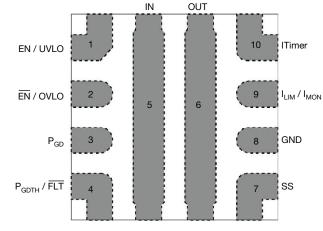

Fig. 2 - Pin Out Drawing (Top View) Pin 1 Dot Marking is on Top of the Device

| PIN DE | PIN DESCRIPTION                     |                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN #  | NAME                                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 1      | EN / UVLO                           | Active high switch control input. $V_{THL}$ < 0.3 V, $V_{THH}$ > 1.2 V/Typ                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 2      | EN / OVLO<br>(SiP32435x, SiP32437)  | Input pin for setting the overvoltage switch off threshold. A resistor divider on this pin from IN to GND can be used for the setting. Connected it to GND if OVP feature isn't required. Don't leave floating                                                                                                                                                                      |  |  |  |  |

| L      | OVCSEL (SiP32436x)                  | Input pin for selecting overvoltage clamp threshold. Please refer to " <u>SiP32436x OVCSEL PIN</u><br><u>SETTING</u> " table for details.                                                                                                                                                                                                                                           |  |  |  |  |

| 3      | PG<br>(SiP32436/7)                  | Open drain output. It is asserted high after a de-glitch time when the switch is fully on, and PGTH input voltage exceeds thresholds of related condition. It is de-asserted if PGTH voltage falls below its threshold, or a fault is detected except over current. Assertion and de-assertion have de-glitching time                                                               |  |  |  |  |

|        | DNC<br>(SiP32435)                   | Left floating                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|        | PGTH (SiP32436/7)                   | Power good threshold feedback input pin                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 4      | /FLT<br>(SiP32435)                  | An open drain output, active low fault event indicator. It is pulled low when a fault is detected                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 5      | IN                                  | Power switch input pins. Two pins are fused inside the package                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 6      | OUT                                 | Power switch output pins. Two pins are fused inside the package                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 7      | SS                                  | A capacitor from this pin to GND sets output voltage slew rate                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 8      | GND                                 | A resistor from this pin to GND sets the overload and short-circuit current limit. The pin can be used for current reporting, referring to the voltage developed over the current limit setting resistor                                                                                                                                                                            |  |  |  |  |

| 9      | I <sub>LIM</sub> / I <sub>MON</sub> | A resistor from this pin to GND sets the overload and short-circuit current limit. The pin can be used for current reporting, referring to the voltage developed over the current limit setting resistor                                                                                                                                                                            |  |  |  |  |

| 10     | ITimer                              | A capacitor from this pin to GND sets the overcurrent blanking interval during which the output current can temporarily exceed set current limit (but lower than fast-trip threshold) before the device overcurrent response takes action. Leave this pin open for the fastest response to overcurrent events. Refer to circuit-breaker or active current limiting for more details |  |  |  |  |

| ORDERING INFORMATION |                                  |                         |              |                      |           |    |

|----------------------|----------------------------------|-------------------------|--------------|----------------------|-----------|----|

| PART NUMBER          | OVP                              | OCP                     | FAULT OUTPUT | RESPONSE TO<br>FAULT | MARKING   |    |

| SiP32435ADN-T5E3 (1) | Adjustable OVP                   |                         | /FLT         | Latch-off            | AA        |    |

| SiP32435BDN-T5E3 (1) | Aujustable OVP                   | Active current          |              | Auto-retry           | AB        |    |

| SiP32436ADN-T5E3     | Selectable over voltage          | Selectable over voltage | clamping     |                      | Latch-off | AC |

| SiP32436BDN-T5E3     | clamping<br>(3.9 V, 5.8 V, 14 V) |                         | PGD          | Auto-retry           | AD        |    |

| SiP32437ADN-T5E3     | Adjustable OVP                   | Circuit breaker         | _            | Latch-off            | AE        |    |

| SiP32437BDN-T5E3     | Adjustable OVP                   | Circuit breaker         |              | Auto-retry           | AF        |    |

#### Note

<sup>(1)</sup> In development. Contact Vishay for availability

S24-1303-Rev. A, 06-Jan-2025

www.vishay.com

Vishay Siliconix

| DADAMETED                                                |                                                                                                                                  |                    | LINUT |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|--|

| PARAMETER                                                | CONDITION                                                                                                                        | LIMIT              | UNIT  |  |

| Input voltage (V <sub>IN</sub> )                         | Reference to GND                                                                                                                 | -0.3 to +26.5      | _     |  |

| Output voltage (V <sub>OUT</sub> )                       | Reference to GND (non-reverse blocking option)                                                                                   | -0.6 to (VIN +0.3) |       |  |

|                                                          | V <sub>OUT</sub> pulse, < 1 μs                                                                                                   | -0.7 V             |       |  |

| EN voltage                                               | Reference to GND                                                                                                                 | -0.3 to +6.5       |       |  |

| OVP                                                      | Reference to GND                                                                                                                 | -0.3 to +6.5       | V     |  |

| SS                                                       |                                                                                                                                  | Internally limited | -     |  |

| ITIMER                                                   |                                                                                                                                  | Internally limited |       |  |

| V <sub>PGTH</sub>                                        |                                                                                                                                  | -0.3 to +6.5       |       |  |

| PG and FLT voltage                                       |                                                                                                                                  | -0.3 to +6.5       | -     |  |

| VLIM                                                     |                                                                                                                                  | Internally limited | V     |  |

| Maximum continuous switch current                        |                                                                                                                                  | Internally limited | A     |  |

| Thermal resistance (R <sub>thJA</sub> )                  | Per JESD51-7: High Effective Thermal<br>Conductivity Board for Leaded Surface<br>Mount Packages. 4 thermal vias.<br>4 layers PCB | 19                 | °C/W  |  |

| ESD rating                                               | HBM                                                                                                                              | ± 2                | kV    |  |

| ESD rating                                               | CDM                                                                                                                              | ± 500              | , KV  |  |

| Latch up current (V <sub>IN</sub> and V <sub>OUT</sub> ) |                                                                                                                                  | 200                |       |  |

| Latch up current (control and signal puls)               | Power input and output pins                                                                                                      | 100                | - mA  |  |

| Temperature                                              |                                                                                                                                  |                    |       |  |

| Operating junction temperature                           |                                                                                                                                  | -40 to +150        |       |  |

| Storage temperature                                      |                                                                                                                                  | -65 to +150        | °C    |  |

| Maximum lead temperature                                 |                                                                                                                                  | -                  | 1     |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE                           |                  |      |      |      |  |

|-------------------------------------------------------|------------------|------|------|------|--|

| ELECTRICAL                                            | PIN              | MIN. | MAX. | UNIT |  |

| Input voltage (V <sub>IN</sub> )                      | IN               | 2.7  | 23   | V    |  |

| Output voltage (V <sub>OUT</sub> )                    | OUT              | -    | VIN  |      |  |

| Enable pin voltage (V <sub>EN</sub> )                 | EN / UVLO        | -    | 5    |      |  |

| OVP pin voltage (V <sub>OVP</sub> )                   | OVP              | 0.5  | 1.5  |      |  |

| P <sub>GTH</sub> pin voltage (V <sub>PGTH</sub> )     | P <sub>GTH</sub> | -    | 5    | v    |  |

| FLT pin voltage (V <sub>FLT</sub> )                   | FLT              | -    | 5    | v    |  |

| PG pin voltage (V <sub>PG</sub> )                     | PG               | -    | 5    |      |  |

| ITIMER capacitor voltage (VITIMER)                    | ITIMER           | 4    | -    |      |  |

| LIM pin resistance to ground (R <sub>LIM</sub> )      | I <sub>LIM</sub> | -    | -    |      |  |

| Reporting ratio, $I_{OUT} \ge 1 \text{ A} (V_{IMON})$ | I <sub>LIM</sub> | 96.5 | 114  | μΑ/Α |  |

| Continuous switch current (I <sub>MAX</sub> )         | IN to OUT        | -    | 8    | A    |  |

| Operating junction temperature (T <sub>J</sub> )      | -                | -40  | +125 | °C   |  |

| ELECTRICAL SPECIFICATIONS                            |                            |                                                                                                                                                                                                                                                                                                                                |            |              |              |      |

|------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|--------------|------|

|                                                      |                            | TEST CONDITIONS UNLESS SPECIFIED                                                                                                                                                                                                                                                                                               |            | LIMITS       |              |      |

| PARAMETER                                            | SYMBOL                     | -40 °C < $T_J$ < 125 °C, $V_{IN}$ = 12 V,<br>OUT = open, $V_{EN}$ high = 2 V,<br>$V_{OVP}$ = 0 V for SiP32435 and SiP32437,<br>$R_{ILIM}$ = 715 $\Omega$ (target set 8 A), SS = open,<br>$I_{TIMER}$ = open, FLT = open for SiP32435,<br>$P_{GTH}$ = open for SiP32436 and SiP32437,<br>$P_G$ = open for SiP32436 and SiP32437 | MIN.       | ТҮР.         | MAX.         | UNIT |

| Power Supply                                         |                            |                                                                                                                                                                                                                                                                                                                                |            |              |              |      |

| Quiescent current                                    | I <sub>Q(ON)</sub>         | EN = 1.8 V, $V_{IN}$ = 2.8 V to 23 V, $V_{OUT}$ open                                                                                                                                                                                                                                                                           | -          | 290          | 575          |      |

| Switch off current                                   | I <sub>Q(OFF)</sub>        |                                                                                                                                                                                                                                                                                                                                | -          | 55           | 135          | μA   |

| Shutdown current                                     | I <sub>SD</sub>            | EN / UVLO < V <sub>SD</sub> (F)                                                                                                                                                                                                                                                                                                | -          | 1.6          | 3            |      |

| V <sub>IN</sub> undervoltage rising threshold        | V <sub>UVP</sub> (R)       |                                                                                                                                                                                                                                                                                                                                | 2.39       | 2.6          | 2.82         |      |

| V <sub>IN</sub> undervoltage falling threshold       | V <sub>UVP</sub> (F)       |                                                                                                                                                                                                                                                                                                                                | 2.32       | 2.48         | 2.64         | V    |

| V <sub>IN</sub> undervoltage threshold hysteresis    | V <sub>UVP</sub><br>(HYST) |                                                                                                                                                                                                                                                                                                                                | -          | 120          | -            | mV   |

| Overvoltage Clamp (OVC)                              |                            |                                                                                                                                                                                                                                                                                                                                |            |              |              |      |

| • • • • • • • • • • • • • • • • • • •                | N/                         | OVCSEL = GND                                                                                                                                                                                                                                                                                                                   | 3.6        | 3.8          | 4.2          |      |

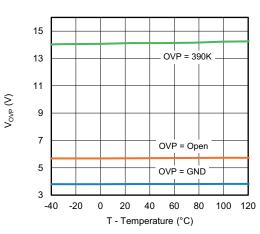

| Over voltage clamp threshold                         | V <sub>OVC</sub>           | OVCSEL = open<br>OVCSEL = 390 k to GND                                                                                                                                                                                                                                                                                         | 5.25<br>13 | 5.75<br>14.1 | 6.15<br>15.3 | -    |

|                                                      |                            | OVCSEL = 390 k to GND<br>OVCSEL = GND                                                                                                                                                                                                                                                                                          | 2.7        | 3.45         | 4.1          | V    |

| Clamped output voltage                               | V <sub>CLAMP</sub>         | OVCSEL = open                                                                                                                                                                                                                                                                                                                  | 4.8        | 5.5          | 6.2          | -    |

| · · · ·                                              |                            | OVCSEL = 390K to GND                                                                                                                                                                                                                                                                                                           | 12.3       | 13.4         | 14.6         |      |

| Output Load Current Monitor (I <sub>LIM</sub> )      |                            |                                                                                                                                                                                                                                                                                                                                |            |              |              |      |

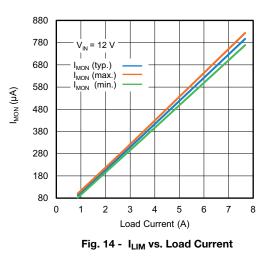

| Analog switch current reporting gain                 | GIMON                      | $I_{OUT} < I_{LIM}$ , 1 A < $I_{OUT} < 8$ A                                                                                                                                                                                                                                                                                    | 96.5       | 105.5        | 113.5        | μA/A |

|                                                      | I <sub>MON</sub> offset    | When I <sub>OUT</sub> < 1 A                                                                                                                                                                                                                                                                                                    | -18        | -            | +16          | μA   |

| Overcurrent Protection                               | I                          |                                                                                                                                                                                                                                                                                                                                |            | T            | -            |      |

|                                                      |                            | $R_{ILIM} = 6.65 \ k\Omega$                                                                                                                                                                                                                                                                                                    | 0.76       | 0.87         | 0.97         |      |

| Overcurrent threshold                                | l                          | $R_{ILIM} = 3.32 \ k\Omega$                                                                                                                                                                                                                                                                                                    | 1.55       | 1.73         | 1.9          | A    |

| Overcurrent threshold                                | ILIM                       | $R_{ILIM} = 1.65 \ k\Omega$                                                                                                                                                                                                                                                                                                    | 3.2        | 3.48         | 3.7          |      |

|                                                      |                            | R <sub>ILIM</sub> = 750 Ω                                                                                                                                                                                                                                                                                                      | 7          | 7.67         | 8.15         |      |

|                                                      | I <sub>LIM</sub>           | I <sub>LIM</sub> pin open                                                                                                                                                                                                                                                                                                      | -          | -            | 0.13         |      |

| Pin shorted to GND                                   | I <sub>LIM</sub>           | I <sub>LIM</sub> pin shorted to GND                                                                                                                                                                                                                                                                                            | 0.45       | 1.35         | 2.3          | А    |

|                                                      | I <sub>FT</sub>            | Based on characterization                                                                                                                                                                                                                                                                                                      | 24         | 27           | 33           | 1    |

| Fast trip current to ILIM ratio                      | ISCRATIO                   |                                                                                                                                                                                                                                                                                                                                | 1.7        | 2            | 2.4          |      |

| Current limit foldback threshold                     | V <sub>FB</sub>            |                                                                                                                                                                                                                                                                                                                                | -          | 50           | -            | %    |

| Switch On Resistance                                 | -10                        |                                                                                                                                                                                                                                                                                                                                |            |              |              | ,.   |

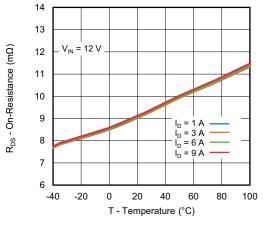

|                                                      | R <sub>ON</sub>            | I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 25 °C                                                                                                                                                                                                                                                                                 | -          | 9.2          | 14           | mΩ   |

| Enable / Undervoltage Lockout (EN / UVLO)            |                            |                                                                                                                                                                                                                                                                                                                                |            |              |              |      |

| EN / UVLO rising threshold                           | V <sub>EN</sub> (R)        |                                                                                                                                                                                                                                                                                                                                | 1.17       | 1.21         | 1.25         | v    |

| EN / UVLO falling threshold                          | V <sub>EN</sub> /F)        |                                                                                                                                                                                                                                                                                                                                | 1.05       | 1.1          | 1.15         | v    |

| EN/UVLO threshold hysteresis                         | V <sub>ENHYST</sub>        |                                                                                                                                                                                                                                                                                                                                | 60         | 100          | 140          | mV   |

| EN/UVLO leakage                                      | I <sub>EN</sub>            | T <sub>J</sub> = 25 °C                                                                                                                                                                                                                                                                                                         | -0.1       | -            | +0.1         | μA   |

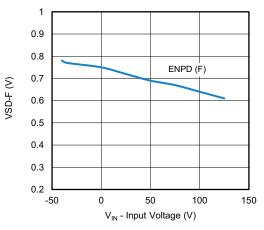

| EN / UVLO falling threshold for low shutdown current | V <sub>SD</sub> (F)        | Pull low enabled when voltage is less than VSD (F)                                                                                                                                                                                                                                                                             | 0.55       | 0.7          | 0.9          | V    |

| Overvoltage Protection (OVLO)                        |                            |                                                                                                                                                                                                                                                                                                                                |            |              |              | 1    |

| OVLO rising threshold                                | V <sub>OV</sub> (R)        |                                                                                                                                                                                                                                                                                                                                | 1.15       | 1.2          | 1.25         | v    |

| OVLO falling threshold                               | V <sub>OV</sub> (F)        |                                                                                                                                                                                                                                                                                                                                | 1.05       | 1.1          | 1.17         | v    |

| OVLO hysteresis                                      | V <sub>OV(HSYST)</sub>     |                                                                                                                                                                                                                                                                                                                                | 25         | 90           | 150          | mV   |

| OVI O pip lookage ourrept                            |                            | 0.5 V < VOVLO < 1.5 V, T <sub>J</sub> = 25 °C<br>(SiP32437x only)                                                                                                                                                                                                                                                              | -0.1       | -            | 0.1          |      |

| OVLO pin leakage current                             | V <sub>OVLKG</sub>         | 0.5 V < VOVLO < 1.5 V, T <sub>J</sub> = 25 °C<br>(SiP32436x)                                                                                                                                                                                                                                                                   | -          | 1            | 4            | μA   |

S24-1303-Rev. A, 06-Jan-2025

### Vishay Siliconix

| ELECTRICAL SPECIFICATIONS                                                               |                            |                                                                                                                                                                                                                                                                                                                                                                                            |           |           |         |      |

|-----------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|---------|------|

|                                                                                         |                            | TEST CONDITIONS UNLESS SPECIFIED                                                                                                                                                                                                                                                                                                                                                           |           | LIMITS    |         |      |

| PARAMETER                                                                               | SYMBOL                     | -40 °C < T <sub>J</sub> < 125 °C, V <sub>IN</sub> = 12 V,<br>OUT = open, V <sub>EN</sub> high = 2 V,<br>V <sub>OVP</sub> = 0 V for SiP32435 and SiP32437,<br>R <sub>ILIM</sub> = 715 $\Omega$ (target set 8 A), SS = open,<br>I <sub>TIMER</sub> = open, FLT = open for SiP32435,<br>P <sub>GTH</sub> = open for SiP32436 and SiP32437,<br>P <sub>G</sub> = open for SiP32436 and SiP32437 | MIN.      | TYP.      | MAX.    | UNIT |

| Overcurrent Fault Timer (I <sub>TIMER</sub> )                                           |                            |                                                                                                                                                                                                                                                                                                                                                                                            |           |           |         |      |

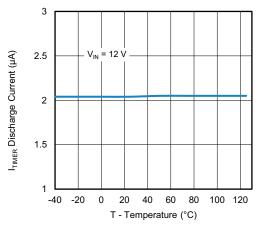

|                                                                                         | I <sub>TIMER</sub>         | I <sub>TIMER</sub> pin internal discharge current under<br>OC condition                                                                                                                                                                                                                                                                                                                    | 1.65      | 2         | 2.45    | μA   |

| 30 % charge or discharge, but 1.5 V delta volt                                          | age on this pi             | n, reference to GND or 1.2 V whatever. Below                                                                                                                                                                                                                                                                                                                                               | are parar | neter for | dischar | ge   |

| I <sub>TIMER</sub> pin internal pull-up resistance                                      | RITIMER                    |                                                                                                                                                                                                                                                                                                                                                                                            | 3         | 6         | 11      | kΩ   |

| I <sub>TIMER</sub> pin internal pull-up voltage                                         | VINT                       |                                                                                                                                                                                                                                                                                                                                                                                            | 1.58      | 1.76      | 1.94    |      |

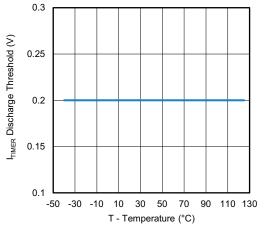

| I <sub>TIMER</sub> comparator threshold under OC condition                              | V <sub>ITIMER</sub> (F)    |                                                                                                                                                                                                                                                                                                                                                                                            | 0.13      | 0.2       | 0.27    |      |

| I <sub>TIMER</sub> charge / discharge differential voltage threshold under OC condition | $\Delta V_{\text{ITIMER}}$ |                                                                                                                                                                                                                                                                                                                                                                                            | 1.35      | 1.55      | 1.75    | V    |

| PGD, Power Good, SiP32436 and SiP32437                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                            |           |           |         |      |

| Power good indication voltage                                                           | V <sub>PGD</sub>           | When asserted, V <sub>IN</sub> > V <sub>UVP</sub> (R), PG pin<br>voltage while de-asserted                                                                                                                                                                                                                                                                                                 | -         | 1.6       | 7.6     | mV   |

| r ower good malouter verage                                                             | ♥ PGD                      | When de-asserted, $V_{IN} < V_{UVP}$ (F), device is off, EN $< V_{SD}$ (F), 250 $\mu A$ pull up current.                                                                                                                                                                                                                                                                                   | 650       | 830       | 1010    |      |

| PG pin leakage current                                                                  | I <sub>PGLKG</sub>         | PG asserted, T <sub>J</sub> = 25 °C                                                                                                                                                                                                                                                                                                                                                        | -         | -         | 1       | μA   |

| Power Good Threshold (PGTH)                                                             | 1                          |                                                                                                                                                                                                                                                                                                                                                                                            |           | 1         | 1       | r —  |

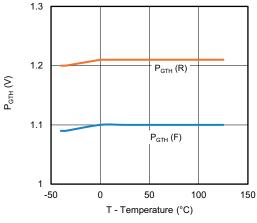

| PGTH rising threshold                                                                   | V <sub>PGTH</sub> (R)      |                                                                                                                                                                                                                                                                                                                                                                                            | 1.14      | 1.2       | 1.28    | v    |

| PGTH falling threshold                                                                  | V <sub>PGTH</sub> (F)      |                                                                                                                                                                                                                                                                                                                                                                                            | 1.03      | 1.1       | 1.16    |      |

| PGTH hysteresis                                                                         | V <sub>PGTH(HYST)</sub>    |                                                                                                                                                                                                                                                                                                                                                                                            | 70        | 115       | 150     | mV   |

| PGTH pin leakage current                                                                | IPGTHLKG                   | T <sub>J</sub> = 25 °C                                                                                                                                                                                                                                                                                                                                                                     | -0.1      | -         | 0.1     | μA   |

| Over-temperature Protection (OTP)                                                       |                            |                                                                                                                                                                                                                                                                                                                                                                                            |           | 1         |         | -    |

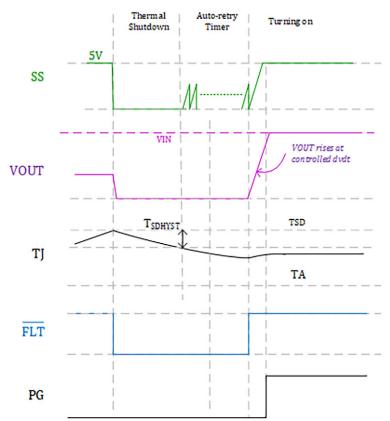

| Thermal shutdown rising threshold                                                       | T <sub>SD</sub>            | Rising T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                      | -         | 150       | -       | °C   |

| Thermal shutdown hysteresis                                                             | T <sub>SDHYS</sub>         | Falling T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                     | -         | 30        | -       |      |

| Suggested max. operation T <sub>J</sub> is 125 °C                                       |                            |                                                                                                                                                                                                                                                                                                                                                                                            |           |           |         |      |

| Soft Start Slew Rate (SS)                                                               | T .                        |                                                                                                                                                                                                                                                                                                                                                                                            |           | L         |         |      |

| SS internal charging current                                                            | I <sub>SS</sub>            |                                                                                                                                                                                                                                                                                                                                                                                            | 225       | 335       | 445     | nA   |

Vishay Siliconix

| DOD |  |  |

|-----|--|--|

|     |  |  |

| PRODUCT TIMING                          |                       |                                                                                              |      |        |      |      |

|-----------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|------|--------|------|------|

| PARAMETER                               | SYMBOL                |                                                                                              |      | LIMITS |      |      |

| PARAMETER                               | STINDUL               | TEST CONDITIONS                                                                              | MIN. | TYP.   | MAX. | UNIT |

| Power Supply                            |                       | •                                                                                            |      | •      | •    |      |

| Overvoltage lockout response time       | t <sub>OVLO</sub>     | $V_{IN} > V_{OV \circledast}$ to $V_{OUT}$ starts to fall                                    | -    | 0.6    | -    |      |

| Overvoltage clamp response time         | t <sub>ovc</sub>      | $V_{IN} > V_{OVC}$ to $V_{OUT}$ starts to fall                                               | -    | 5      | -    |      |

| Circuit breaker response time           | t <sub>CV</sub>       | From $I_{OUT}$ at 1.3 x $I_{LIM}$ to $V_{OUT}$ fall. $I_{TIMER}$ open                        | -    | 5.9    | -    | μs   |

| Current limit response time             | t <sub>LIM</sub>      | From $I_{OUT}$ at 1.3 x $I_{LIM}$ to $I_{OUT}$ settling to within 5 % of $I_{LIM}$           | -    | 0.35   | -    |      |

| Short-circuit response time             | t <sub>SC</sub>       | $I_{OUT} > 3 \text{ x } I_{LIM} \text{ to } I_{OUT} \text{ cut off}$                         | -    | 300    | -    | 20   |

| Fixed fast-trip response time           | t <sub>FT</sub>       | I <sub>OUT</sub> > IFT to I <sub>OUT</sub> cut off                                           | -    | 200    | -    | ns   |

| Thermal Shutdown to auto-retry interval | t <sub>TSD, RST</sub> | T <sub>J</sub> < T <sub>SD</sub> - T <sub>SDHYS</sub>                                        | -    | 34     | -    |      |

| PG assertion de-glitch time             | t <sub>PGA</sub>      | V <sub>PGTH</sub> > V <sub>PGTH</sub> (R) to PG rises                                        | -    | 18     | -    |      |

| PG de-assertion de-glitch time          | t <sub>PGD</sub>      | V <sub>PGTH</sub> > V <sub>PGTH</sub> (F) to PG falls                                        | -    | 18     | -    | μs   |

| V <sub>OUT</sub> slew rate              | SR                    | $R_L$ = 100 Ω, CL = 1µF, C <sub>SS</sub> = 3.3 nF,<br>V <sub>IN</sub> = 2.7 V to 23 V, 25 °C | 4.3  | 11     | 17.5 | V/ms |

|                                         |                       | EN high to 10 % V <sub>OUT</sub> , SiP32436x                                                 | 540  | 865    | 1200 |      |

| Turn on delay                           | tONDLY                | EN high to 10 % V <sub>OUT</sub> , SiP32437x                                                 | 335  | 655    | 985  | μs   |

| PGD LOGIC TABLE - SiP32436 AND SiP32437             |                                                                                                                                               |                                                                                                       |                                        |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|

| EVENT                                               | SWITCH STATUS                                                                                                                                 | SWITCH STATUS PGD OUTPUT                                                                              |                                        |  |  |

| V <sub>IN</sub> undervoltage, UVP or UVLO           | Off                                                                                                                                           | Low                                                                                                   | NA                                     |  |  |

| Overvoltage clamping, SiP32436                      | On, clamp                                                                                                                                     | High, if P <sub>GTH</sub> > V <sub>PGTH</sub> (R)<br>Low, if P <sub>GTH</sub> < V <sub>PGTH</sub> (F) | t <sub>PGA</sub><br>t <sub>PGD</sub>   |  |  |

| Overvoltage, SiP32437 only                          | Off                                                                                                                                           | Low                                                                                                   | t <sub>PGD</sub>                       |  |  |

| Switch ON                                           | On                                                                                                                                            | High, if P <sub>GTH</sub> > V <sub>PGTH</sub> (R)<br>Low, if P <sub>GTH</sub> < V <sub>PGTH</sub> (F) | t <sub>PGA</sub><br>t <sub>PGD</sub>   |  |  |

| Overcurrent during I <sub>TIMER</sub> period        | On $\begin{array}{c} \text{High, if } P_{\text{GTH}} > V_{\text{PGTH}}(R) \\ \text{Low, if } P_{\text{GTH}} < V_{\text{PGTH}}(F) \end{array}$ |                                                                                                       | t <sub>PGA</sub><br>t <sub>PGD</sub>   |  |  |

| Overcurrent, persistent, SiP32436, current clamping | On, clamp                                                                                                                                     | High, if P <sub>GTH</sub> > V <sub>PGTH</sub> (R)<br>Low, if P <sub>GTH</sub> < V <sub>PGTH</sub> (F) | t <sub>PGA</sub><br>t <sub>PGD</sub>   |  |  |

| Overcurrent, persistent, SiP32437, circuit breaker  | Off                                                                                                                                           | Low                                                                                                   | t <sub>PGA</sub><br>t <sub>PGD</sub>   |  |  |

| Output short circuit / sever overcurrent            | On, clamp                                                                                                                                     | High, if P <sub>GTH</sub> > V <sub>PGTH</sub> (R)<br>Low, if P <sub>GTH</sub> < V <sub>PGTH</sub> (F) | t <sub>PGA</sub><br>t <sub>PGD</sub>   |  |  |

| Overtemperature                                     | Off                                                                                                                                           | Low, if P <sub>GTH</sub> < 1.1 V                                                                      | t <sub>PGD</sub> + t <sub>ITIMER</sub> |  |  |

| I <sub>LIM</sub> pin open                           | Off                                                                                                                                           | Low                                                                                                   | t <sub>PGD</sub>                       |  |  |

| I <sub>LIM</sub> pin short to GND                   | Off                                                                                                                                           | Low                                                                                                   | t <sub>PGD</sub>                       |  |  |

www.vishay.com

### Vishay Siliconix

| FAULT RESPONSE AND /FLT LOGIC TABLE                    |                               |                 |                                |                          |  |  |

|--------------------------------------------------------|-------------------------------|-----------------|--------------------------------|--------------------------|--|--|

| EVENT                                                  | SWITCH<br>RESPONSE            | LATCHABLE FAULT | /FLT STATUS<br>(SiP32435 ONLY) | /FLT ASSERTION<br>DELAY  |  |  |

| V <sub>IN</sub> undervoltage, UVP or UVLO              | Off                           | No              | High                           |                          |  |  |

| Overvoltage, SiP32435                                  | Off                           | No              | High                           |                          |  |  |

| Overvoltage, SiP32436                                  | Voltage clamp                 | No              | n/a                            |                          |  |  |

| Overvoltage, SiP32437                                  | Off                           | No              | n/a                            |                          |  |  |

| Overcurrent during ITIMER period                       | No                            | No              | n/a                            |                          |  |  |

| Overcurrent, persistent, SiP32436, current<br>clamping | Current clamping              | No              | n/a                            |                          |  |  |

| Overcurrent, persistent, SiP32437x, circuit breaker    | Off                           | Yes             | n/a                            |                          |  |  |

| Output short circuit/sever overcurrent                 | Breaker then<br>current limit | No              | High                           | After I <sub>TIMER</sub> |  |  |

| Overtemperature                                        | Off                           | Yes             | Low                            |                          |  |  |

| ILIM pin open during normal steady state               | Off                           | No              | Low                            | After I <sub>TIMER</sub> |  |  |

| I <sub>LIM</sub> pin short to GND                      | Off                           | Yes             | Low                            | After I <sub>TIMER</sub> |  |  |

Latchable faults can be reset either by VIN power cycling or by pulling EN / UVLO below VSD (F). This also resets the auto-retry timer. EN / UVLO should be below V<sub>SD</sub> (F), not UVLO threshold.

Auto Retry option devices restart automatically and alert pin is de-asserted on the expiry of the t<sub>RST</sub> (100 ms ~150 ms) timer.

Vishay Siliconix

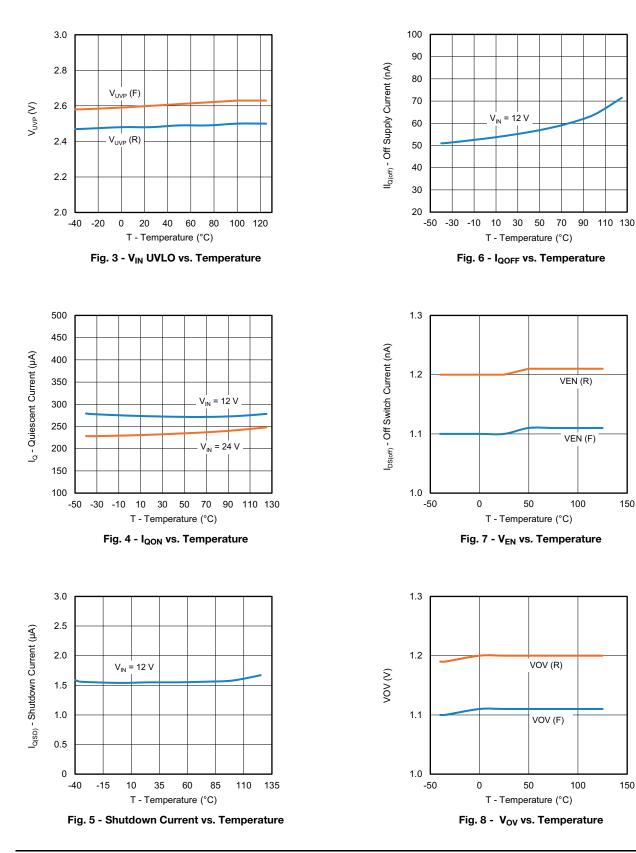

### **TYPICAL CHARACTERISTICS**

S24-1303-Rev. A, 06-Jan-2025

8

Document Number: 61536

Vishay Siliconix

### **TYPICAL CHARACTERISTICS**

Fig. 9 - P<sub>GTH</sub> Threshold vs. Temperature

Fig. 10 - R<sub>DS(on)</sub> vs. Temperature

Fig. 11 - EN Shutdown Threshold vs. Temperature

Fig. 12 - OV Threshold vs. Temperature

S24-1303-Rev. A, 06-Jan-2025

9

Document Number: 61536

Vishay Siliconix

### **TYPICAL CHARACTERISTICS**

Fig. 15 - Timer Discharge Voltage vs. Temperature

Fig. 16 - Timer Discharge Current vs. Temperature

Fig. 17 - Timer Pull Up Voltage vs. Temperature

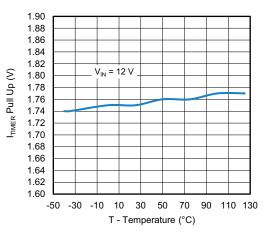

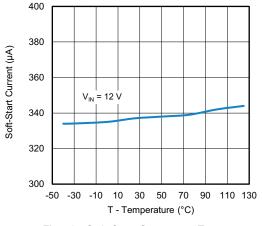

Fig. 18 - Soft-Start Current vs. Temperature

10

**Vishay Siliconix**

### **TYPICAL CHARACTERISTICS**

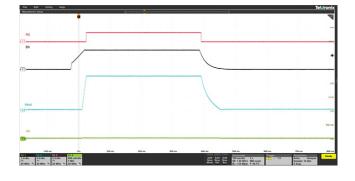

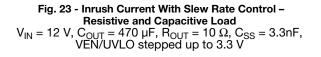

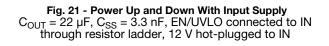

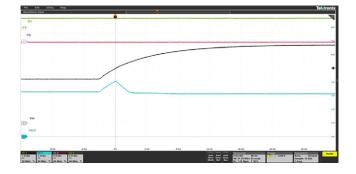

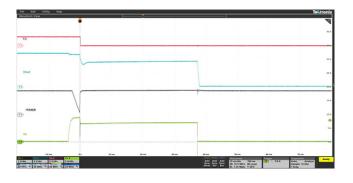

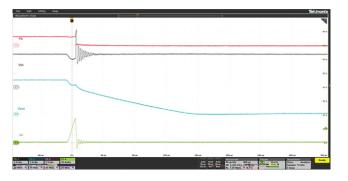

Fig. 19 - Power Up and Down With EN/UVLO Control  $V_{IN}$  = 12 V,  $C_{OUT}$  = 22  $\mu$ F,  $C_{SS}$  = 3.3 nF, VEN/UVLO ramped from 0 V  $\rightarrow$  1.4 V  $\rightarrow$  0 V

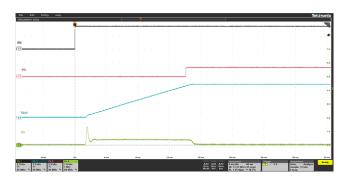

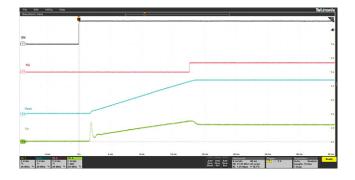

Fig. 22 - Inrush Current With Slew Rate Control – Capacitive Load  $V_{IN} = 12$  V,  $C_{OUT} = 470$  µF,  $C_{SS} = 3.3$  nF, VEN/UVLO stepped up to 3.3 V

Fig. 20 - Power Up and Down With Input Supply  $V_{IN}$  = 22 V,  $C_{OUT}$  = 22  $\mu$ F,  $C_{SS}$  = 3.3 nF, VEN/UVLO ramped from 0 V  $\rightarrow$  12 V  $\rightarrow$  0 V

Fig. 24 - Overvoltage Lockout Response – SiP32437 OV threshold set to 15.8 V,  $V_{\rm IN}$  ramped up from 12 V to 16.5 V

A Vide A Vide J Alde

11

Document Number: 61536

**Vishay Siliconix**

### **TYPICAL CHARACTERISTICS**

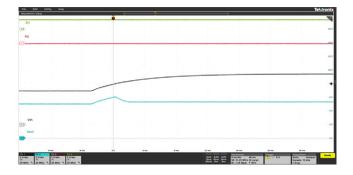

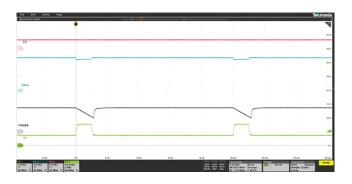

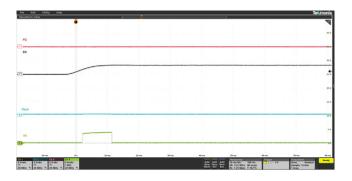

Fig. 25 - Overvoltage Clamp Response - SiP32436 ROVCSEL = GND,  $C_{OUT}$  = 220 µF,  $I_{OUT}$  = 200 mA,  $V_{IN}$  ramped up from 3.3 V to 5.8 V

Fig. 26 - Overvoltage Clamp Response - SiP32436 ROVCSEL = Open,  $C_{OUT}$  = 220 µF,  $I_{OUT}$  = 200 mA,  $V_{IN}$  ramped up from 5 V to 7.5 V

Fig. 27 - Overvoltage Clamp Response - SiP32436 ROVCSEL = 390 k $\Omega,$   $C_{OUT}$  = 220  $\mu F,$   $I_{OUT}$  = 200 mA,  $V_{IN}$  ramped up from 12 V to 16.5 V

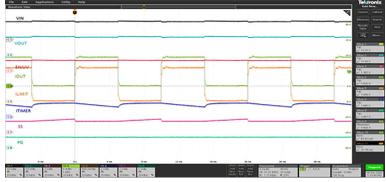

Fig. 28 - Active Current Limit Response - SiP32436  $V_{IN}$  = 12 V, CITIMER = 3.3 nF, C<sub>OUT</sub> = 220\*2 µF,  $R_{ILM}$  = 680  $\Omega$ , Resistor stepped from Open  $\Omega \rightarrow$  1.3  $\Omega$

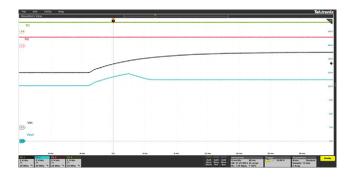

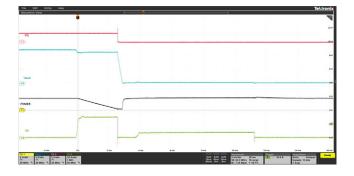

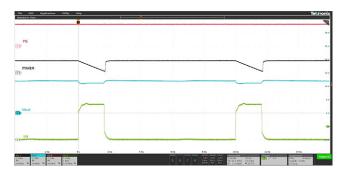

Fig. 30 - Transient Overcurrent Blanking Timer Response  $V_{IN} = 12$  V, CITIMER = 3.3 pF,  $C_{OUT} = 220^{*2}$  µF,  $R_{ILM} = 680 \Omega$ ,  $I_{OUT}$  ramped from 7 A  $\rightarrow$  15 A  $\rightarrow$  7 A within 1 ms

12

**Vishay Siliconix**

### **TYPICAL CHARACTERISTICS**

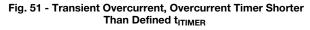

Fig. 31 - Circuit-Breaker Response SiP32437  $V_{IN}$  = 12 V, CITIMER = 3.3 nF,  $C_{OUT}$  = 220\*2  $\mu$ F,  $R_{ILM}$  = 680  $\Omega$ ,  $I_{OUT}$  stepped from 0 A  $\rightarrow$  15 A

Fig. 32 - Output Short-Circuit During Steady Stat  $V_{IN}$  = 12 V,  $R_{ILM}$  = 680  $\Omega$ , OUT stepped from Open  $\rightarrow$  Shortcircuit to GND

Fig. 33 - Output Short-Circuit During Steady State (Zoomed In)  $V_{\text{IN}} = 12 \text{ V}, \text{ R}_{\text{ILM}} = 680 \Omega,$ OUT stepped from Open  $\rightarrow$  Shortcircuit to GND

Fig. 34 - Power Up into Short-Circuit  $V_{IN} = 12 \text{ V}, C_{OUT} = \text{Open}, \text{OUT short-circuit to GND}, R_{ILM} = 680 \ \Omega, \text{VEN/UVLO stepped from 0 V to 3.3 V}$

**Vishay Siliconix**

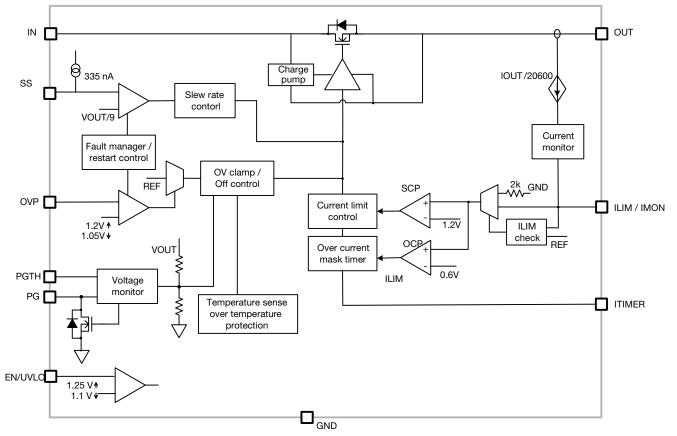

#### **OVERVIEW**

The SiP32435/6/7x is an eFuse that provides controllability and safety in power management system designs. The SiP32435/6/7x features programmable overvoltage, undervoltage, power good, and overcurrent protections, in addition to overtemperature shutdown. Its start-up output voltage slew rate can be set to control the inrush current level.

The devices operate when powered at the V<sub>IN</sub>. When the V<sub>IN</sub> clears the undervoltage lockout (UVLO) threshold, a logic high signal - higher than the VUVLO - on the EN / UVLO enables the integrated power path in a controlled slew rate.

The device monitors switch current from the start of the power path, and enables and controls the switch to ensure the user-defined overcurrent limit is not exceeded. The switch will go off swiftly to protect it from severe overcurrent conditions, such as short circuit. To cater for load circuits that require moderate transient surge current, an user-defined overcurrent blanking timer, iTimer, sets the time to allow the higher than  $I_{LIM}$  current to pass through the switch without switch-off interruption. Overvoltage on the  $V_{IN}$  is either clamped to selected thresholds (VOVC), or switched off if the overvoltage is higher than the user-defined UVLO thresholds. Such a design provides precise and prompt protection, in addition to immunity to circuit transients, for smooth circuit operation.

Fig. 35 - SiP3243x Block Diagram

**Vishay Siliconix**

### **PRODUCT FEATURES**

#### Undervoltage Protections: Undervoltage Protection (UVP) and Undervoltage Lockout (UVLO)

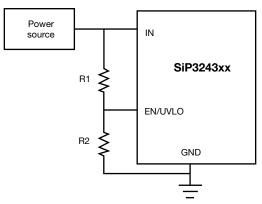

The devices have two undervoltage protections. One is a built-in fixed threshold  $V_{IN}$  UVP (VUVP), which ensures that the  $V_{IN}$  voltage is sufficient for proper device operation. The other is undervoltage lockout (UVLO). A user-defined UVLO threshold can be set by the voltage resistor divider, as shown in Fig. 36.

#### Fig. 36 - User-Defined V<sub>IN</sub> Undervoltage Lockout

The equation below shows how a resistor divider sets the UVLO threshold per a given  $V_{\text{IN}}$  level.

$$V_{\rm IN(UVP)} = \frac{V_{\rm UVLO} \times (R_1 + R_2)}{R_2}$$

#### **Overvoltage Protection**

The SiP32435/6/7x has two overvoltage protection options to protect the load from input overvoltage conditions:

- The SiP32435x and SiP32437x feature user-defined overvoltage lockout (OVLO)

- The SiP32436x features overvoltage clamping (OVC) on three user-selected voltage levels (VOVC)

#### **Overvoltage Protection (OVLO)**

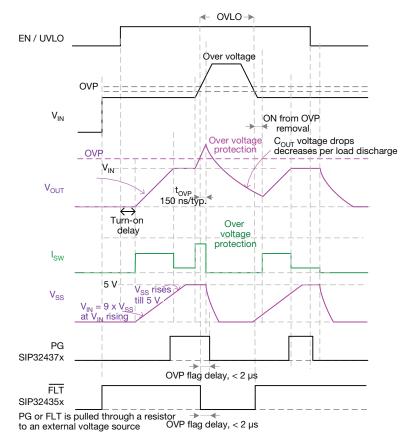

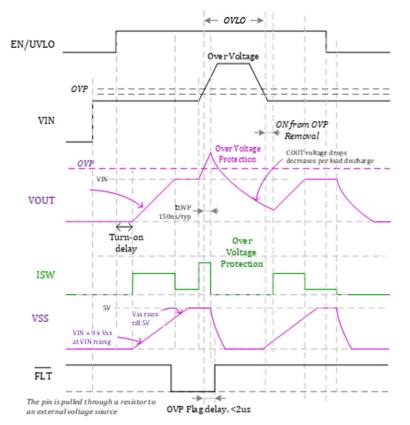

The SiP32435x and SiP32437x VIN OVLO thresholds can be set by a resistor divider, as per Fig. 37. When the voltage on OVLO crosses the OVLO rising threshold,  $V_{OV(R)}$ , the switch is off. The switch will be ON again when the voltage on OVLO falls across  $V_{OV(F)}$ . The switch on follows the slew rate. Overvoltage is not a latchable fault, meaning when the fault is removed, the switch will turn on again.

#### Fig. 37 - User-Defined Overvoltage Lockout

The equation below shows how a resistor divider sets the OVLO threshold per a given  $V_{IN}$  level.

$$\mathsf{V}_{\mathsf{IN}(\mathsf{OV})} = \frac{\mathsf{V}_{\mathsf{OV}} \times (\mathsf{R}_1 + \mathsf{R}_2)}{\mathsf{R}_2}$$

S24-1303-Rev. A, 06-Jan-2025

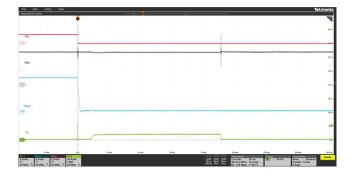

Fig. 38 - SiP32435x and SiP32437x Overvoltage Lockout and Recovery

Fig. 39 - SiP32435x Overvoltage Lockout and Recovery

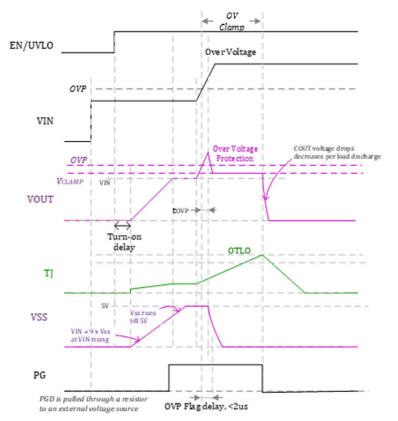

#### **Overvoltage Clamping (OVC)**

When the V<sub>IN</sub> voltage exceeds the overvoltage clamp threshold (V<sub>OVC</sub>), the SiP32436x regulates the switch and clamps the output to the voltage level of V<sub>CLAMP</sub>. There are three V<sub>CLAMP</sub> threshold levels that can be selected by the OVCSEL pin.

| SiP32436x OVCSEL PIN SETTING                     |                                |  |  |  |

|--------------------------------------------------|--------------------------------|--|--|--|

| OVCSEL PIN SETTING                               | OVERVOLTAGE CLAMPING THRESHOLD |  |  |  |

| Connected to GND                                 | 3.8 V                          |  |  |  |

| Open                                             | 5.8 V                          |  |  |  |

| Connect to GND through a 390 k $\Omega$ resistor | 14.2 V                         |  |  |  |

The device stays in the clamping state as long as the  $V_{IN}$  overvoltage persists. The device's power dissipation could be high in this state. If such a clamping condition lasts for an extended period, overtemperature protection could shut down the switch if  $T_J$  reaches the OTP threshold. For the auto-retry option, the device will restart after a delay time of 34x of  $t_{SS}$ .

Fig. 40 - SiP32436x Overvoltage Clamping and Recovery

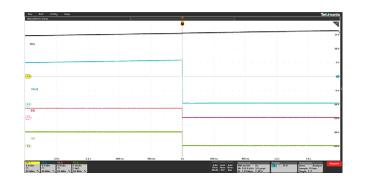

#### Turn-on Slew Rate and Inrush Current Management

A heavy capacitive load or hot-plug event can result in large inrush current or sparking at the connector contact. Such conditions should be properly managed to minimize the inrush current for a smooth switch-on transition without causing system power bus interruption or connector damage. The below equation shows how to determine the slew rate, given inrush current limit and load capacitance. Given the inrush current limit, load capacitance, and operation voltage, the proper soft start time can be determined.

Slew Rate =

$$\frac{V_{OUT}}{t_{SS}} = \frac{I_{INRUSH}}{C_{OUT}}$$

The capacitor connected between SS and GND determines the device's soft start slew rate. The output slew rate control circuit regulates the  $V_{OUT}$  to 9x of  $V_{SS}$ .

Slew Rate =

$$\frac{V_{OUT}}{t_{SS}} = \frac{I_{SS}}{C_{SS}} \times 9$$

For the fastest output slew rate, please leave the SS pin open.

During the soft start, when V<sub>OUT</sub> is below 50 % of V<sub>IN</sub>, the overcurrent limit threshold is folded back by 50 %. Together with overtemperature protection, the devices are protected from overstress conditions that could result in degraded reliability.

Www.vishay.com

### **Vishay Siliconix**

#### Circuit Breaker - SiP32437x

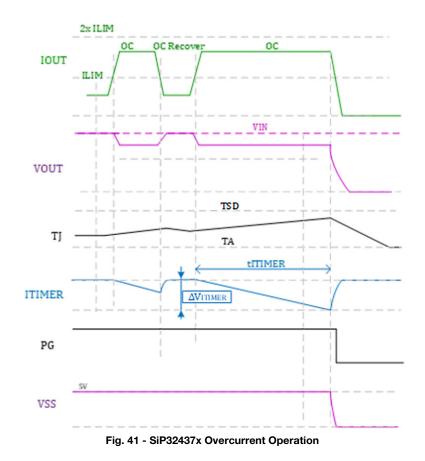

The SiP32437x will turn off the switch if the output overcurrent condition persists after the user-defined fault blanking time.

The device overcurrent threshold is set by  $R_{LIM}$  and its overcurrent fault blanking time is set by iTimer. When the load current crosses the overcurrent threshold, the iTimer circuit starts counting the time by discharging the capacitor ( $C_{ITIMER}$ ) with a constant  $I_{ITMER}$  (2 µA). If the overcurrent condition still exists when the voltage on  $C_{ITIMER}$  is discharged by  $\Delta V_{ITIMER}$ , the switch will be turned off, otherwise iTimer will reset as soon as the current falls below the  $I_{LIM}$  level. In the event the load current reaches the short circuit protection threshold (2 x  $I_{LIM}$ ), the switch will be turned off immediately.

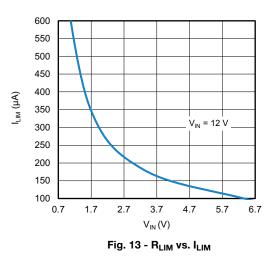

The overcurrent limit (I<sub>LIM</sub>) for a set resistor (R<sub>ILIM</sub>) can be calculated by the equation below.

$$\mathsf{R}_{\mathsf{ILIM}} = \frac{600 \, \mathsf{mV}}{\mathsf{G}_{\mathsf{IMON}} \times \mathsf{I}_{\mathsf{LIM}}}$$

$G_{IMON}$  is the switch current sense gain on the  $I_{LIM}$  /  $I_{MON}$  pin of 105.5  $\mu\text{A/A}.$

The overcurrent blanking time, which allows the load current transient, can be programmed by the capacitor (C<sub>ITIMER</sub>) connected between the iTimer pin and GND.

$$\text{iTimer} = \frac{I_{\text{ITIMER}}}{C_{\text{ITIMER}} \times \Delta V_{\text{ITIMER}}}$$

$\Delta V_{\text{ITIMER}}$  is 1.55 V

$I_{\text{ITIMER}}$  is 2  $\mu$ A

It is recommended to leave the iTimer pin open if the fastest overcurrent switch-off response is required.

The switch-off upon overcurrent will stay latched off until the V<sub>IN</sub> power reset, logic toggling, or the auto-retry feature is active.

**Vishay Siliconix**

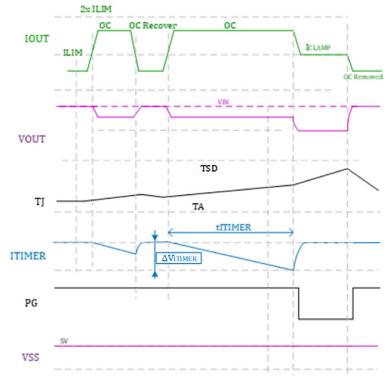

#### Current Limiting / Active Current Clamping - SiP32435x and SiP32436x

The SiP32435x and SiP32436x will actively regulate the output current if the output overcurrent condition persists after the user-defined fault blanking time.

The device overcurrent threshold is set by  $R_{LIM}$  and its overcurrent fault blanking time is set by iTimer. When the load current crosses the overcurrent threshold, the iTimer circuit starts counting the time by discharging the capacitor ( $C_{ITIMER}$ ) with a constant  $I_{ITMER}$  (2 µA). If the overcurrent condition still exists when the voltage on  $C_{ITMER}$  is discharged by  $\Delta V_{ITMER}$ , the switch will actively regulate the output current to the overcurrent threshold set by  $R_{ILIM}$ . Otherwise, iTimer will reset as soon as the current falls below the  $I_{LIM}$  level. In the event the load current reaches the short circuit protection threshold (2 x  $I_{LIMI}$ ), the switch will be turned off immediately.

The overcurrent threshold is set up by the resistor ( $R_{ILIM}$ ) on the  $I_{LIM}$  pin. The overcurrent limit ( $I_{LIM}$ ) set by the resistor ( $R_{ILIM}$ ) can be calculated by the equation below.

$$\mathsf{R}_{\mathsf{ILIM}} = \frac{600 \text{ mV}}{\mathsf{G}_{\mathsf{IMON}} \times \mathsf{I}_{\mathsf{LIM}}}$$

$G_{IMON}$  is the switch current sense gain on the  $I_{LIM}$  /  $I_{MON}$  pin of 105.5  $\mu\text{A/A}.$

The overcurrent blanking time, which allows the load current transient, can be programmed by the capacitor (C<sub>ITIMER</sub>) connected between the iTimer pin and GND.

$$\text{iTimer} = \frac{I_{\text{ITIMER}}}{C_{\text{ITIMER}} \times \Delta V_{\text{ITIMER}}}$$

When the  $I_{LIM}$  pin is open, the current limit is set to a low current level below 0.13 A. The part will begin overcurrent clamping with the very light load. In case the  $I_{LIM}$  is short is GND, the overcurrent clamping is set to 1.35 A typically.

The overcurrent protection circuit implements a foldback scheme when the  $V_{OUT}$  is below 50 % of  $V_{IN}$ .

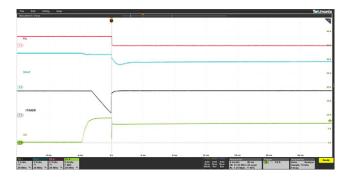

Fig. 42 - SiP32435x and SiP32436x Active Overcurrent Clamping Operation

S24-1303-Rev. A, 06-Jan-2025

**Vishay Siliconix**

When the iTimer pin is open, the devices will respond to overcurrent with a minimum possible delay.

During start-up, the devices will respond to overcurrent events without any delay (blanking time). They will actively regulate the output current to the set I<sub>LIM</sub> level. There is no circuit breaker mode during start-up. iTimer is active only after the start-up is completed.

If overcurrent happens during output voltage clamping for the SiP32436x, overcurrent clamping will be engaged immediately without the blanking timer.

Overcurrent clamping could result in overheating due to increased power dissipation across the switch. Thermal protection will kick in once the junction temperature reaches the thermal shutdown threshold (TSD).

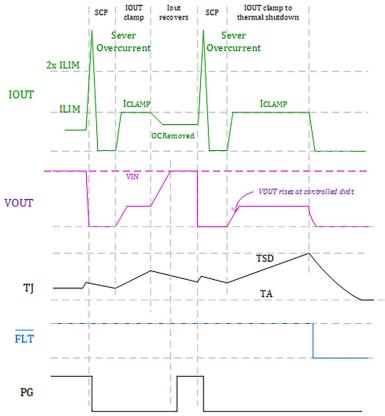

#### Severe Overcurrent and Short Circuit Protection

The severe overcurrent threshold is 2x I<sub>LIM</sub>. There is also an internal fixed short circuit protection threshold of 27 A. The severe overcurrent will turn off the switch.

Fig. 43 - SiP32435x and SiP32436x Active Overcurrent Clamping Operation

#### Analog Current Reporting Through ILIM

The  $I_{LIM}$  pin can serve both overcurrent limit setting and current reporting functions. The application circuit can acquire switch current through reading the voltage on the  $I_{LIM}$  pin, since its voltage developed over  $R_{LIM}$  is proportional to its switch current. 600 mV on the  $I_{LIM}$  pin represents the current of the overcurrent threshold level.

$$I_{OUT} = \frac{V_{ILIM}}{R_{ILIM} \times G_{IMON}}$$

Fig. 44 - I<sub>MON</sub> Current Monitor Response

The circuit load current is the switch current plus the output capacitance current.

#### **Overtemperature Protection**

The overtemperature protection circuit is active all the time, monitors the junction temperatures, and shuts the switch off under any condition as soon as it reaches thermal shutdown threshold (TSD), protecting the device from damage or performance and reliability degradation. When the junction temperature cools down by the thermal shutdown hysteresis (TSDHYS), the device can be turned on.

| DEVICE                       | OVERTEMPERATUR PROTECTION RESET                                                                                                                                                   |