Vishay Siliconix

# 18 V, 60 A, 0.6 m $\Omega$ R<sub>DS(on)</sub> Hot-Swap eFuse Switch

#### DESCRIPTION

The SiC32309 is a programmable hot swap e-fuse for high current applications such as servers, data storage, and communication products. It contains a high-side MOSFET and other control circuitry that enables it to work as stand-alone device, or to be controlled by a hot-swap controller. The SiC32309 drives up to 60 A of continuous current per device.

The SiC32309 limits the inrush current to the load when a circuit card is inserted into a live backplane power source, thereby limiting the backplane's voltage drop.

The device offers many features to simplify system designs. It provides an integrated solution for monitoring output current and die temperature, eliminating the need for an external current sensing shunt resistor, power MOSFET, and thermal sensing device.

The SiC32309 detects the power FET gate, source, and drain short conditions, in addition to feedback to the controller. SiC32309 can be operated in parallel for higher current applications. The SiC32309 is available in a PowerPAK MLP32-55.

### FEATURES

- 4.5 V to 18 V operating input range

- 25 V guaranteed maximum input tolerance

- Maximum 60 A output current

- Integrated switch with lower  $R_{DS(on)}$  of 0.6 m $\Omega$

- Built-in MOSFET driver

- · Integrated current sensing with sense output

- Separate current sensing output used to program over-current value

- · Built-in soft start and insertion delay

- Output short-circuit protection

- Over-temperature protection

- Built-in fuse health diagnostics

- · Fault status report

- · Parallel operation for higher current applications

- Analog temperature report

- Available in a PowerPAK MLP32-55 package

#### APPLICATIONS

- Hot swap

- PC cards

- Disk drives

- Servers

- Networking

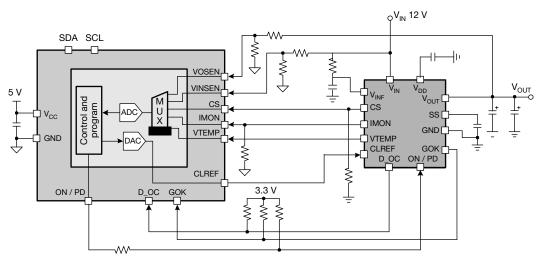

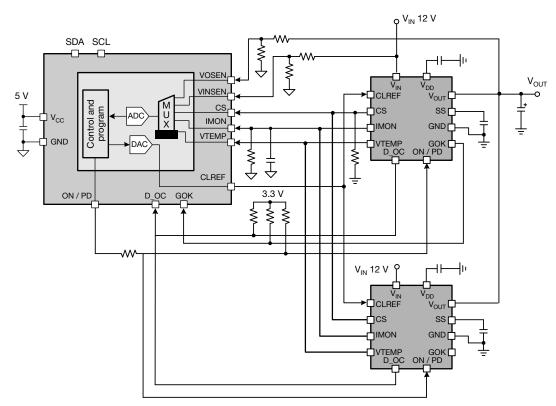

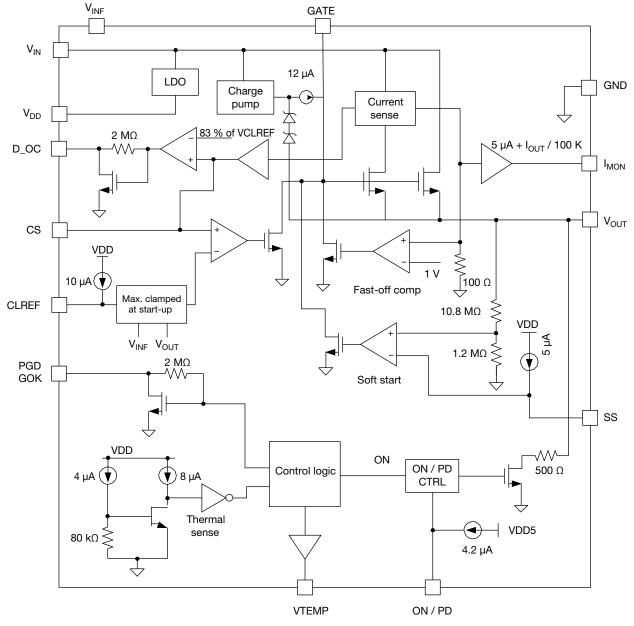

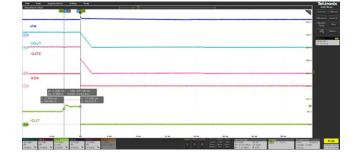

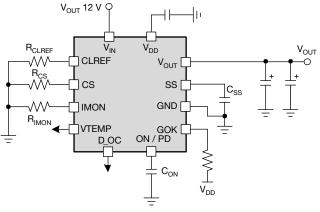

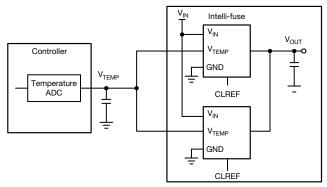

#### Fig. 1 - Typical Application Circuit

1

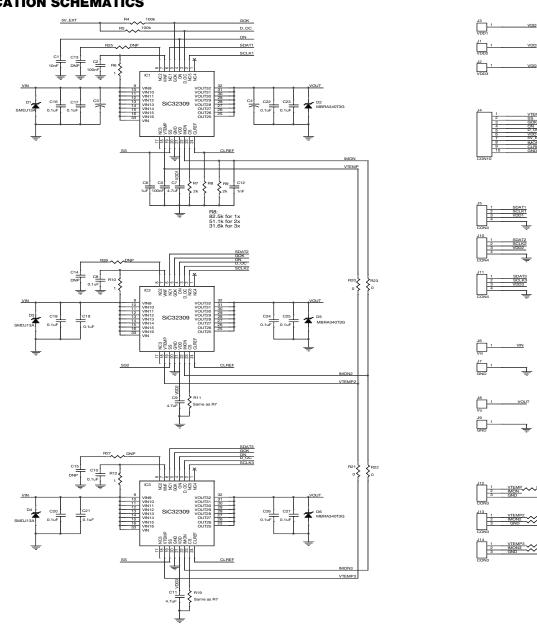

### **TYPICAL APPLICATION CIRCUIT**

Vishay Siliconix

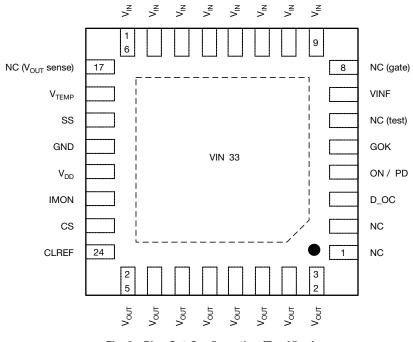

### **PINOUT CONFIGURATION**

Fig. 3 - Pins Out Configuration (Top View)

VISHAY

www.vishay.com

# SiC32309

Vishay Siliconix

| ORDERING INFORMATION |                   |                                        |            |              |  |  |  |

|----------------------|-------------------|----------------------------------------|------------|--------------|--|--|--|

| PART NUMBER          | PACKAGE           | FAULT RESPONSE                         | ALERT PINS | MARKING CODE |  |  |  |

| SiC32309CD-T5E3      | PowerPAK MLP32-55 | Switch off, and latch upon fault event | GOK, D_OC  | SiC32309     |  |  |  |

| SiC32309EVB          | Reference board   |                                        |            |              |  |  |  |

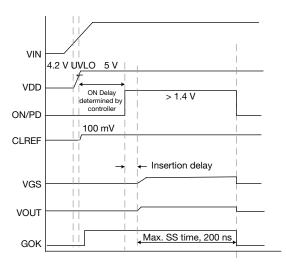

| 19SSsource charges an external capacitor in linear fashion. The V <sub>OUT</sub> voltage soft-starts at a<br>rate that tracks the soft-start capacitor. If soft-start has not completed within 200ms, a<br>fault is declared. In the event that the soft-start ramp is too fast and causes in-rush<br>current to charge V <sub>OUT</sub> with too much current, the CLREF reference will override (slow<br>down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the<br>V <sub>OUT</sub> voltage during ramping20GNDSignal ground21V <sub>DD</sub> Internal 5 V LDO output. Place a 1 μF decoupling capacitor close to V <sub>DD</sub> and GND22I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through<br>the power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 μA/A with 5 μA off set23CSCurrent sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with<br>CLREF to determine the current limit24CLREFCLREF25 to 32V <sub>OUT</sub> VoUT25 to 32V <sub>OUT</sub> Output voltage controlled by the IC. OUT is connected to the source of the integrated<br>MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PIN DESCRIP | TION              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3     D_OC     Digital output of over-current indication. D_OC is an open-drain output. When the voltage on CS is higher than 8% v VCLREP. D_OC logic is pulled low. This pin has an internal 2 MG pull-down resistor to artificially pull low in case the external pull-up resistor is missing       4     ON / PD     Power FET on / off control or OUT voltage pull-down mode control. Drv N/ PD higher than 1.4 V to turn on the power FET after starting ON / PD equal to 11.4 V Or 2 ms will cause the controller to recognize a V <sub>QUT</sub> discharge request. The power FET will begin to discharge with a 500 Ω internal resistor. Drive ON / PD to Below 0.8 V to open the power FET.       5     GOK     If a fault is detected, GOK will pull low, and the switch is turn off. If the fault is caused by an OVER-CURRENT event, OVER-TEMPERATURE event or OVER-POWER event, then the GOK will latch.       5     GOK     If a fault is detected, GOK will pull cause a GOK latch immediately if the current is greater than 100 A or if the CS voltage is greater than the CLRE voltage for 250 µs.       6     NC (TEST)     Do not connect to this pin, is an internal 2 MG pull-down resistor to artificially pull the algoal low in case the external pull-up resistor is missing       9 to 16     V <sub>N</sub> This ip is an optional liftered V <sub>N</sub> pin. Connect an appropriate RC filter to filter noise on V <sub>N</sub> 113     V(CUT Serse)     Voury or cave endoard     Voury or cave endoard       124     Vour     The SES pin is the ramping control or soft-start ramping ret. An internal fixed corent M <sub>N</sub>                                                                                                                                                                                                                                                                                                                                                 | PIN         | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3     D_OC     voltage on CS is higher than 83 % x VCLREF, D_OC logic pulled low. This pin has an internal 2 Mu pull-down resistor to artificially pullow in case the external pull-up resistor is missing       4     ON / PD     Power FET on / off control or OUT voltage pull-down mode control. Drive ON / PD higher than 1.4 V to turn on the power FET after setting ON / PD equals 10.1 V for 2 ms will lease the controller to recognize a V <sub>QUT</sub> discharge request. The power FET will begin to discharge with a 500 QL internal resistor.       5     Drive ON / PD     Fault is detected, GOK will pull low, and the switch is turn off. If the fault is caused by an OVER-CURRENT event, OVER-TEMPERATURE event or OVER-POWER event, then the GOK will latch.       5     GOK     If a fault is detected, GOK will pull low, and the switch is trond fault when power response to a soft-start timer expires are DRAIN-SHORT seent. OVER-TEMPERATURE event or OVER-POWER event, then the GOK will latch.       5     GOK     The OVER-CURRENT event will cause a GOK latch immediately if the current is greater than 100 A or if the CS VOICS short detection but does not latch GOK unless 200 ms timer expires. This pin has an internal 2 MC pull-down resistor to artificially pull the signal low in a optional filtered V <sub>M</sub> pin. Connect an appropriate RC filter to filter noise on V <sub>N</sub> will be a pull power supply. The SiS 2300 Depreses from a 4.5 V to 16 V input rail.       6     NC (TEST)     Do not connect to My pin. Connect an appropriate RC filter to filter noise on V <sub>N</sub> North Sistem in pull-up resister is missing       119     Nc (Gate)     V <sub>MW</sub> This pin is a                                                                                                                                                                                                                                                        | 1,2         | NC                | May connect to GND, V <sub>OUT</sub> , or left floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4     ON / PD     than 1.4 V to turn on the power FET after setting ON / PD equal to 1.1 V for 2 ms will begin to discharge with a 500 Ω internal resistor. Drive ON / PD below 0.8 V to open the power FET. A 1 MΩ resistor connects ON / PD to GND just in case it is floating when power input is under UVL0 threshold.       5     GOK     If a fault is detected, GOK will pull low, and the switch is turn off. If the fault is caused by an OVER-CURRENT event, OVER-TEMPERATURE event or OVER-POWER event, then the GOK will latch. Other fault is caused by an OVER-CURRENT event, OVER-TEMPERATURE event or OVER-POWER event, then the GOK will latch. Other fault is caused by an OVER-CURRENT event, obtain the CLREF voltage for 250 ms soft-start time or SOFT-START FAIL. The OVER-CURRENT event will cause a GOK latch immediately if the current is greater than 100 A or 1/PD cyclic is required in the CLREF voltage for 250 ms soft-start time expires. The pin has an internal 2 Mt publ-down resistor to artificial publ units and public down cause to a got the CLREF voltage for 250 ms soft-start time expires. The pin has an unit and 2 Mt public down calls are provided to 0 ms time expires. The pin has an internal 2 Mt public down calls are provided to 0 ms time expires. The pin has an unit and 2 Mt public down calls are greater than 100 A or case the external public presistor is ontificial public to most the set of the CLREF voltage for 250 ms 200 ms to 10 ms | 3           | D_OC              | voltage on CS is higher than 83 % x VCLREF, D_OC logic is pulled low. This pin has an internal 2 M $\Omega$ pull-down resistor to artificially pull low in case the external pull-up resistor is missing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

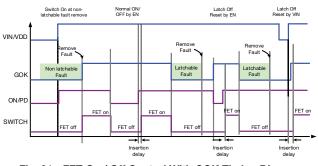

| 5 GOK If the fault is caused by an OVER-CURRENT event, OVER-TEMPERATURE event or OVER-POWRE event, then the GOK will latch.   5 GOK Other faults monitored which do not cause a latch unless the 200 ms soft-start time expires are DRAIN-SHORT short, GATE-SOURCE short, GATE-PORAIN short, and SOFT-START FALL.   5 GOK The OVER-CURRENT event will cause a GOK latch immediately if the current is greater than 100 A or if the CS voltage is greater than the CLREF voltage for 250 µs. Power or ON / PD cycling is required if the GOK latches. FET health is monitored at startup via DRAIN / GATE / SOURCE short detection but does not latch GOK unless 200 ms timer expires. This pin has an internal 2 MD pull-down resistor to artificially pull the signal low in case the external pull-up resistor is missing   6 NC (TEST) Do not connect to this pin; leave floating   7 VINF This pin is an optional filtered V <sub>IN</sub> pin. Connect an appropriate RC filter to filter noise on V <sub>N</sub> 8 NC (Gate) Leave floating or connect a 33 nF capacitor to GND i fload could oscillate at greater than 4 kHz at initia power on with single configuration circuit design   10 V <sub>INF</sub> Junction temperature sense output.   11 NC (VOUT Sense) V <sub>OUT</sub> event that tracks the soft-start apacitor to float oscillate at greater than track the soft-start capacitor in linear fabion. The V <sub>OUT</sub> voltage soft-starts at a rate that tracks the soft-start capacitor in lone of the soft-start capacitor in the soft set approximately with 200 mV + 10 mV/°C x T <sub>J</sub> .   19 SS Sin is the ramping control for soft-start amping rate. An internal fi                                                                                                                                                                                                                                                                                                       | 4           | ON / PD           | than 1.4 V to turn on the power FET after setting ON / PD equal to 1.1 V for 2 ms will cause the controller to recognize a V <sub>OUT</sub> discharge request. The power FET will begin to discharge with a 500 $\Omega$ internal resistor.<br>Drive ON / PD below 0.8 V to open the power FET.<br>A 1 M $\Omega$ resistor connects ON / PD to GND just in case it is floating when power input is                                                                                                                                                                                                                                                                                                                                                 |

| 7   V <sub>INF</sub> This pin is an optional filtered V <sub>IN</sub> pin. Connect an appropriate RC filter to filter noise on V <sub>IN</sub> 8   NC (Gate)   Leave floating or connect a 33 nF capacitor to GND if load could oscillate at greater than 4 kHz at initial power on with single configuration circuit design     9 to 16   V <sub>IN</sub> System input power supply. The SIC32309 operates from a +4.5 V to +16 V input rail.     17   NC (VOUT Sense)   V <sub>OUT</sub> sense pin. Connect to V <sub>OUT</sub> or leave floating     18   V <sub>TEMP</sub> Junction temperature sense output.     18   V <sub>TEMP</sub> The output temperature equals 200 mV + 10 mV/°C x T <sub>J</sub> 19   SS   fault is declared. In the event that the soft-start ramp is too fast and causes in-rush current to charge Sup current to charge Sup rum with too much current, the CLREF reference will override (slow down) the soft-start ramp is too fast and causes in-rush current to charge V <sub>QUT</sub> with too much current, the CLREF reference will override (slow down) the soft-start ramp is too fast and causes in-rush current to charge V <sub>QUT</sub> with too much current the CLREF reference will override (slow down) the soft-start ramp is 10 µA/A with 5 µA off set     20   GND   Signal ground     21   V <sub>DD</sub> Internal 5 V LDO output. Place a 1 µF decoupling capacitor close to V <sub>DD</sub> and GND     22   I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through the power device. The H <sub>MON</sub> /Q <sub>UT</sub> gain is 10 µA/A with 5 µA off set                                                                                                                                                                                                                                                                                                                                           | 5           | GOK               | If the fault is caused by an OVER-CURRENT event, OVER-TEMPERATURE event or OVER-POWER event, then the GOK will latch.<br>Other faults monitored which do not cause a latch unless the 200 ms soft-start timer expires are DRAIN-SHORT short, GATE-SOURCE short, GATE-DRAIN short, and SOFT-START FAIL.<br>The OVER-CURRENT event will cause a GOK latch immediately if the current is greater than 100 A or if the CS voltage is greater than the CLREF voltage for 250 µs.<br>Power or ON / PD cycling is required if the GOK latches. FET health is monitored at startup via DRAIN / GATE / SOURCE short detection but does not latch GOK unless 200 ms timer expires. This pin has an internal 2 MΩ pull-down resistor to artificially pull the |

| VINF     VIN       8     NC (Gate)     Leave floating or connect a 33 nF capacitor to GND if load could oscillate at greater than<br>4 kHz at initial power on with single configuration circuit design       9 to 16     V <sub>IN</sub> System input power supply. The SIC32309 operates from a +4.5 V to +16 V input rail.       17     NC (VOUT Sense)     V <sub>UUT</sub> sense pin. Connect to V <sub>QUT</sub> or leave floating       18     V <sub>TEMP</sub> Junction temperature equals 200 mV + 10 mV/°C x T <sub>J</sub> 19     SS     The output temperature equals 200 mV + 10 mV/°C x T <sub>J</sub> 19     SS     fault is declared. In the event that the soft-start ramping rate. An internal fixed current<br>source charges an external capacitor. If soft-start has not completed within 200ms, a<br>fault is declared. In the event that the soft-start ramp is to fast and causes in-rush<br>current to charge V <sub>QUT</sub> with too much current, the CLREF reference will override (slow<br>down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the<br>V <sub>QUT</sub> voltage during ramping       20     GND     Signal ground       21     V <sub>DD</sub> Internal 5 V LDO output. The output current is proportional to the current flowing through<br>the power device. The H <sub>QMN</sub> /Q <sub>UUT</sub> gain is 10 µA/A with 5 µA off set       23     CS     Current sense output. CS requires an external rosistor. The V <sub>CS</sub> voltage is compared with<br>CLREF to determine the current limit       24     CLREF     CLREF to determine                                                                                                                                                                                                                                                                                                                                                                                   | 6           | NC (TEST)         | Do not connect to this pin; leave floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8     NC (Gate)     4 kHz at initial power on with single configuration circuit design       9 to 16     V <sub>IN</sub> System input power supply. The SIC32309 operates from a +4.5 V to +16 V input rail.       17     NC (VOUT Sense)     V <sub>OUT</sub> sense pin. Connect to V <sub>OUT</sub> or leave floating       18     V <sub>TEMP</sub> Junction temperature sense output.<br>The output temperature equals 200 mV + 10 mV/°C x TJ       19     SS     The SS pin is the ramping control for soft-start ramping rate. An internal fixed current source charges an external capacitor. If soft-start has not completed within 200ms, a rate that tracks the soft-start capacitor. If soft-start has not completed within 200ms, a fault is declared. In the event that the soft- start ramp is too fast and causes in-rush current to charge V <sub>OUT</sub> with too much current, the CLREF reference will override (slow down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the V <sub>OUT</sub> voltage during ramping       20     GND     Signal ground       21     V <sub>DD</sub> Internal 5 V LDO output. Place a 1 μF decoupling capacitor close to V <sub>DD</sub> and GND       22     I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through the power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 μA/A with 5 μA off set       23     CS     Current sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V 150 mV when V <sub>OUT</sub> is between 40 % and 80 % o                                                                                                                                                                                                                                                                         | 7           | V <sub>INF</sub>  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

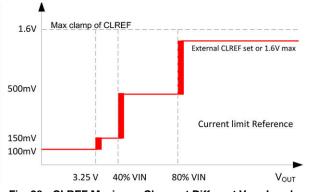

| 17   NC (VOUT Sense)   V <sub>OUT</sub> sense pin. Connect to V <sub>OUT</sub> or leave floating     18   V <sub>TEMP</sub> Junction temperature enses output.<br>The output temperature equals 200 mV + 10 mV/°C x T <sub>J</sub> 19   SS   The SS pin is the ramping control for soft-start ramping rate. An internal fixed current source charges an external capacitor in linear fashion. The V <sub>OUT</sub> voltage soft-starts at a rate that tracks the soft-start capacitor. If soft-start has not completed within 200ms, a fault is declared. In the event that the soft- start ramp is too fast and causes in-rush current to charge V <sub>OUT</sub> with too much current, the CLREF reference will override (slow down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the V <sub>OUT</sub> voltage during ramping     20   GND   Signal ground     21   V <sub>DD</sub> Internal 5 V LDO output. Place a 1 µF decoupling capacitor close to V <sub>DD</sub> and GND     22   I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through the power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 µA/A with 5 µA off set     23   CS   Current sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with CLREF to determine the current limit     24   CLREF   Current limit reference voltage input. An internal 10 µA current is sourced from this pin to an external resistor. During soft-start, this current is 60 MV when V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of VIN or higher, the CLREF voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin can be manually control                                                                                                                                                                                                                   | 8           | NC (Gate)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18     V <sub>TEMP</sub> Junction temperature sense output.<br>The output temperature equals 200 mV + 10 mV/°C x T <sub>J</sub> 19     SS     The SS pin is the ramping control for soft-start ramping rate. An internal fixed current<br>source charges an external capacitor in linear fashion. The V <sub>OUT</sub> voltage soft-starts at a<br>rate that tracks the soft-start capacitor. If soft-start has not completed within 200ms, a<br>fault is declared. In the event that the soft-start ramp is too fast and causes in-rush<br>current to charge V <sub>OUT</sub> with too much current, the CLREF reference will override (slow<br>down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the<br>V <sub>OUT</sub> voltage during ramping       20     GND     Signal ground       21     V <sub>DD</sub> Internal 5 V LDO output. Place a 1 μF decoupling capacitor close to V <sub>DD</sub> and GND       22     I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through<br>the power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 μA/A with 5 μA off set       23     CS     Current limit reference voltage input. An internal 10 μA current is sourced from this pin<br>to an external resistor. During soft-start, this current is further internally limited such that<br>the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V,<br>150 mV when V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF<br>voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin<br>can be manually controlled / driven by an external DAC that can overdrive 10 μA.       24     V <sub>OUT</sub> Output voltage controlled by the IC. OUT is con                                                                                                                           | 9 to 16     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18     VTEMP     The output temperature equals 200 mV + 10 mV/°C x TJ       19     The SS pin is the ramping control for soft-start ramping rate. An internal fixed current source charges an external capacitor. If soft-start has not completed within 200ms, a rate that tracks the soft-start capacitor. If soft-start has not completed within 200ms, a fault is declared. In the event that the soft- start ramp is too fast and causes in-rush current to charge Vo <sub>UT</sub> with too much current, the CLREF reference will override (slow down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the V <sub>OUT</sub> voltage during ramping       20     GND     Signal ground       21     V <sub>DD</sub> Internal 5 V LDO output. Place a 1 μF decoupling capacitor close to V <sub>DD</sub> and GND       22     I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through the power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 μA/A with 5 μA off set       23     CS     Current limit reference voltage in put. An internal 10 μA current is sourced from this pin to an external resistor. During soft-start, this current is sourced from this pin to an external resistor. During soft-start, this current is proportinal to the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V, 150 mV when V <sub>OUT</sub> is between 40% and 80% of VIN. When VOUT is 80% of V <sub>IN</sub> or higher, the CLREF voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin can be manually controlled / driven by an external DAC that can overdrive 10 μA.       24     Vout     Output voltage controlled by the IC. OUT is connected t                                                                                                                                                                               | 17          | NC (VOUT Sense)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19   SS   The SS pin is the ramping control for soft-start ramping rate. An internal fixed current source charges an external capacitor in linear fashion. The V <sub>OUT</sub> voltage soft-starts at a rate that tracks the soft-start capacitor. If soft-start has not completed within 200ms, a fault is declared. In the event that the soft-start ramp is too fast and causes in-rush current to charge V <sub>OUT</sub> with too much current, the CLREF reference will override (slow down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the V <sub>OUT</sub> voltage during ramping     20   GND   Signal ground     21   V <sub>DD</sub> Internal 5 V LDO output. Place a 1 μF decoupling capacitor close to V <sub>DD</sub> and GND     22   I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through the power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 μA/A with 5 μA off set     23   CS   Current sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with CLREF to determine the current limit     24   CLREF   CLREF   Current lesitor. During soft-start, this current is sourced from this pin to an external resistor. During soft voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V, 150 mV when V <sub>OUT</sub> is between 3.25 V and 40 % of V <sub>IN</sub> , 500 mV (approximately) when V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin can be manually controlled / driven by an external DAC that can overdrive 10 μA.     25 to 32   V <sub>OUT</sub> Output voltage controlled by the IC. OUT is                                                                                                                                                            | 18          | V <sub>TEMP</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21   V <sub>DD</sub> Internal 5 V LDO output. Place a 1 μF decoupling capacitor close to V <sub>DD</sub> and GND     22   I <sub>MON</sub> Current monitor output. The output current is proportional to the current flowing through the power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 μA/A with 5 μA off set     23   CS   Current sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with CLREF to determine the current limit     24   CLREF   Current limit reference voltage input. An internal 10 μA current is sourced from this pin to an external resistor. During soft-start, this current is further internally limited such that the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V, 150 mV when V <sub>OUT</sub> is between 3.25 V and 40 % of V <sub>IN</sub> , 500 mV (approximately) when V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin can be manually controlled / driven by an external DAC that can overdrive 10 μA.     25 to 32   V <sub>OUT</sub> Output voltage controlled by the IC. OUT is connected to the source of the integrated MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19          | SS                | The SS pin is the ramping control for soft-start ramping rate. An internal fixed current source charges an external capacitor in linear fashion. The $V_{OUT}$ voltage soft-starts at a rate that tracks the soft-start capacitor. If soft-start has not completed within 200ms, a fault is declared. In the event that the soft- start ramp is too fast and causes in-rush current to charge $V_{OUT}$ with too much current, the CLREF reference will override (slow down) the soft-start ramp rate. The ramping voltage on the SS pin will equal 10 % of the                                                                                                                                                                                    |

| 22IMONCurrent monitor output. The output current is proportional to the current flowing through<br>the power device. The IMON/IOUT gain is 10 μA/A with 5 μA off set23CSCurrent sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with<br>CLREF to determine the current limit24CLREFCurrent limit reference voltage input. An internal 10 μA current is sourced from this pin<br>to an external resistor. During soft-start, this current is further internally limited such that<br>the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V,<br>150 mV when V <sub>OUT</sub> is between 3.25 V and 40 % of V <sub>IN</sub> , 500 mV (approximately) when<br>V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF<br>voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin<br>can be manually controlled / driven by an external DAC that can overdrive 10 μA.25 to 32VOUTOutput voltage controlled by the IC. OUT is connected to the source of the integrated<br>MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20          | GND               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22IMONthe power device. The I <sub>MON</sub> /I <sub>OUT</sub> gain is 10 μÅ/A with 5 μA off set23CSCurrent sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with<br>CLREF to determine the current limit24CLREFCurrent limit reference voltage input. An internal 10 μA current is sourced from this pin<br>to an external resistor. During soft-start, this current is further internally limited such that<br>the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V,<br>150 mV when V <sub>OUT</sub> is between 3.25 V and 40 % of V <sub>IN</sub> , 500 mV (approximately) when<br>V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF<br>voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin<br>can be manually controlled / driven by an external DAC that can overdrive 10 μA.25 to 32V <sub>OUT</sub> Output voltage controlled by the IC. OUT is connected to the source of the integrated<br>MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21          | V <sub>DD</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23CSCurrent sense output. CS requires an external resistor. The V <sub>CS</sub> voltage is compared with<br>CLREF to determine the current limit24CLREFCurrent limit reference voltage input. An internal 10 μA current is sourced from this pin<br>to an external resistor. During soft-start, this current is further internally limited such that<br>the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V,<br>150 mV when V <sub>OUT</sub> is between 3.25 V and 40 % of V <sub>IN</sub> , 500 mV (approximately) when<br>V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF<br>voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin<br>can be manually controlled / driven by an external DAC that can overdrive 10 μA.25 to 32V <sub>OUT</sub> Output voltage controlled by the IC. OUT is connected to the source of the integrated<br>MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22          | I <sub>MON</sub>  | the power device. The $I_{MON}/I_{OUT}$ gain is 10 $\mu\text{A}/\text{A}$ with 5 $\mu\text{A}$ off set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 24CLREFto an external resistor. During soft-start, this current is further internally limited such that<br>the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V,<br>150 mV when V <sub>OUT</sub> is between 3.25 V and 40 % of V <sub>IN</sub> , 500 mV (approximately) when<br>V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF<br>voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin<br>can be manually controlled / driven by an external DAC that can overdrive 10 μA.25 to 32V <sub>OUT</sub> Output voltage controlled by the IC. OUT is connected to the source of the integrated<br>MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23          | CS                | Current sense output. CS requires an external resistor. The $V_{\text{CS}}$ voltage is compared with CLREF to determine the current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25 to 32 V <sub>OUT</sub> MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24          | CLREF             | to an external resistor. During soft-start, this current is further internally limited such that the developed external voltage is not more than 100 mV when V <sub>OUT</sub> is less than 3.25 V, 150 mV when V <sub>OUT</sub> is between 3.25 V and 40 % of V <sub>IN</sub> , 500 mV (approximately) when V <sub>OUT</sub> is between 40 % and 80 % of VIN. When VOUT is 80 % of V <sub>IN</sub> or higher, the CLREF voltage is set by external resistor. The max settable voltage on this pin is 1.6 V. This pin                                                                                                                                                                                                                               |

| 33 V <sub>IN</sub> Input of hot swap power switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25 to 32    | V <sub>OUT</sub>  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33          | V <sub>IN</sub>   | Input of hot swap power switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

E24-0450-Rev. B, 23-Sep-2024

Document Number: 62376

For technical questions, contact: <a href="mailto:powerictechsupport@vishay.com">powerictechsupport@vishay.com</a> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

#### **MARKING CODE**

#### Format:

- Line 1: part number

- · Line 2: Siliconix logo, lot code, and ESD logo

- Line 3: factory code, year code, work week code

| PARAMETER                                                           | SYMBOL                             | MIN. | MAX.                          | UNIT |

|---------------------------------------------------------------------|------------------------------------|------|-------------------------------|------|

| Input voltage                                                       | V <sub>IN</sub> , V <sub>INF</sub> | -0.3 | +25                           | V    |

| Output voltage (DC)                                                 |                                    | -0.3 | +25                           | V    |

| Output negative voltage (10 µs)                                     | V <sub>OUT</sub>                   | -3   | -                             | V    |

| Output negative voltage (500 µs)                                    |                                    | -1   | -                             | V    |

| Internal 5 V LDO output                                             | V <sub>DD</sub>                    | -0.3 | -0.3 to +6                    | V    |

| All other pins                                                      |                                    | -0.3 | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating junction temperature range                                | TJ                                 | -40  | +150                          | °C   |

| Lead temperature                                                    | T <sub>SLD</sub>                   | -    | 260                           | °C   |

| Storage temperature                                                 | T <sub>STG</sub>                   | -65  | +150                          | °C   |

| Pin 17 "V <sub>OUT</sub> Sense" voltage range                       |                                    |      | Internally limited            |      |

| Pin 8, gate voltage range (V <sub>GATE</sub> - V <sub>OUT</sub> )   |                                    | -20  | 20                            | V    |

| Maximum continuous switch current                                   |                                    | -    | 60                            | А    |

| Electronstatic discharge, human body model<br>(per EIA/JESD22-A114) | ESD <sub>HBM</sub>                 | -    | 2                             | kV   |

| Electronstatic discharge, charge device model (per EIA/JESD22-A115) | ESD <sub>CDM</sub>                 | -    | 1.5                           | kV   |

| Maximum latch-up current limit<br>(per JESD78 class II)             | I <sub>LU</sub>                    | -    | 100                           | mA   |

| Moisture sensitivity level                                          | MSL                                |      | Level 1                       |      |

| Storage                                                             | T <sub>STG</sub>                   | -55  | +125                          | °C   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

| PARAMETER                                                   | MIN. | TYP.              | MAX.  | UNIT |

|-------------------------------------------------------------|------|-------------------|-------|------|

| Input voltage (V <sub>IN</sub> )                            | 4.5  | -                 | 18    | V    |

| Maximum continuous output current                           | -    | -                 | 60    | А    |

| Maximum peak output current                                 | -    | -                 | 80    | A    |

| V <sub>DD</sub> output capacitance range                    | 2.2  | -                 | 10    | μF   |

| CLREF voltage range                                         | 0.2  | -                 | 1.6   | V    |

| Operation junction temperature                              | -40  | -                 | +125  | °C   |

| THERMAL CHARACTERISTICS                                     |      |                   |       |      |

| THERMAL PARAMETER                                           | S    | YMBOL             | VALUE | UNIT |

| Thermal resistance, junction to ambient                     |      | R <sub>0JA</sub>  | 17    | °C/W |

| Thermal resistance, junction to case, V <sub>OUT</sub> lead |      | R <sub>0JCL</sub> | 1.9   | °C/W |

| Thermal resistance, junction to case, center of exposed pad |      | R <sub>0JCB</sub> | - 1   | °C/W |

Thermal resistances are obtained by measurement with part mounted on evaluation board

Vishay Siliconix

| SPECIFICATIONS                                         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |        |       |      |

|--------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-------|------|

|                                                        |                         | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | LIMITS |       |      |

| PARAMETER                                              | SYMBOL                  | $\label{eq:VINF} \begin{array}{l} V_{\text{IN}} = V_{\text{INF}} = 12 \text{ V}, \text{ ON }/\text{ PD} = 3.3 \text{ V}, \\ \text{CVINF} = 0.1 \ \mu\text{F}, \text{CVDSS} = 4 \ \mu\text{F}, \\ \text{CVTEMP} = 0.1 \ \mu\text{F}, \text{RVTEMP} = 1 \ \text{k}\Omega, \\ \text{CSS} = 100 \ \text{nF}, \text{MIN.} \ / \text{MAX.} \ \text{LIMITS} \ \text{ARE} \\ \text{OVER THE JUNCTION TEMPERATURE} \\ \text{RANGE OF -40 }^{\circ}\text{C} \ \text{TO} \ +125 \ ^{\circ}\text{C} \ \text{UNLESS} \\ \text{SPECIFIED OTHERWISE, TYP. VALUES AT} \\ T_{\text{A}} = 25 \ ^{\circ}\text{C} \end{array}$ | MIN. | ТҮР.   | MAX.  | UNIT |

| Supplies Current                                       |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 1      | 1     |      |

|                                                        |                         | V <sub>ONPD</sub> = 3 V, no load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 3.15   | -     | mA   |

| Quiescent current                                      | lq                      | Fault latch off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | 6.5    | -     | μA   |

|                                                        |                         | V <sub>ONPD</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -    | 6.15   | -     | mA   |

| V <sub>DD</sub> Regulator and UVLO                     |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |        |       |      |

| Regulator output voltage                               | V <sub>VDD</sub>        | $I_{VDD} = 0 \text{ mA}, V_{INF} = 6 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -5%  | 5      | 5%    | V    |

| V <sub>DD</sub> current limit                          |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40   | 70     | -     | mA   |

| V <sub>DD</sub> drop out voltage                       |                         | $V_{INF} = V_{IN} = 4.5 \text{ V}, I = 20 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -    | 140    | 210   | mV   |

| V <sub>IN</sub> Under Voltage and Over Voltage Pr      | otections               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |        |       |      |

| $V_{\text{IN}}$ under voltage lockout threshold rising | V <sub>VIN_THR</sub>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | 4.2    | -     | V    |

| V <sub>IN</sub> under-voltage lockout hysteresis       | $V_{VIN_{THF}}$         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70   | 105    | -     | mV   |

| ON / PD                                                | T                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 1      | 1     |      |

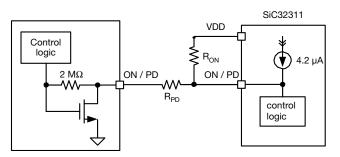

| Internal current source                                | I <sub>ON_PD</sub>      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.8  | 4.2    | 4.6   | μA   |

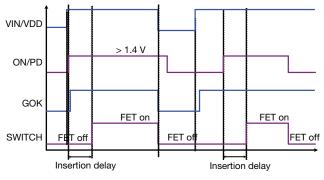

| FET on insertion delay time                            | t <sub>ON_DLY</sub>     | <b>Note:</b><br>1 ms timer begins after ON_PD pin<br>transitions above 1.4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -    | 1      | -     | ms   |

| FET on high-level input voltage                        | V <sub>ON_Hi</sub>      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.25 | 1.35   | 1.45  | V    |

| FET on-state hysteresis                                | V <sub>ON_Hyst</sub>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | 0.1    | -     | V    |

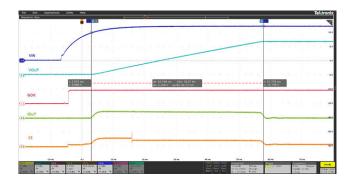

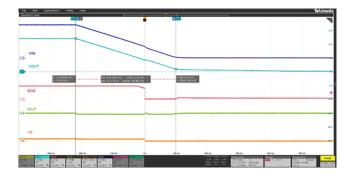

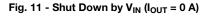

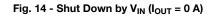

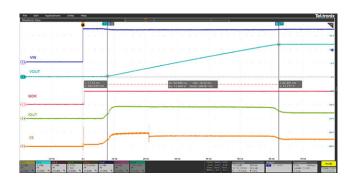

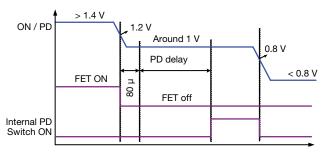

| Switch off discharge upper threshold                   | V <sub>PD_Hi</sub>      | Note:<br>ON / PD must be held continuously between<br>the value of 0.8 V and 1.2 V for 80 µs before<br>command to discharge is recognized.<br>Discharging will commence 2 ms after<br>command is recognized                                                                                                                                                                                                                                                                                                                                                                                                | -    | 1.2    | -     | v    |