## 3-Phase Brushless DC Motor Controller

#### **FEATURES**

- Hall-Effect Commutation

- 60° or 120° Sensor Spacing

- Integral High-Side Drive for all N-Channel MOSFET Bridges

- PWM Input

- Quadrature Selection

- Tachometer Output

- Reversible

- Braking

- Output Enable Control

- Cross Conduction Protection

- Current Limiting

- Undervoltage Lockout

- Internal Pull-Up Resistors

#### **DESCRIPTION**

The Si9979 is a monolithic brushless dc motor controller with integral high-side drive circuitry. The Si9979 is configured to allow either 60° or 120° commutation sensor spacing. The internal low-voltage regulator allows operation over a wide input voltage range, 20- to 40-V dc.

The Si9979 provides commutation from Hall-effect sensors. The integral high-side drive, which utilizes combination bootstrap/charge pump supplies, allows implementation of an all n-channel MOSFET 3-phase bridge. PWM, direction,

quadrature select, and braking inputs are included for control along with a tachometer output. Protection features include cross conduction protection, current limiting, and undervoltage lockout. The FAULT output indicates when undervoltage, over current, disable, or invalid sensor shutdown has occurred.

The Si9979 is available in both standard and lead (Pb)-free 48-pin SQFP packages and is specified to operate over the commercial temperature range of 0 to 70°C (C suffix), and the industrial temperature range of –40 to 85°C (D suffix).

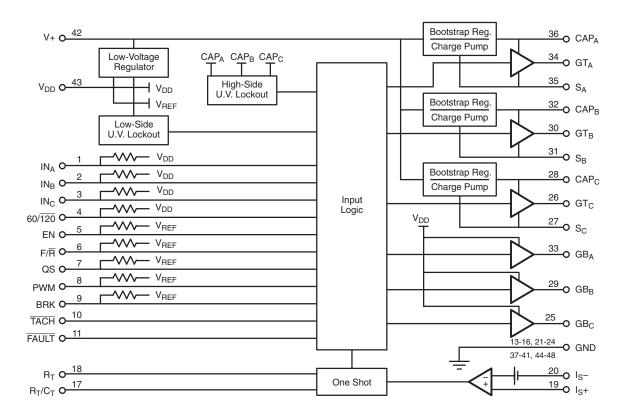

#### FUNCTIONAL BLOCK DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

| Voltage on Pin 42 50 V                 |  |

|----------------------------------------|--|

| Voltage on Pins 1–4, 10, 11            |  |

| Voltage on Pins 5–9                    |  |

| Voltage on Pins 26, 28, 30, 32, 34, 36 |  |

| Voltage on Pins 27, 31, 35             |  |

| Operating Temperature                  |  |

| C Suffix                               |  |

| D Suffix                               |  |

| Storage Temperature65 to               | o 150°C |

|----------------------------------------|---------|

| Junction Temperature (T <sub>J</sub> ) | . 150°C |

| Power Dissipation (P <sub>D</sub> )    |         |

| C Suffix                               | 0.70 W  |

| D Suffix                               | 0.55 W  |

## **RECOMMENDED OPERATING RANGE**

| V+             | <br> | +20 to 40 V <sub>D</sub> |

|----------------|------|--------------------------|

| R <sub>T</sub> | <br> | 10 kΩ Mi                 |

| SPECIFICATIONS                                 |                                             |                                          |                         |                  |      |                  |      |  |

|------------------------------------------------|---------------------------------------------|------------------------------------------|-------------------------|------------------|------|------------------|------|--|

|                                                |                                             | Test Condition                           | Limits                  |                  |      |                  |      |  |

| Parameter                                      | Symbol                                      | V+ = 20 to 40 V, I <sub>DD</sub>         | = 0 mA                  | Min <sup>a</sup> | Typb | Max <sup>a</sup> | Unit |  |

| Power                                          |                                             |                                          |                         | l                | L    | 1                |      |  |

| Supply Voltage Range                           | V+                                          |                                          |                         | 20               |      | 40               |      |  |

| Logic Voltage                                  | $V_{DD}$                                    | -20 mA ≤ I <sub>DD</sub> ≤ 0             | 0 mA                    | 14.5             | 16   | 17.5             | V    |  |

| Supply Current                                 | I+                                          |                                          |                         |                  | 4.5  |                  |      |  |

| Logic Current                                  | I <sub>DD</sub>                             |                                          |                         | -20              |      |                  | mA   |  |

| Internal Referenced                            | $V_{REF}$                                   |                                          |                         |                  | 4.2  |                  | V    |  |

| Commutation Inputs (IN <sub>A</sub> , I        | N <sub>B</sub> , IN <sub>C</sub> , 60/120)  |                                          |                         |                  |      |                  |      |  |

| High-State                                     | V <sub>IH</sub>                             |                                          |                         | 4.0              |      |                  |      |  |

| Low-State                                      | V <sub>IL</sub>                             |                                          |                         |                  |      | 1.0              | V    |  |

| High-State Input Current                       | I <sub>IH</sub>                             | $V_{IH} = V_{DD}$                        |                         |                  |      | 10               |      |  |

| Low-State Input Current                        | I <sub>IL</sub>                             | V <sub>IL</sub> = 0 V                    |                         |                  | -50  |                  | μΑ   |  |

| Logic Inputs (F/R, EN, QS, I                   | PWM, BRK)                                   | ·                                        |                         | ,                |      |                  |      |  |

| High-State                                     | V <sub>IH</sub>                             |                                          |                         | 2.0              |      |                  | .,   |  |

| Low-State                                      | V <sub>IL</sub>                             |                                          |                         |                  |      | 0.8              | V    |  |

| High-State Input Current                       | I <sub>IH</sub>                             | V <sub>IH</sub> = 5.5 V                  | V <sub>IH</sub> = 5.5 V |                  |      | 10               |      |  |

| Low-State Input Current                        | I <sub>IL</sub>                             | V <sub>IL</sub> = 0 V                    |                         |                  | -125 |                  | μΑ   |  |

| Outputs                                        |                                             | <u> </u>                                 |                         |                  |      |                  |      |  |

| Low-Side Gate Drive, High State                | $V_{GBH}$                                   |                                          |                         | 14               | 16   | 17.5             |      |  |

| Low-Side Gate Drive, Low State                 | $V_{GBL}$                                   |                                          |                         |                  |      | 0.1              |      |  |

| HE L OIL O L D : HE L OIL                      |                                             | T <sub>A</sub> = 0 to 70°C               | C Suffix                |                  | 16   | 18               | .,   |  |

| High-Side Gate Drive, High State               | $V_{GTH}$                                   | T <sub>A</sub> = -40 to 85°C             | D Suffix                |                  | 16   | 20               | V    |  |

| High-Side Gate Drive, Low State                | $V_{GTL}$                                   |                                          | •                       |                  |      | 0.1              |      |  |

| Capacitor Voltaged                             | V <sub>CAP</sub>                            | V+ = 40 V                                |                         | İ                | 55   |                  |      |  |

| Low-Side Switching, Rise Time                  | t <sub>rL</sub>                             |                                          |                         |                  | 70   |                  |      |  |

| Low-Side Switching, Fall Time                  | r-Side Switching, Fall Time t <sub>fL</sub> |                                          | 0 V                     |                  | 25   |                  |      |  |

| High-Side Switching, Rise Time t <sub>rH</sub> |                                             | Falltime = 10 to C <sub>L</sub> = 600 pF |                         | 100              |      |                  |      |  |

| High-Side Switching, Fall Time                 | t <sub>fH</sub>                             |                                          |                         |                  | 40   |                  | ns   |  |

| Break-Before-Make Time                         | t <sub>BLH</sub>                            |                                          |                         |                  | 100  |                  |      |  |

| DIEAK-DEIDIE-IVIAKE TITTE                      | t <sub>BHL</sub>                            |                                          |                         |                  | 300  |                  |      |  |

| TACH Output/FAULT Output                       | V <sub>OL</sub>                             | I <sub>OL</sub> = 1.0 mA                 |                         |                  | 0.15 | 0.4              | V    |  |

| TACH Output Pulsewidth                         | t <sub>T</sub>                              |                                          |                         | 300              | 600  |                  | ns   |  |

| SPECIFICATIONS                 |                                                       |                                             |                  |      |                       |      |    |  |  |  |

|--------------------------------|-------------------------------------------------------|---------------------------------------------|------------------|------|-----------------------|------|----|--|--|--|

|                                |                                                       | Test Condition Unless Otherwise             |                  |      | Limits                |      |    |  |  |  |

| Parameter                      | <b>Symbol</b> V+ = 20 to 40 V, I <sub>DD</sub> = 0 mA |                                             | Min <sup>a</sup> | Typb | Max <sup>a</sup>      | Unit |    |  |  |  |

| Protection                     |                                                       |                                             |                  |      |                       |      |    |  |  |  |

| Low-Side Undervoltage Lockout  | UVLL                                                  |                                             |                  |      | 12.2                  |      |    |  |  |  |

| Low-Side Hysteresis            | V <sub>H</sub>                                        |                                             |                  |      | 0.8                   |      | V  |  |  |  |

| High-Side Undervoltage Lockout | UVLH                                                  | S <sub>A, B, C</sub> = 0 V                  |                  |      | V <sub>DD</sub> – 3.3 |      |    |  |  |  |

| Current Limit                  |                                                       |                                             |                  |      |                       |      |    |  |  |  |

| Comparator Input Bias Current  | I <sub>IB</sub>                                       |                                             |                  | -5   |                       |      | μΑ |  |  |  |

| 0                              |                                                       | T <sub>A</sub> = 0 to 70°C                  | C Suffix         | 90   | 100                   | 110  | ., |  |  |  |

| Comparator Threshold Voltage   | $V_{TH}$                                              | T <sub>A</sub> = -40 to 85°C                | D Suffix         | 85   | 100                   | 125  | mV |  |  |  |

| Common Mode Voltage            | V <sub>CM</sub>                                       |                                             |                  | 0    |                       | 1    | V  |  |  |  |

| One Chat Dules Width           |                                                       | R <sub>T</sub> = 10 k, C <sub>T</sub> = 0.0 | 8                | 10   | 12                    | με   |    |  |  |  |

| One Shot Pulse Width           | t <sub>p</sub>                                        | $R_T = 10 \text{ k}, C_T = 0.0$             | 80               | 100  | 120                   |      |    |  |  |  |

- Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

c. The reference voltage is not available for external use.

d. V<sub>CAP</sub> = (V+) + (V<sub>DD</sub>).

| CON | COMMUTATION TRUTH TABLE |                 |     |                |                 |    |     |         |                  |     |       |          |         |         |         |       |               |

|-----|-------------------------|-----------------|-----|----------------|-----------------|----|-----|---------|------------------|-----|-------|----------|---------|---------|---------|-------|---------------|

|     |                         | Inputs Outputs  |     |                |                 |    |     |         | Conditions       |     |       |          |         |         |         |       |               |

|     | ensor<br>Spac           |                 |     | ensor<br>°Spac |                 |    |     |         |                  | To  | p Dri | ve       | Bot     | tom D   | rive    |       |               |

| INA | INB                     | IN <sub>C</sub> | INA | INB            | IN <sub>C</sub> | EN | F/R | BR<br>K | I <sub>S</sub> + | GT- | GT-   | GT-<br>c | GB<br>A | GB<br>B | GB<br>C | FAULT |               |

| 0   | 0                       | 0               | 1   | 0              | 1               | 1  | 1   | 0       | 0                | 1   | 0     | 0        | 0       | 1       | 0       | 1     |               |

| 1   | 0                       | 0               | 1   | 0              | 0               | 1  | 1   | 0       | 0                | 1   | 0     | 0        | 0       | 0       | 1       | 1     |               |

| 1   | 1                       | 0               | 1   | 1              | 0               | 1  | 1   | 0       | 0                | 0   | 1     | 0        | 0       | 0       | 1       | 1     |               |

| 1   | 1                       | 1               | 0   | 1              | 0               | 1  | 1   | 0       | 0                | 0   | 1     | 0        | 1       | 0       | 0       | 1     |               |

| 0   | 1                       | 1               | 0   | 1              | 1               | 1  | 1   | 0       | 0                | 0   | 0     | 1        | 1       | 0       | 0       | 1     |               |

| 0   | 0                       | 1               | 0   | 0              | 1               | 1  | 1   | 0       | 0                | 0   | 0     | 1        | 0       | 1       | 0       | 1     |               |

| 0   | 0                       | 0               | 1   | 0              | 1               | 1  | 0   | 0       | 0                | 0   | 1     | 0        | 1       | 0       | 0       | 1     |               |

| 1   | 0                       | 0               | 1   | 0              | 0               | 1  | 0   | 0       | 0                | 0   | 0     | 1        | 1       | 0       | 0       | 1     |               |

| 1   | 1                       | 0               | 1   | 1              | 0               | 1  | 0   | 0       | 0                | 0   | 0     | 1        | 0       | 1       | 0       | 1     |               |

| 1   | 1                       | 1               | 0   | 1              | 0               | 1  | 0   | 0       | 0                | 1   | 0     | 0        | 0       | 1       | 0       | 1     |               |

| 0   | 1                       | 1               | 0   | 1              | 1               | 1  | 0   | 0       | 0                | 1   | 0     | 0        | 0       | 0       | 1       | 1     |               |

| 0   | 0                       | 1               | 0   | 0              | 1               | 1  | 0   | 0       | 0                | 0   | 1     | 0        | 0       | 0       | 1       | 1     |               |

| Х   | Х                       | Х               | Х   | Х              | Х               | 0  | Х   | 0       | Х                | 0   | 0     | 0        | 0       | 0       | 0       | 0     | Disable       |

| Х   | Х                       | Х               | Х   | Х              | Х               | 0  | Х   | 1       | Х                | 0   | 0     | 0        | 1       | 1       | 1       | 0     | Power Down    |

| L   | L                       | L               | L   | L              | L               | 1  | Х   | 1       | 0                | 0   | 0     | 0        | 1       | 1       | 1       | 1     | Brake         |

| L   | L                       | L               | L   | L              | L               | 1  | Х   | 1       | 1                | 0   | 0     | 0        | 1       | 1       | 1       | 0     | Over I in BRK |

| L   | L                       | L               | L   | L              | L               | 1  | Х   | 0       | 1                | 0   | 0     | 0        | 0       | 0       | 0       | 0     | Over I        |

| 1   | 0                       | 1               | 1   | 1              | 1               | 1  | Х   | 0       | Х                | 0   | 0     | 0        | 0       | 0       | 0       | 0     |               |

| 1   | 0                       | 1               | 1   | 1              | 1               | 1  | Х   | 1       | Х                | 0   | 0     | 0        | 1       | 1       | 1       | 0     |               |

| 0   | 1                       | 0               | 0   | 0              | 0               | 1  | Х   | 0       | Х                | 0   | 0     | 0        | 0       | 0       | 0       | 0     |               |

| 0   | 1                       | 0               | 0   | 0              | 0               | 1  | Х   | 1       | Х                | 0   | 0     | 0        | 1       | 1       | 1       | 0     |               |

Notes: L. Any valid sensor combination X. Don't care

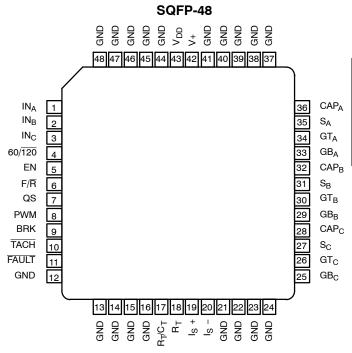

#### PIN CONFIGURATION AND ORDERING INFORMATION

Top View

| ORDERING INFORMATION                                       |                       |                |         |  |  |  |  |  |  |

|------------------------------------------------------------|-----------------------|----------------|---------|--|--|--|--|--|--|

| Standard Lead (Pb)-Free Temperature Part Number Range Pack |                       |                |         |  |  |  |  |  |  |

| Si9979CS                                                   | Si9979CS—E3           | 0 to 70°C      | SQFP-48 |  |  |  |  |  |  |

| Si9979DS Si9979DS—E3 -40 to 85°C                           |                       |                |         |  |  |  |  |  |  |

| NOTE: Si9979CS                                             | and Si9979DS are supp | lied in trays. |         |  |  |  |  |  |  |

#### **PIN DESCRIPTION**

#### Pins 1-3: INA, INB, INC

${\rm IN_A}$ ,  ${\rm IN_B}$ , and  ${\rm IN_C}$  are the commutation sensor inputs, and are intended to be driven by open collector Hall effect switches. These inputs have internal pull up resistors tied to  ${\rm V_{DD}}$ , which eliminates the need for external pull up resistors.

#### Pin 4: 60/120

The  $60/\overline{120}$  input allows the use of the Si9979 with either a  $60^\circ$  or  $120^\circ$  commutation sensor spacing. An internal pull up resistor, which is tied to  $V_{DD}$ , sets the default condition to  $60^\circ$  spacing.  $120^\circ$  spacing is selected by pulling this input to ground.

#### Pin 5: EN (Enable)

A logic "1" on this input allows commutation of the motor. This is the default condition as this pin is pulled up internally. When this pin is pulled to ground, all gate drive outputs are turned off.

#### Pin 6: F/R (Forward/Reverse)

A logic "1" on this input selects commutation for motor rotation in the "forward" direction. This is the default condition as this

pin is pulled up internally. When this pin is pulled to ground, the commutation sensor logic levels are inverted internally, causing reverse rotation.

#### Pin 7: QS (Quadrature Select)

This input determines whether the bottom MOSFETs or both bottom and top MOSFETs switch in response to the PWM signal. A logic "1" on this input enables only the bottom MOSFETs. This is the default condition as this pin is pulled up internally. When this pin is pulled to ground, both the bottom and top MOSFETs are enabled.

#### Pin 8: PWM

An open collector (drain) or TTL compatible signal is applied to this input to control the motor speed. The QS input determines which MOSFETs are switched in response to the PWM signal. If no PWM signal is being used, this input is left open. It is pulled up internally, which allows the MOSFETs to follow the commutation sequence.

# VISHAY

## **Vishay Siliconix**

#### **PIN DESCRIPTION (CONT'D)**

#### Pin 9: BRK

With this input at logic "1", the top MOSFETs are turned off and the bottom MOSFETs are turned on, shorting the motor windings together. This provides a braking torque which is dependent on the motor speed. This is the default condition as this pin is pulled up internally. When this pin is pulled to ground, the MOSFETs are allowed to follow the commutation sequence.

#### Pin 10: TACH

This output provides a minimum 300-nanosecond output pulse for every commutation sensor transition, yielding a 6 pulse per electrical revolution tachometer signal. This output is open drain.

#### Pin 11: FAULT

The FAULT output switches low to indicate that at least one of the following conditions exists, controller disable (EN), undervoltage lockout, invalid commutation sensor code shutdown, or overcurrent shutdown. This output is open drain.

#### Pin 17: R<sub>T</sub>/C<sub>T</sub>

The junction of the current limit one shot timing resistor and capacitor is connected to this pin. This one-shot is triggered by the current limit comparator when an overcurrent condition exists. This action turns off all the gate drives for the period defined by  $R_T$  and  $C_T$ , thus stopping the flow of current.

#### Pin 18: R<sub>T</sub>

One side of the current limit one shot timing resistor is connected to this pin.

#### Pin 19: Is+

This is the sensing input of the current limit comparator and should be connected to the positive side of the current sense resistor. When the voltage across the current sense resistor exceeds 100 mV, the comparator switches and triggers the current limit one-shot. The one-shot turns off all the gate drives for the period defined by  $R_T$  and  $C_T$ , thus stopping the flow of current. If the overcurrent condition remains after the shutdown period, the gate drives will be held off until the overcurrent condition no longer exists.

#### Pin 20: I<sub>S</sub>-

This pin is the ground reference for the current limit comparator. It should be connected directly to the ground side of the current sense resistor to enhance noise immunity.

#### Pins 12-16: 21-24, 37-41, 44-48, GND

These pins are the return path for both the logic and gate drive circuits. Also, they serve to conduct heat out of the package, into the circuit board.

#### Pin 25: GB<sub>C</sub>

This is the gate drive output for the bottom MOSFET in Phase  ${\rm C.}$

#### Pin 26: GT<sub>C</sub>

This is the gate drive output for the top MOSFET in Phase C.

#### Pin 27: S<sub>C</sub>

This pin is negative supply of the high-side drive circuitry. As such, it is the connection for the negative side of the bootstrap capacitor, the top MOSFET Source, the bottom MOSFET Drain, and the Phase C output.

#### Pin 28: CAP<sub>C</sub>

This pin is the positive supply of the high-side circuitry. The bootstrap capacitor for Phase C is connected between this pin and SC.

#### Pin 29: GB<sub>B</sub>

This is the gate drive output for the bottom MOSFET in Phase R

#### Pin 30: GT<sub>B</sub>

This is the gate drive output for the top MOSFET in Phase B.

#### Pin 31: S<sub>B</sub>

This pin is negative supply of the high-side drive circuitry. As such, it is the connection for the negative side of the bootstrap capacitor, the top MOSFET Source, the bottom MOSFET Drain, and the Phase B output.

#### Pin 32: CAPB

This pin is the positive supply of the high-side circuitry. The bootstrap capacitor for Phase B is connected between this pin and SB.

#### Pin 33: GB<sub>△</sub>

This is the gate drive output for the bottom MOSFET in Phase A.

#### **PIN DESCRIPTION (CONT'D)**

Pin 34: GT<sub>A</sub>

This is the gate drive output for the top MOSFET in Phase A.

Pin 35: S<sub>△</sub>

This pin is negative supply of the high-side drive circuitry. As such, it is the connection for the negative side of the bootstrap capacitor, the top MOSFET Source, the bottom MOSFET Drain, and the Phase A output.

Pin 36: CAPA

This pin is the positive supply of the high-side circuitry. The bootstrap capacitor for Phase A is connected between this pin and SA.

#### Pin 42: V+

The supply voltage for the Si9979 is connected between this pin and ground. The internal logic and high-side supply voltages are derived from V+.

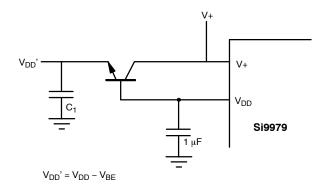

#### Pin 43: V<sub>DD</sub>

$V_{DD}$  is the internal logic and gate drive voltage. It is necessary to connect a capacitor between this pin and ground to insure that the current surges seen at the turn on of the bottom MOSFETs does not trip the undervoltage lockout circuitry.

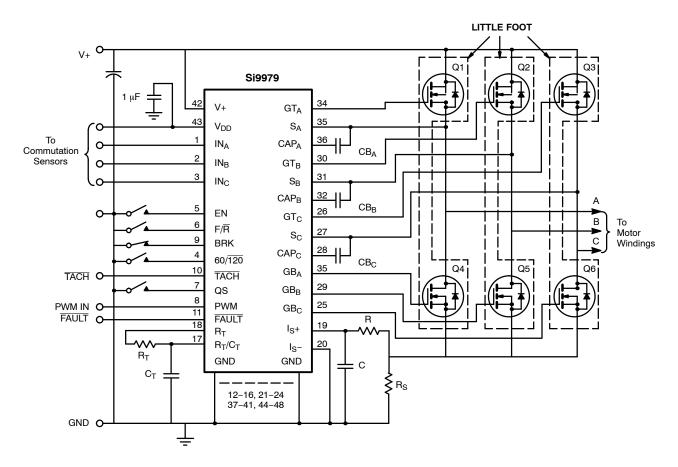

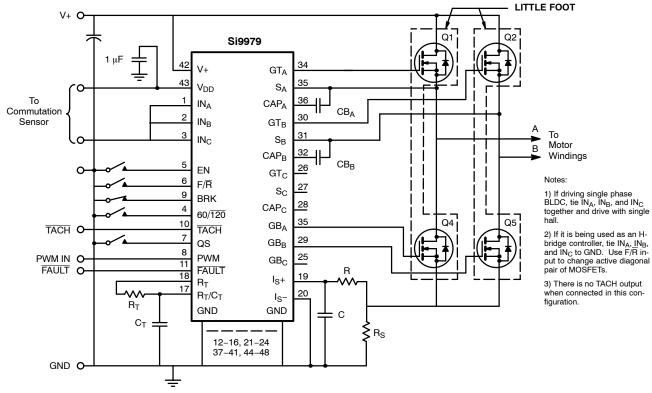

#### **APPLICATION CIRCUITS**

FIGURE 1. Three-Phase Brushless DC Motor Controller

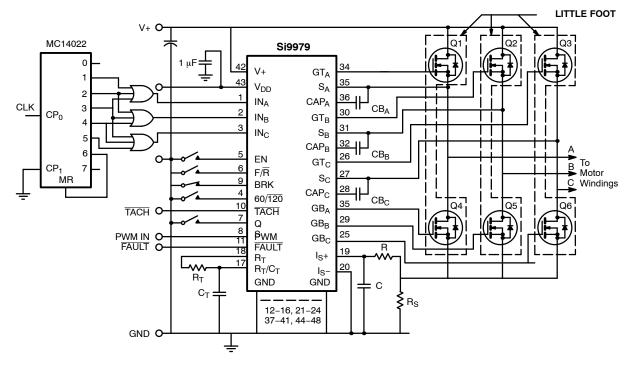

#### **APPLICATION CIRCUITS**

FIGURE 2. Single H-Bridge Controller

FIGURE 3. Three-Phase AC Motor Controller

## **APPLICATION CIRCUITS**

**FIGURE 4.** External  $V_{DD}$  Regulator

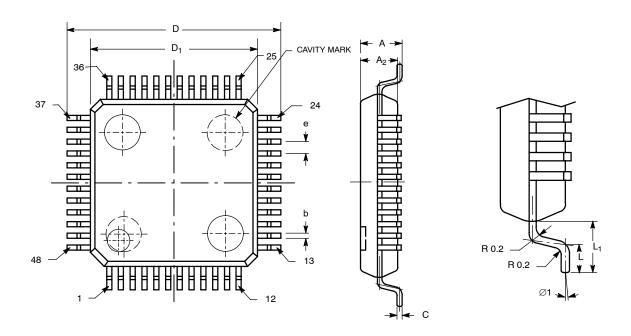

## SQFP: 48-LEAD (7X7X1.4 MM) SQUARE (POWER IC ONLY)

|                                             | MILLIM | IETERS | INCH  | HES*  |  |  |  |  |

|---------------------------------------------|--------|--------|-------|-------|--|--|--|--|

| Dim                                         | Min    | Max    | Min   | Max   |  |  |  |  |

| Α                                           | 1.40   | 1.60   | 0.055 | 0.063 |  |  |  |  |

| <b>A</b> <sub>1</sub>                       | 0.05   | 0.15   | 0.002 | 0.006 |  |  |  |  |

| A <sub>2</sub>                              | 1.35   | 1.45   | 0.053 | 0.057 |  |  |  |  |

| b                                           | 0.17   | 0.26   | 0.006 | 0.010 |  |  |  |  |

| С                                           | 0.117  | 0.177  | 0.005 | 0.007 |  |  |  |  |

| D                                           | 8.70   | 9.30   | 0.343 | 0.366 |  |  |  |  |

| D <sub>1</sub>                              | 6.90   | 7.10   | 0.270 | 0.280 |  |  |  |  |

| е                                           | 0.50   | TYP    | 0.020 | TYP   |  |  |  |  |

| L                                           | 0.45   | 0.75   | 0.018 | 0.030 |  |  |  |  |

| L <sub>1</sub>                              | 0.90   | 1.10   | 0.035 | 0.043 |  |  |  |  |

| Ø <b>1</b>                                  | 0°     | 7°     | 0°    | 7°    |  |  |  |  |

| ECN: S-40084—Rev. A, 02-Feb-04<br>DWG: 5928 |        |        |       |       |  |  |  |  |

<sup>\*</sup> For reference only

www.vishay.com 29-Jan-04

## **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Vishay products are not designed for use in life-saving or life-sustaining applications or any application in which the failure of the Vishay product could result in personal injury or death unless specifically qualified in writing by Vishay. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.