VISHAY SEMICONDUCTORS

www.vishay.com

### Infrared Data Transceiver Modules

**Application Note**

# **Reference Layouts and Circuit Diagrams**

By Sebastian Schaefer

### **IrDA TRANSCEIVER TYPES**

The Vishay portfolio of IrDA transceivers comprises five different packages of varying sizes and with different pinning (please see Table 1). Common to all transceivers are the basic pins V<sub>CC2</sub> / IRED anode (IRED supply voltage), TXD (emitter input signal), RXD (receiver output signal), SD (shutdown), V<sub>CC1</sub> (supply voltage), and GND. The smallest part, TFBS4711, contains only these six pins. In addition to that, three models offer the possibility to contact the IRED cathode pin for adding external emitters or using the IRED with custom IR codes. For more details, please see the below sections "Remote Control Function" and "Adding External Emitters".

| TABLE 1 - VISHAY IrDA-TRANSCEIVER PINOUT AND FOOTPRINT |                               |                               |                               |                               |                               |  |  |  |

|--------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|--|--|--|

| SIR 115.2 KBIT/S                                       |                               |                               |                               |                               |                               |  |  |  |

| PINOUT                                                 | TFDU4101                      | TFDU4301                      | TFBS4711                      | TFBS4652                      | TFBS4650                      |  |  |  |

| Package                                                |                               | THE REAL                      |                               |                               |                               |  |  |  |

| Technology                                             | Leadframe                     |                               | РСВ                           |                               |                               |  |  |  |

| Size (mm)                                              | 9.7 x 4.7 x 4.0               | 8.5 x 3.1 x 2.5               | 6.0 x 3.1 x 1.9               | 6.8 x 2.8 x 1.6               | 6.8 x 2.8 x 1.6               |  |  |  |

| 1                                                      | V <sub>CC2</sub> / IRED anode |  |  |  |

| 2                                                      | IRED cathode                  | IRED cathode                  | TXD                           | TXD                           | IRED cathode                  |  |  |  |

| 3                                                      | TXD                           | TXD                           | RXD                           | RXD                           | TXD                           |  |  |  |

| 4                                                      | RXD                           | RXD                           | SD                            | SD                            | RXD                           |  |  |  |

| 5                                                      | SD                            | SD                            | V <sub>CC1</sub>              | V <sub>logic</sub>            | SD                            |  |  |  |

| 6                                                      | V <sub>CC1</sub>              | V <sub>CC1</sub>              | GND                           | V <sub>CC1</sub>              | V <sub>CC1</sub>              |  |  |  |

| 7                                                      | NC                            | NC                            | -                             | GND                           | GND                           |  |  |  |

| 8                                                      | GND                           | GND                           | -                             | -                             | -                             |  |  |  |

| Pin spacing                                            | 1                             | 0.95                          | 0.95                          | 0.95                          | 0.95                          |  |  |  |

The TFBS4652 is the only model where the logic level of TXD, RXD, and SD can be tuned separately from the supply voltage V<sub>CC1</sub> or the IRED anode level.

≻

Revision: 04-Feb-2025

Document Number: 82610

1 For technical questions within your region: irdasupportAM@vishav.com, irdasupportAP@vishay .com, irdasupportEU@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

## **Reference Layouts and Circuit Diagrams**

#### THE RECOMMENDED APPLICATION CIRCUIT

When using a clean power supply and short wiring, Vishay IrDA transceivers can be operated without the need of any additional components. Nevertheless, in most applications the power supply line is influenced by other electrical consumers on the board and might get noisy. Furthermore, the short 2 µs pulses used in IrDA communication require high peak currents in a sufficiently short time, which some power sources might not be able to supply.

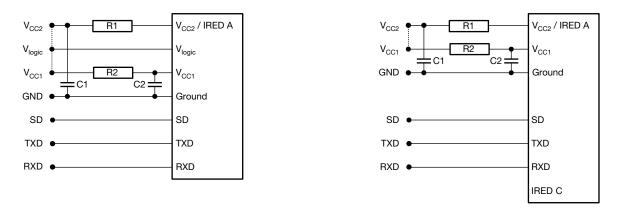

Fig. 1 - Recommended Application Circuit for TFBS4652 (Left) and all Other Transceivers (Right)

For these reasons we recommend the application circuit shown in Fig. 1. The left figure shows the circuit for the TFBS4652 with a  $V_{\text{logic}}$  pin, whereas the right figure illustrates how to connect transceivers with an IRED cathode pin (TFBS4650, TFDU4101, and TFDU4301). The TFDU4711 has only six pins and can be connected as shown in the right figure, neglecting the IRED cathode pin. The capacitance C1 is used to buffer the IRED supply voltage  $V_{CC2}$  and to compensate the inductance of the supply line. It should be fast enough to source the short IRED current pulses and could be, for example, a tantalum capacitor. To generate steep signal flanks, the use of an additional small ceramic capacitor in parallel to C1 could be taken into consideration.

The combination of C2 and R2 forms a low pass filter for smoothing and stabilizing the supply voltage at the  $V_{CC1}$  pin. For C2, a ceramic capacitor can be chosen. If the  $V_{CC1}$  and the IRED anode ( $V_{CC2}$ ) pins are connected to the same power supply line, the pulsed IRED current might lead to a voltage instability on the  $V_{CC1}$  pin. In this case, C1 and C2 both will help to stabilize the voltage at the  $V_{CC1}$  pin. The shutdown input must be grounded for normal operation, even when the shutdown function is not used.

The placement of these parts should be as near as possible to the transceiver. All stabilization and filter capacitors should be located < 10 mm from module pins, with short, large, direct ground paths. In general, the layout of a PCB can also have quite a big influence on parameters, especially on rise and fall times and on jitter.

Document Number: 82610 🔳

# **Reference Layouts and Circuit Diagrams**

### THE EMITTER FORWARD CURRENT AND INTENSITY (THE V<sub>CC2</sub> PIN)

R1 limits the IRED forward current if the full link distance given in the datasheet is not required. R1 is not strictly necessary, since the transceiver circuit contains an internal IRED current control, which limits the current to approximately 350 mA if R1 = 0  $\Omega$  (5.5 V).

| TABLE 2 - RECOMMENDED APPLICATION CIRCUIT COMPONENTS |                                   |  |  |  |  |

|------------------------------------------------------|-----------------------------------|--|--|--|--|

| COMPONENT                                            | RECOMMENDED VALUE                 |  |  |  |  |

| C1                                                   | 4.7 μF                            |  |  |  |  |

| C2                                                   | 0.1 µF, ceramic                   |  |  |  |  |

| R1                                                   | Depends on current to be adjusted |  |  |  |  |

| R2                                                   | 47 Ω                              |  |  |  |  |

There are several possible reasons why a series resistor R1 could be useful in an application. The reduction of the power dissipation could be one of these reasons if the application is exposed to high ambient temperatures.

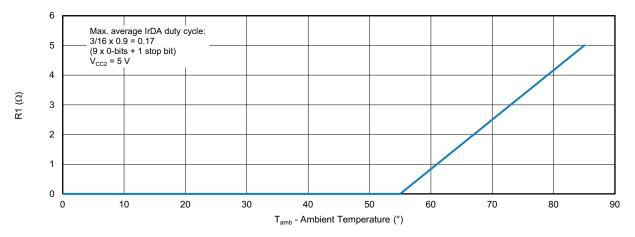

Fig. 2 - R1 vs. Maximum Operating Temperature

If the transceiver is used without the current limiting resistor R1, the ambient temperature range should be considerably smaller than given in the datasheet. The required resistance R1 for the maximum ambient temperature expected in the application is shown in Fig. 2 for  $V_{CC2} = 5$  V. For  $V_{CC2} = 3.3$  V or below, R1 = 0  $\Omega$  can be used for the whole operating temperature range.

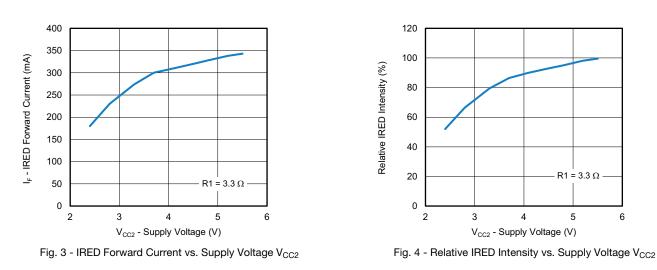

Another reason for the use of R1 is power saving. For example, in battery-powered devices a low current consumption could be preferred over a large link distance. In some cases, a reduced link distance might also be desired to avoid interception. Due to the internal current control, the IRED forward current and intensity shows only a week dependence on the supply voltage  $V_{CC2}$ . Both characteristics can be seen in Fig. 3 and Fig. 4 for R1 = 3.3  $\Omega$ .

Document Number: 82610

**Vishay Semiconductors**

The DNA of tech.

**Reference Layouts and Circuit Diagrams**

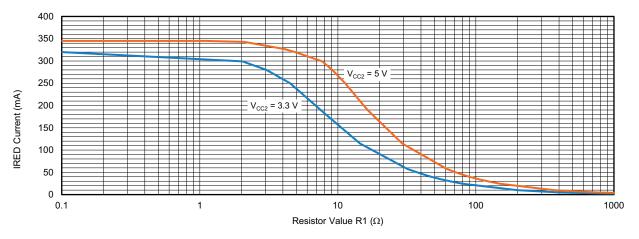

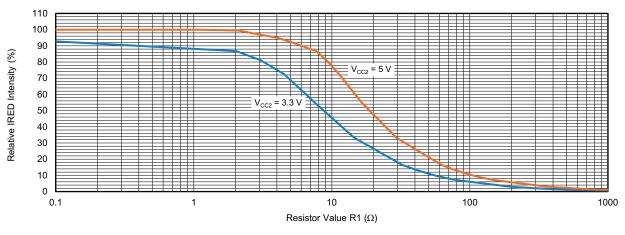

The effect of using different resistor values for R1 is illustrated in Fig. 5 for two typical supply voltages.

Fig. 5 - IRED Forward Current vs. R1

The resulting IRED intensity vs. R1 is given in Fig. 6. Relative values are shown here since the absolute intensity varies with the transceiver package type due to different lens shapes and sizes among the different modules. The 100 % intensity value can be found in the optoelectronic characteristics table of the corresponding transceiver datasheet.

**Vishay Semiconductors**

The DNA of tech.

Fig. 6 - Relative IRED Intensity vs. R1

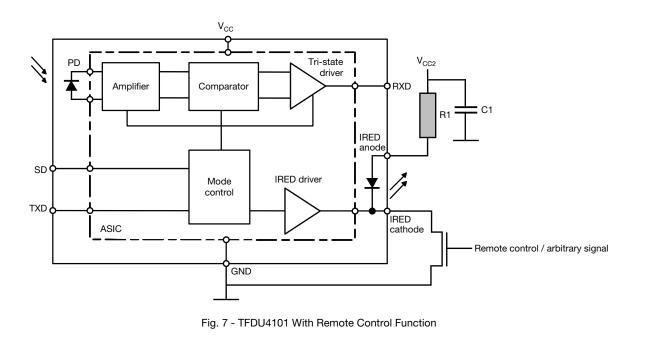

### **REMOTE CONTROL FUNCTION (THE CATHODE PIN)**

The IRED cathode pin extends the functionality of the transceiver in two different ways. Connecting this pin to GND via an external transistor as shown in Fig. 7 allows the transceiver IRED to be used with any desired signal shape; for example, remote control codes. In this circuit R1 is strictly necessary to avoid any damage to the IRED, since the IRED driver is short wired and cannot limit the forward current.

## **Reference Layouts and Circuit Diagrams**

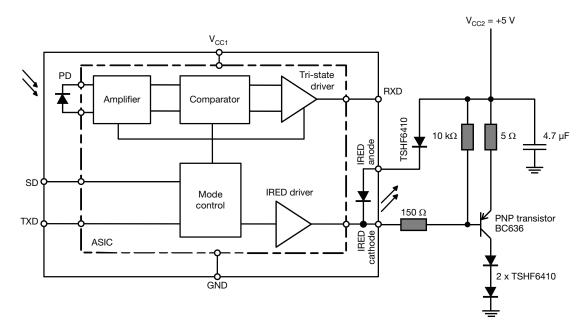

### ADDING EXTERNAL EMITTERS (THE CATHODE PIN)

The cathode pin can also be used to connect external emitters for achieving larger link distances. There are several ways to connect an external emitter to the transceiver, two of them are shown in Fig. 8. One way is to connect the emitter to the IRED anode pin. In this case both IREDs, the internal and the external one, are connected in series to the IRED driver.

Fig. 8 - TFDU4101 With Three External Emitters

In this connection the supply voltage should be large enough to source the sum of the forward voltages of both IREDs.

A second approach is to use the internal IRED driver to control an external transistor circuit. This type of circuit facilitates the connection of several external IREDs. The example in Fig. 8 illustrates how three external transmitters can be connected to a TFDU4101 by using both connection methods in parallel. The advantage of this configuration is that the intensity of the three external transmitters adds up to the internal emitter, which is also active in this setup.

The choice of the emitter can be adapted to the requirements of the application. For maximum range, three narrow-angled TSHF6210s are recommended, where a typical range of approximately 10 m could be achieved. If a wide field of view with medium range (~5 m) is required, a good choice would be three wide-angled TSHF6410s. In each case, the preferred emitter should have a peak wavelength of 890 nm to match the peak sensitivity of the IrDA receiver.

Document Number: 82610

# **Reference Layouts and Circuit Diagrams**

#### THE EMITTER SIGNAL TIMING (THE TXD PIN)

If the TXD input pin is set active, the internal driver will turn on the IRED at a specified intensity according to the R1 setting (see previous sections). The maximum IRED on time is limited to approximately 50  $\mu$ s, which protects the emitter against wrong timing that could lead to excessive power dissipation and overheating. This limit allows the nominal pulse duration to be used for IrDA data rates down to 9.6 kbit/s, as shown in Table 3 below. 2.4 kbit/s can also be transmitted - not with the nominal 78.13  $\mu$ s, but with any shorter pulse durations; for example, 1.63  $\mu$ s.

| TABLE 3 - SIGNALING RATE AND PULSE DURATION SPECIFICATION |                    |                             |                           |                           |                           |  |  |

|-----------------------------------------------------------|--------------------|-----------------------------|---------------------------|---------------------------|---------------------------|--|--|

| SIGNALING RATE                                            | MODULATION         | RATE TOLERANCE<br>% OF RATE | PULSE DURATION<br>MINIMUM | PULSE DURATION<br>NOMINAL | PULSE DURATION<br>MAXIMAL |  |  |

| 2.4 kbit/s                                                | RZI <sup>(1)</sup> | ± 0.87                      | 1.41 µs                   | 78.13 µs                  | 88.55 µs                  |  |  |

| 9.6 kbit/s                                                | RZI <sup>(1)</sup> | ± 0.87                      | 1.41 µs                   | 19.53 µs                  | 22.13 µs                  |  |  |

| 19.2 kbit/s                                               | RZI <sup>(1)</sup> | ± 0.87                      | 1.41 µs                   | 9.77 µs                   | 11.07 µs                  |  |  |

| 38.4 kbit/s                                               | RZI <sup>(1)</sup> | ± 0.87                      | 1.41 µs                   | 4.88 µs                   | 5.96 µs                   |  |  |

| 57.6 kbit/s                                               | RZI <sup>(1)</sup> | ± 0.87                      | 1.41 μs                   | 3.26 µs                   | 4.34 µs                   |  |  |

| 115.2 kbit/s                                              | RZI <sup>(1)</sup> | ± 0.87                      | 1.41 µs                   | 1.63 µs                   | 2.23 µs                   |  |  |

#### Note

<sup>(1)</sup> RZI = return to zero inverted

In general, the IrDA communication protocol is limited to half duplex, which means that data transmission in both directions is possible, but not simultaneously. During signal emission the TXD channel connects electrically to the RXD channel. This phenomenon refers to the term echo-on as described in the datasheet, and is sometimes used for self-testing the IrDA modules in mass production. However, the echo signal should be ignored by the micro controller during real data communication; and since the receiver saturates during transmission, it is also necessary to include a latency time of > 150 µs after transmission before the receiver is ready for reception again. If this latency time is not included between sending and receiving messages, the receiver will be insensitive right after transmission and will eventually miss parts of the data stream.

**Reference Layouts and Circuit Diagrams**

### IrDA ENCODER / DECODER MODULES

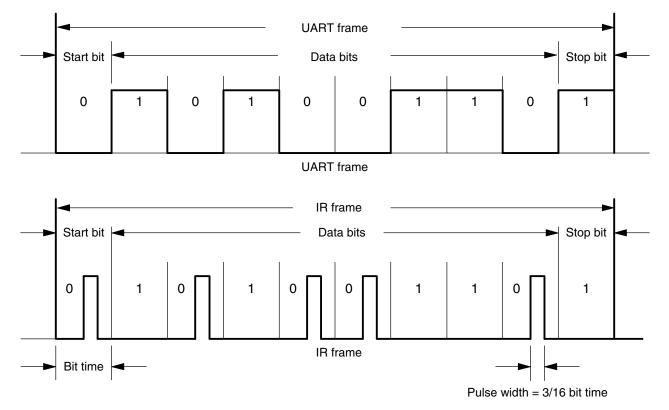

Data transmission with IrDA transceivers requires serial communication peripherals such as a UART interface in a computer or microcontroller. However, the IrDA transceiver cannot be connected directly to a UART interface since the corresponding bit length is not compatible with the short pulse timing limits of the transceiver. Hence, the UART data format needs to be converted into the IR short pulse format as shown in Fig. 9.

In this frame the UART bit length is typically shortened to 3/16 of its original duration (nominal pulse duration, as shown in Table 3). The format is "return to zero inverted" (RZI), where a pulse is transmitted for a 0-bit and no pulse for a 1-bit.

Fig. 9 - Conversion From the UART Frame Into the IR Frame

# **Reference Layouts and Circuit Diagrams**

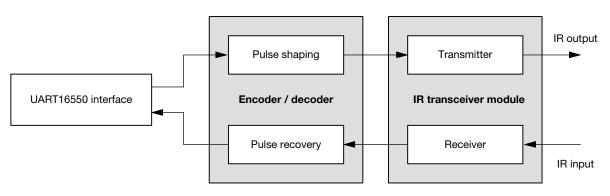

This conversion can be either performed in a microcontroller or by using an additional IrDA encoder / decoder module, which is connected between the UART interface and the IrDA transceiver on both sides of the data connection. An example of interfacing the IrDA transceiver with an encoder / decoder unit is shown in Fig. 10. Encoder / decoder modules are available, for example, from Texas Instruments (TIR1000) or Microchip (MCP2120/22).

Fig. 10 - Interfacing UART With Encoder / Decoder Modules

### THE RECEIVER OUTPUT SIGNAL (THE RXD PIN)

The RXD output pin is active low. It turns from the high state (inactive) to the low state (active) if an optical signal is detected by the receiver. Similar to the pulse width limit of the TXD pin, the RXD channel is also limited to AC signals and cannot detect DC radiation. The output pulse is always approximately 2.2  $\mu$ s long, regardless of the incoming pulse width. Vishay transceivers use tri-state outputs. When the device is set to the shutdown mode, the output is floating with a small load (in the order of 500 k $\Omega$  to 1 M $\Omega$ ) to the digital supply voltage V<sub>logic</sub>, if available, or V<sub>CC1</sub>. In general, carrier-based remote control signals (as RC5<sup>®</sup>, RC6<sup>®</sup>, or NEC<sup>®</sup> codes) can be received and used especially for a teach mode for learning RC codes.

### THE SHUTDOWN FUNCTION (THE SD PIN)

If the SD pin is set active (high), the transceiver goes into shutdown mode. In the shutdown mode the current consumption is reduced to about 10 nA, and the transmitter is turned off and will not send any signal, even if there is an input signal at the TXD pin. Please, note that the TXD-pin and the SD-pin should not be switched from the low to the high state simultaneously. A short delay time of > 1  $\mu$ s should be inserted when SD is activated before TXD. When TXD is activated first, the SD-pin should follow at least 50  $\mu$ s later. Furthermore, the RXD pin is not able to receive a signal during shutdown. The RXD output is weakly pulled to V<sub>logic</sub> if available, or to V<sub>CC1</sub> in the absence of a V<sub>logic</sub> pin. The shutdown input must be grounded for normal operation, even when the shutdown function is not used.

### THE SUPPLY VOLTAGE (THE V<sub>CC1</sub> PIN)

In all Vishay transceivers, the supply voltages for the IRED ( $V_{CC2}$ ) and the transceiver ( $V_{CC1}$ ) can be applied separately. Since the transceiver requires only a very small operating current, the separated pins provide the possibility to connect only  $V_{CC1}$  to a regulated power supply, whereas the much higher IRED drive current can be supplied by an unregulated source, resulting in less cost for the power supply. The supply voltage should be filtered with a low pass, as shown in the circuit diagram in Fig. 1. Especially when EMI immunity is an issue, care should be taken for the RF quality of the ceramic capacitor.

Document Number: 82610 🔳

**Vishay Semiconductors**

#### The DNA of tech.

### **Reference Layouts and Circuit Diagrams**

#### LOGIC VOLTAGE LEVELS (THE V<sub>logic</sub> PIN)

The TFBS4652 provides the possibility to apply an external reference for the logic input and output levels. The  $V_{logic}$  pin can be either connected to  $V_{CC1}$  or can be separately supplied by a reference voltage to adapt input thresholds and output levels to the logic levels, especially when using different I/O voltages than the supply voltage  $V_{CC1}$ . The input threshold is about half of the applied  $V_{logic}$  level and the output swing is defined by  $V_{logic}$ .

#### THE GND PIN

This is the reference for all applied voltages. Switching times, delays, noise immunity, and even sensitivity can suffer from bad grounding.

#### **NON-IrDA APPLICATIONS**

The constriction to the IrDA standard limits the application of the transceivers outside the IrDA protocol. Due to the pulse duration limits of minimum and maximum optical pulse width, IrDA transceivers are designed to suppress low frequency and DC radiation, such as sunlight and incandescent or fluorescent lamps. Therefore, these transceivers cannot be used as DC radiation sensors. Also, presence or proximity sensing is not applicable with IrDA transceivers, the TXD channel is connected to the RXD channel during signal emission, which causes the receiver to echo the transmitter signal. Sending and receiving is thus not possible at the same time.

#### **OPTICAL WINDOWS**

Optical windows should be designed not to truncate the beam shape of transceivers. On the other hand, the window design also can be used to minimize interference with background light and other disturbances. For type-related window design and general information regarding window materials and suppliers, see the application note <u>Window Size in Housings</u> and visit our <u>Window Size Calculator</u>.