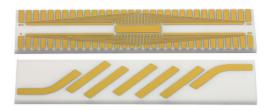

## **Custom Substrates - Conductor Pattern**

#### **FEATURES**

- Precision conductor patterns

- · Metalization on 1 or 2 surfaces

- Various substrate materials

- · Sputtered / plated metal systems

- Custom sizes from 0.020" x 0.020" to 4.000" x 4.000"

- Quick delivery available

#### **APPLICATIONS**

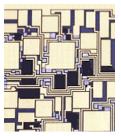

Vishay EFI custom specialty films / conductor patterned substrates are used in the hybrid circuit and microwave industries. These conductor patterns are precisely manufactured to be used for complex fan-outs, interconnects, high temperature, and RF / microwave designs. Vishay EFI custom specialty films / conductor patterned substrates can also be used in a wider variety of applications including jumpers, mounting pads, and bonding pads. The custom specialty film / conductor patterned substrates are manufactured using Vishay Electro-Films (EFI) sophisticated thin film equipment and manufacturing technology. The custom specialty film / conductor patterned substrates are visually inspected to MIL-STD-883, method 2032 class H or K.

## THIN FILM DESIGN GUIDELINES

Thin Film Design Guide for RF and UWave Substrates (www.vishay.com/doc?49109).

#### SUBSTRATE MATERIALS

For substrate materials and their properties, please reference datasheet: SPF1 (www.vishay.com/ppg?61105).

## **DEFINING A METAL SYSTEM**

Vishay EFI offers several different metals to meet the custom needs of our customers. Simple conductor circuits have the most flexibility with available metal systems. As the complexity and level of integration increase, the list of available metal system choices is limited to allow for tighter process control and manufacturability. The following table identifies the specific function of the available metals as well as their available thickness ranges.

| AVAILABLE METALS AND THEIR FUNCTIONS |                         |                                       |                                 |  |

|--------------------------------------|-------------------------|---------------------------------------|---------------------------------|--|

| LAYER TYPE                           | METAL                   | RANGE OF VALUES                       | COMMENTS                        |  |

| A all a set a se                     | Titanium tungsten (TiW) | 500 Å to 1250 Å                       | Ideal for high temperatures     |  |

| Adhesion                             | Chromium (Cr)           | 500 Å to 1250 Å                       | Ideal for low temperatures      |  |

| Downier                              | Nickel (Ni)             | 1250 Å to 1750 Å                      | Sputtered barrier               |  |

| Barrier                              | Palladium (Pd)          | 1500 Å to 2500 Å                      | High temperature solder barrier |  |

| Conductor                            | Gold (Au)               | 10 μ" to 200 μ"<br>(0.25 μm to 5 μm)  | -                               |  |

|                                      | Copper (Cu)             | 20 μ" to 200 μ"<br>(0.05 μm to 5 μm)  | -                               |  |

|                                      | Aluminum (Al)           | 50 μ" to 120 μ"<br>(1.27 μm to 5 μm)  | Aluminum wire bond              |  |

| High Current Conductor               | Gold (Au)               | 200 μ" to 1000 μ"<br>(5 μm to 25 μm)  | Gold wire bond                  |  |

|                                      | Copper (Cu)             | 200 μ" to 4000 μ"<br>(5 μm to 100 μm) | High temperature / conductivity |  |

## Note

TaN and NiCr are available as adhesion metal layers under certain metal stacks. Call factory for details

## Vishay Electro-Films

## **APPLICATION OF METAL SYSTEMS**

A metal system should be selected based upon electrical, thermal, and mechanical performance demands as well as the assembly process requirements. Assembly requirements might include pads suitable for eutectic (solder) bonding and / or wire bonding.

Soldering pads should include a barrier layer designed to control the solubility of the pad metallization with the solder being applied. A nickel or palladium barrier layer is typically deposited under gold soldering pads to ensure reliable device attachment due to gold's high solubility in solders.

All of the standard metal systems offered by Vishay EFI are readily bonded using gold wire. For optimal bond integrity, a minimum of 100  $\mu$ " (2.5  $\mu$ m) gold thickness is recommended, although reasonable bonding results can be achieved with gold as thin as 50  $\mu$ " (1.2  $\mu$ m).

Intermetallic formation and barrier metal migration are influenced by film exposure to high temperatures. For this reason, it is important to select a metal system that can withstand the temperature profile requirements of the application. The following table provides a matrix of standard metal systems and assembly options.

| STANDARD METAL SYSTEMS AND ASSEMBLY OPTIONS |                            |               |                       |              |

|---------------------------------------------|----------------------------|---------------|-----------------------|--------------|

| METAL SYSTEM                                | MAX. REFLOW<br>TEMPERATURE | WIRE-BONDABLE | SOLDER TYPE           |              |

|                                             |                            | GOLD          | LEAD / LEAD (Pb)-FREE | GOLD BEARING |

| Cr / Cu / Ni / Au                           | 350                        | Yes           | Preferred             | Yes          |

| NiCr / TiW / Au                             | 400                        | Yes           | -                     | Yes          |

| NiCr / Ni / Au                              | 350                        | Yes           | Preferred             | Yes          |

| NiCr / TiW / Au / Ni / Au                   | 350                        | Yes           | Preferred             | Yes          |

| TiW / Au                                    | 450                        | Yes           | -                     | Yes          |

| TiW / Ni / Au                               | 350                        | Yes           | Preferred             | Yes          |

| TiW / Au / Ni / Au                          | 350                        | Yes           | Preferred             | Yes          |

| TiW / Pd / Au                               | 450                        | Yes           | Yes                   | Preferred    |

| TiW / Au / Cu / Ni / Au                     | 350                        | Yes           | Preferred             | Yes          |

| TaN / TiW / Au                              | 450                        | Yes           | -                     | Yes          |

| TaN / TiW / Ni / Au                         | 350                        | Yes           | Preferred             | Yes          |

| TaN / TiW / Au / Ni / Au                    | 350                        | Yes           | Preferred             | Yes          |

| TaN / TiW / Pd / Au                         | 450                        | Yes           | Yes                   | Preferred    |

| TaN / TiW / Au / Cu / Ni / Au               | 350                        | Yes           | Preferred             | Yes          |

Additional metal system capabilities are available. These options are subject to review by the Vishay EFI engineering and production teams. Consideration will be given to special requests, with a focus on manufacturability and reliability.

## **INCORPORATING HIGH CONDUCTIVITY TRACES**

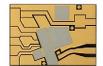

Vishay EFI's capability to deposit thick conductor traces has enabled design approaches that allow high current, low resistance circuit traces to co-exist with microwave structures and transmission lines. For circuit traces carrying high currents over long distances, the resistive losses of thin film conductor lines can become significant. By selectively increasing the thickness of high-current lines, the engineer can have fine line RF structures on the same circuit with low-loss DC lines. Additionally, these low-resistance traces can be used to manage thermal loads within RF circuits.

Typically, the design engineer will calculate the trace resistance ( $R_{total}$ ) of a structure during the design process. The trace resistance is defined as:

$R_{\text{total}}$  = (trace length / trace width) x conductor sheet resistance

$R_{\text{total}} = (L / W) \times R_{\text{sheet}}.$

The sheet resistance ( $R_{\rm sheet}$ ) is derived by dividing the bulk resistivity by the conductor thickness. Therefore, the thicker one can deposit the conductor, the lower the overall sheet resistance. The following two tables detail the bulk resistivity and the typical sheet resistance of some common thin film metals at a variety of deposition thicknesses.

# Vishay Electro-Films

| SELECTED BULK RESISTIVITY |                                                                 |                                                               |  |  |

|---------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|--|--|

| MATERIAL                  | THEORETICAL BULK RESISTIVITY $\mu\Omega\mathbf{x}\;\mathbf{cm}$ | CONSERVATIVE VALUE OF BULK RESISTIVITY WHEN DEPOSITED μΩ x cm |  |  |

| Gold (Au)                 | 2.2                                                             | 2.4 (sputtered) / 2.9 (plated)                                |  |  |

| Titanium Tungsten (TiW)   | -                                                               | 45 (sputtered)                                                |  |  |

| Copper (Cu)               | 1.71                                                            | 2 (sputtered) / 4 (plated)                                    |  |  |

| Nickel (Ni)               | 7                                                               | 8.2 (sputtered)                                               |  |  |

| Aluminum (Al)             | 2.7                                                             | 3 (sputtered)                                                 |  |  |

| SELECTED APPROXIMATE SHEET RESISTIVITIES |                      |                                   |  |

|------------------------------------------|----------------------|-----------------------------------|--|

| METAL                                    | THICKNESS<br>µ" (µm) | PLATED SHEET RESISTIVITY (mΩ /sq) |  |

| Gold (Au)                                | 80 (2)               | 14.5                              |  |

| Gold (Au)                                | 160 (4)              | 7.25                              |  |

| Gold (Au)                                | 400 (10)             | 2.9                               |  |

| Copper (Cu)                              | 1000 (25)            | 0.42                              |  |

| Copper (Cu)                              | 2000 (50)            | 0.21                              |  |

| Nickel (Ni)                              | 200 (5)              | 160 (sputtered)                   |  |

| Aluminum (Al)                            | 40 (1)               | 30 (sputtered)                    |  |

In summary, gold (Au) and copper (Cu) can be deposited at much greater thicknesses than standard thin films to reduce overall conductor resistance. Gold (Au) can be deposited up to a maximum thickness of 400  $\mu$ ", while copper (Cu) can be plated routinely at thicknesses up to 4000  $\mu$ " (100  $\mu$ m). It is important to note that minimum line widths and spaces increase with film thickness. See the following for a summary of line widths and spaces as associated with conductor thickness.

## PATTERNING LINES AND SPACES

Thin film patterning tolerances are influenced by several factors in the photomasking process. Pattern tolerancing for plating and etching processes vary based on the metal thickness as shown in the tables below. As the thickness of the metal increases, the photoresist used for this process changes and the metal thickness tolerances and line and space patterning must be adjusted to compensate for this. As these decisions are made the surface finish of the substrate must also be factored as the polished surface finish will deliver the smoothest surface and therefore the best line and space pattern. For the substrate materials where As fired and lapped options are available these surfaces will not hold the same tolerances and minimum sizes that the polished surface will.

| PLATED METAL PATTERNS         |                                |                                     |                                    |  |

|-------------------------------|--------------------------------|-------------------------------------|------------------------------------|--|

| TOTAL MAX. METAL<br>THICKNESS | BEST PATTERN TOLERANCE PROCESS | BEST PLATING THICKNESS<br>TOLERANCE | SMALLEST PATTERN<br>LINE AND SPACE |  |

| 100 μ" (2.54 μm)              | ± 0.1 mil                      | ± 30 μ"                             | 0.5 mil / 0.5 mil                  |  |

| 150 μ" (3.8 μm)               | ± 0.15 mil                     | ± 40 μ"                             | 0.5 mil / 0.5 mil                  |  |

| 250 μ" (6.35 μm)              | ± 0.2 mil                      | ± 50 μ"                             | 0.5 mil / 0.5 mil                  |  |

| 400 μ" (10.2 μm)              | ± 0.2 mil                      | ± 100 μ"                            | 0.5 mil / 0.5 mil                  |  |

| 800 μ" (20.3 μm)              | 0.3 mil±                       | ± 150 μ"                            | 1 mil / 1 mil                      |  |

| 1000 μ" (25.4 μm)             | ± 1.0 mil                      | ± 250 μ"                            | 2 mil / 2 mil                      |  |

| 2000 μ" (51 μm)               | ± 2.0 mil                      | ± 500 μ"                            | 3 mil / 3 mil                      |  |

| 4000 μ" (102 μm)              | ± 3.0 mil                      | ± 1 mil                             | 5 mil / 5 mil                      |  |

## www.vishay.com

## Vishay Electro-Films

| ETCHED METAL PATTERNS      |                                      |                                      |                                    |                  |

|----------------------------|--------------------------------------|--------------------------------------|------------------------------------|------------------|

| TOTAL MAX. METAL THICKNESS | BEST PATTERN<br>TOLERANCE<br>PROCESS | BEST METAL<br>THICKNESS<br>TOLERANCE | SMALLEST PATTERN<br>LINE AND SPACE | METAL DEPOSITION |

| 100 μ" (2.54 μm)           | ± 0.1 mil                            | Ref. plating table                   | 1 mil / 1 mil                      | Plated           |

| 150 μ" (3.8 μm)            | ± 0.2 mil                            | Ref. plating table                   | 1.5 mil / 1.5 mil                  | Plated           |

| 200 μ" (5.1 μm)            | ± 0.3 mil                            | Ref. plating table                   | 2 mil / 2 mil                      | Plated           |

| 300 μ" (7.6 μm)            | ± 0.5 mil                            | Ref. plating table                   | 2 mil / 2 mil                      | Plated           |

| 12 000 Å                   | ± 0.5 mil                            | ±10 %                                | 1.5 mil / 2 mil                    | Sputtered        |

| 25 000 Å                   | ± 1.0 mil                            | ±10 %                                | 2 mil / 2 mil                      | Sputtered        |

#### **AuSn APPLICATIONS**

Vishay EFI offers the option of a sputter deposition of gold-tin solder with wt % of 80 / 20 while maintaining tolerances tighter than ± 2 % wt and control of film thickness to ± 1.0 µm. This capability allows deposition of customer AuSn patterns that can be used to fine-tune assembly processes to meet the most demanding requirements; the tight composition tolerance eliminates the need to adjust reflow process parameters to compensate for variations in solder composition. The gold-tin deposition process allows films with thickness ranging between 4.5 um and 7 um with a tolerance of  $\pm$  1.0  $\mu$ m. Common applications for AuSn deposition are laser diode sub-mounts, fiber optic pump lasers, optical transmitters, optical receivers, optical transceivers and optical TOSA / ROSA packages. For further detail, please reference document: AuSn design guideline (www.vishay.com/doc?49248).

When designing hybrid assemblies to operate at temperatures above 125 °C it becomes important to provide monometallic interconnects to prevent intermetallic diffusion and resultant long term reliability problems. For these situations, Vishay Electro-Films (EFI) has developed processes for depositing both aluminum and gold bonding pads on the same substrate. This structure provides for monometallic interconnects. Aluminum wire can be used to connect from the aluminum pads on the substrate. Similarly, gold wire can be used to connect gold pads on the substrate to gold hermetic package terminals. Appropriate barrier metals are included in substrate processing to provide long term reliability in high temperature applications.

High temperature - Au and Al wirebond pads

# Vishay Electro-Films

## SUBSTRATE SINGULATION

Vishay Electro-Films uses standard semiconductor / ceramic dicing equipment and processes to singulate production boards into individual pieces. These processes depend on tight alignment and inspection to maintain overall part dimension tolerances and metal pattern to part edge tolerances. Each of these dimensions and their tolerances are measured on each lot that is processed.

| SUBSTRATE SINGULATION                   |                                      |                                  |                                                        |

|-----------------------------------------|--------------------------------------|----------------------------------|--------------------------------------------------------|

| DIMENSION                               | DIMENSION MEASUREMENT in inches (mm) | MINIMUM TOLERANCE in inches (mm) | Nominal ± 0.002"                                       |

| Metal pattern pullback from edge of die | 0.002 (0.0508)                       | ± 0.002 (± 0.0508)               | Back pattern                                           |

| Overall part dimension                  | n/a                                  | ± 0.002 (± 0.0508)               | <u> </u>                                               |

| Front to back pattern tolerance         | n/a                                  | ± 0.002 (± 0.0508)               | Front to back pattern registration ± 0.002" (0.051 mm) |

# CONTACT INFORMATION For design assistance, contact: efi@vishay.com

## **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.